IDT71B74 View Datasheet(PDF) - Integrated Device Technology

Part Name

Description

Manufacturer

IDT71B74 Datasheet PDF : 9 Pages

| |||

IDT71B74

BiCMOS STATIC RAM 64K (8K x 8-BIT) CACHE-TAG RAM

COMMERCIAL TEMPERATURE RANGE

7

•

6

∆TADM

(Typical, ns) 5

4

3

2

•

1 •••

•

•

8 20 40 60 80 100 120 140 160 180 200

CAPACITANCE (pF)

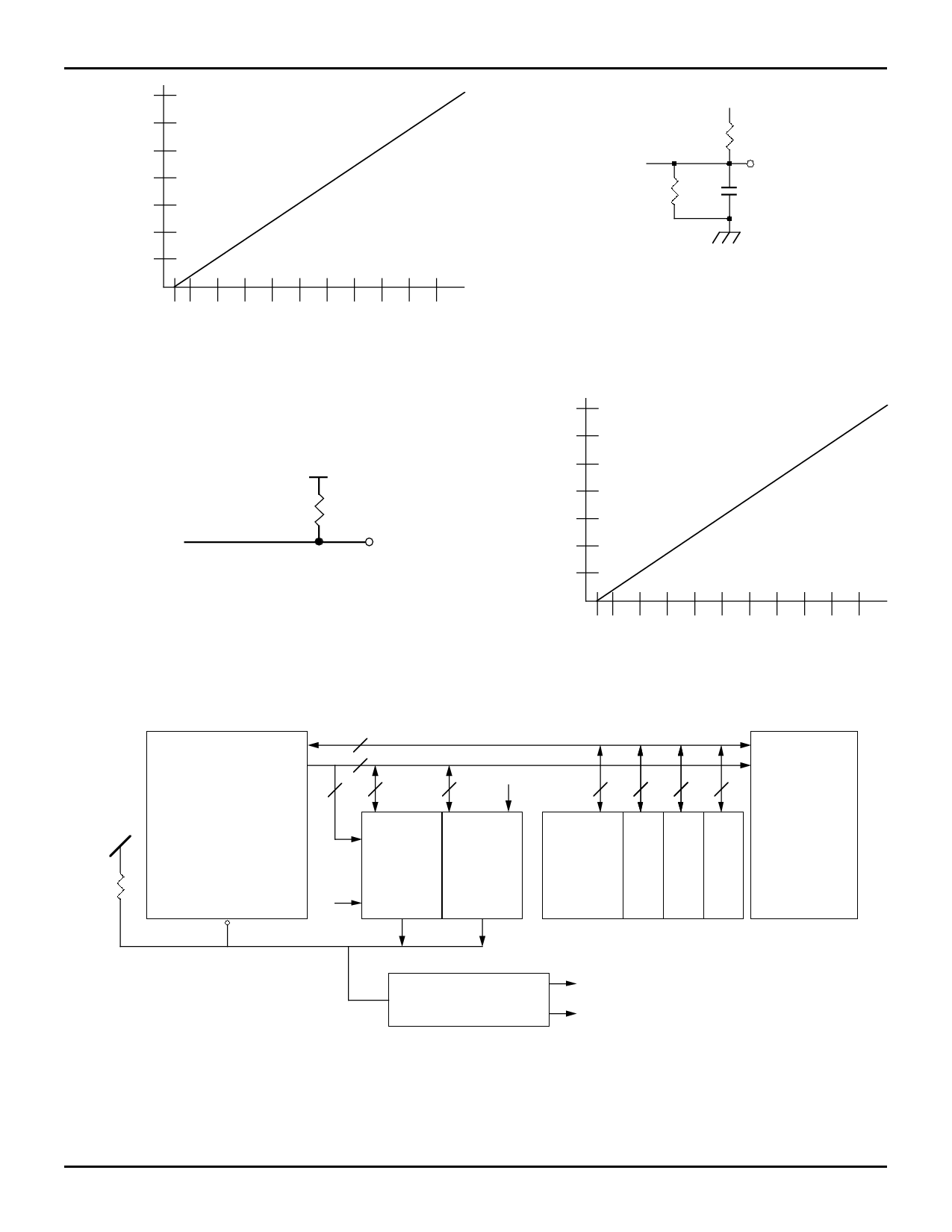

Figure 1A. Lumped Capacitive Load

Typical Derating Curve

3013 drw 04

MATCH

5V

RL

RL = 200Ω (COM’L.)

= 270Ω (MIL.)

3013 drw 06

Figure 3. AC Test Load for MATCH

DATAOUT

255Ω

5V

480Ω

5pF*

3013 drw 05

*Includes scope and jig.

Figure 2. AC Test Load

(for tCLZ, tOLZ, tCHZ, tOHZ, tOW, tWHZ)

7

•

6

∆TAA

(Typical,

ns)

5

4

3

2

•

1 •••

•

•

8 20 40 60 80 100 120 140 160 180 200

CAPACITANCE (pF)

Figure 3A. Lumped Capacitive Load

Typical Derating Curve

3013 drw 07

5V

R L(2)

DATA

32

D0-D31

ADDR

32

13

8

A0-A31

7

LOGIC 1

A17-A24

A25-A31

8

98

98

8

80486

32-BIT

MICROPROCESSOR

A4-A16

IDT71B74

CACHE-

TAG

RAM

IDT71B74

CACHE-

TAG

RAM

IDT71256 256 256 256

CACHE-

DATA

RAM

RDY

CLEAR

MATCH

MATCH

DATA

ADDR

MAIN

MEMORY

MEMORY READ/WRITE

CONTROL LOGIC

CACHE READ/WRITE

MAIN MEMORY READ/WRITE

3013 drw 08

NOTES:

1. For more information refer to IDT Application Notes AN-07 and AN-78 and Technical Notes TN-11 and TN-13.

2. RL = 200Ω.

Figure 4. Example of Cache Memory System Block Diagram

14.1

4