UPD75212ACW View Datasheet(PDF) - NEC => Renesas Technology

Part Name

Description

Manufacturer

UPD75212ACW Datasheet PDF : 70 Pages

| |||

µPD75212A

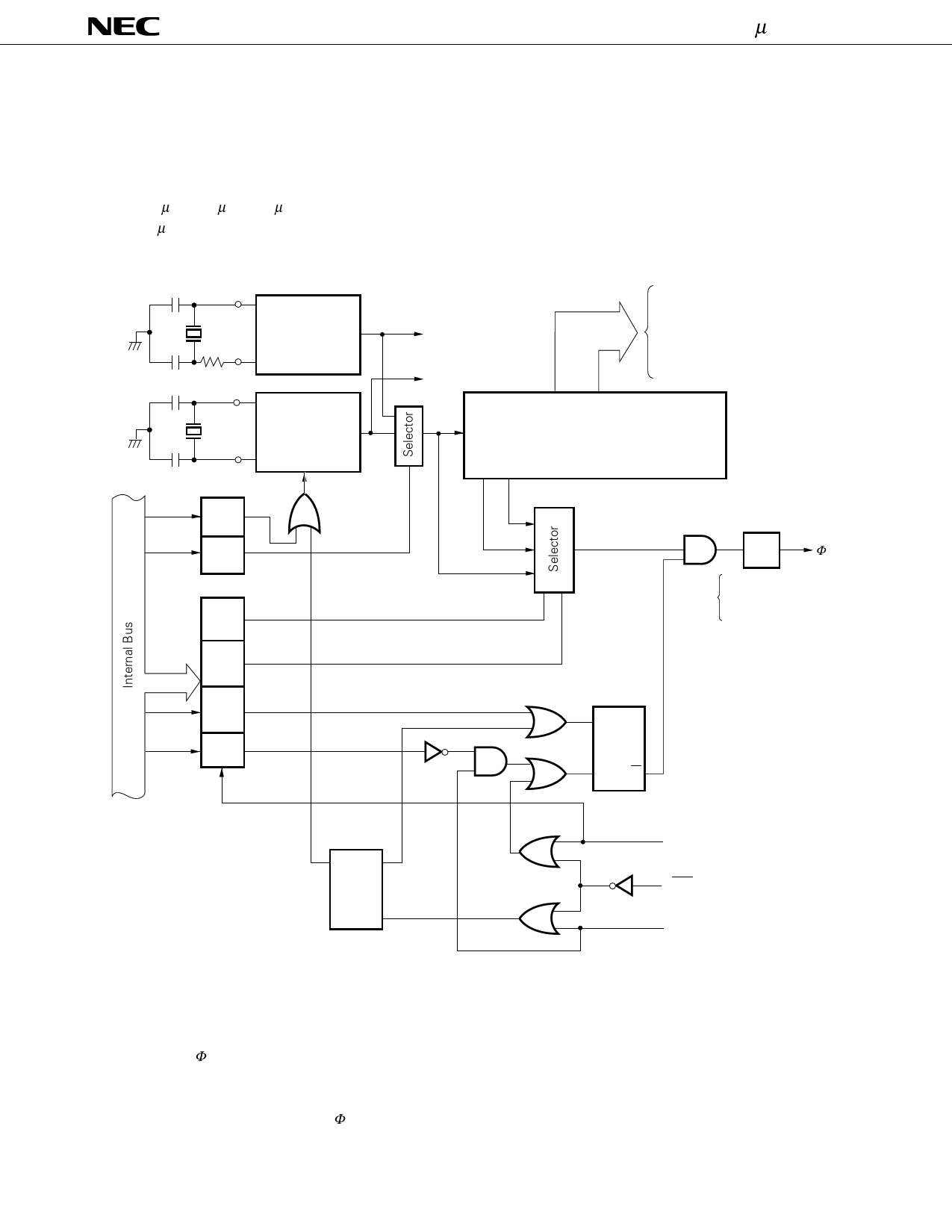

5.2 CLOCK GENERATOR

The clock generator operations are determined by the processor clock control register (PCC) and the system clock

control register (SCC).

The clock generator has two types: main system clock and subsystem clock.

The instruction execution time can be changed.

• 0.95 µs, 1.91 µs, 15.3 µs (Main system clock: at 4.19 MHz operation)

• 122 µs (Subsystem clock: at 32.768 kHz operation)

XT1

XT2

X1

X2

SCC

SCC3

SCC0

PCC

PCC0

Fig. 5-1 Clock Generator Block Diagram

Subsystem fXT

Clock

Oscillator

Main System

Clock

Oscillator

fX

Oscillation

Stop

Watch Timer

Timer/Pulse

Generator

fXX

1/2 1/6

• FIP Controller

• Basic Interval Timer (BT)

• Timer/Event Counter

• Serial Interface

• Watch Timer

• INT0 Noise Eliminator

1/8~1/4096

Frequency Divider

Frequency

Divider

1/4

Φ

• CPU

• INT0 Noise Eliminator

• INT1 Noise Eliminator

PCC1

4

PCC2

HALT*

PCC3

STOP*

HALT F/F

S

RQ

PCC2 and

PCC3

Clear

* Instruction execution

STOP F/F

QS

R

Wait Release Signal from BT

RES Signal (Internal Reset)

Standby Release Signal from

Interrupt Control Circuit

Remarks 1. fX = Main system clock frequency

2. fXT = Subsystem clock frequency

3. fXX = System clock frequency

4. Φ = CPU clock

5. PCC: Processor clock control register

6. SCC: System clock control register

7. 1 clock cycle (tCY) of Φ is 1 machine cycle of an instruction. For tCY, see ”AC Characteristics“ in 12.

ELECTRICAL SPECIFICATIONS.

18