April 1994 Revised October 2003

# 74VHC4046 CMOS Phase Lock Loop

### **General Description**

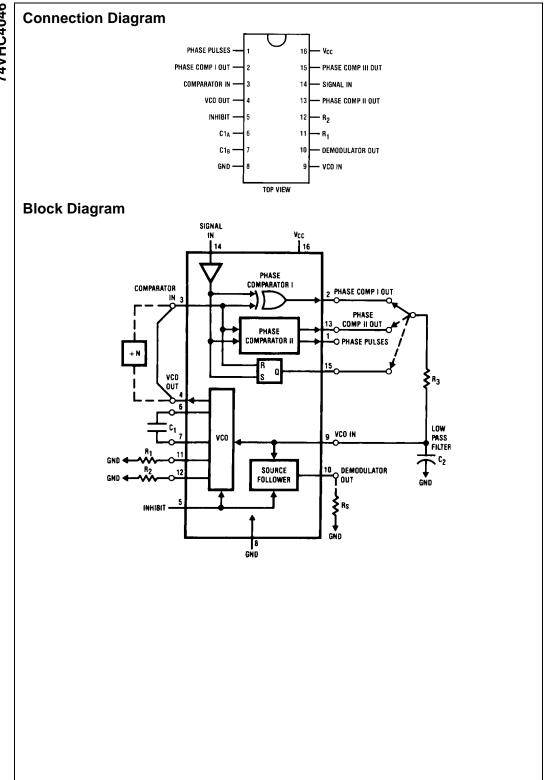

The VHC4046 is a low power phase lock loop utilizing advanced silicon-gate CMOS technology to obtain high frequency operation both in the phase comparator and VCO sections. This device contains a low power linear voltage controlled oscillator (VCO), a source follower, and three phase comparators. The three phase comparators have a common signal input and a common comparator input. The signal input has a self biasing amplifier allowing signals to be either capacitively coupled to the phase comparators with a small signal or directly coupled with standard input logic levels. This device is similar to the CD4046 except that the Zener diode of the metal gate CMOS device has been replaced with a third phase comparator.

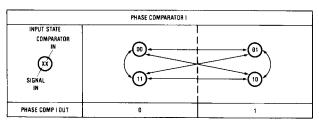

Phase Comparator I is an exclusive OR (XOR) gate. It provides a digital error signal that maintains a 90 phase shift between the VCO's center frequency and the input signal (50% duty cycle input waveforms). This phase detector is more susceptible to locking onto harmonics of the input frequency than phase comparator I, but provides better noise rejection.

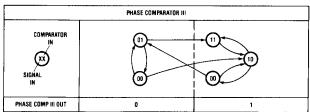

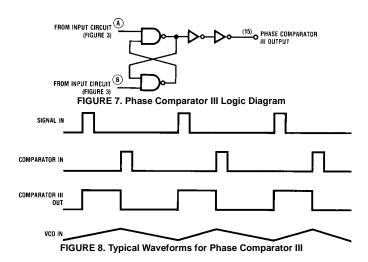

Phase comparator III is an SR flip-flop gate. It can be used to provide the phase comparator functions and is similar to the first comparator in performance.

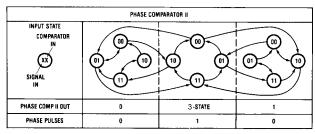

Phase comparator II is an edge sensitive digital sequential network. Two signal outputs are provided, a comparator output and a phase pulse output. The comparator output is a 3-STATE output that provides a signal that locks the VCO output signal to the input signal with 0 phase shift between them. This comparator is more susceptible to noise throw-

ing the loop out of lock, but is less likely to lock onto harmonics than the other two comparators.

In a typical application any one of the three comparators feed an external filter network which in turn feeds the VCO input. This input is a very high impedance CMOS input which also drives the source follower. The VCO's operating frequency is set by three external components connected to the C1 $_{\mbox{\scriptsize A}}$ , C1 $_{\mbox{\scriptsize B}}$ , R $_{\mbox{\scriptsize 1}}$  and R $_{\mbox{\scriptsize 2}}$  pins. An inhibit pin is provided to disable the VCO and the source follower, providing a method of putting the IC in a low power state.

The source follower is a MOS transistor whose gate is connected to the VCO input and whose drain connects the Demodulator output. This output normally is used by tying a resistor from pin 10 to ground, and provides a means of looking at the VCO input without loading down modifying the characteristics of the PLL filter.

#### **Features**

- Low dynamic power consumption: (V<sub>CC</sub> = 4.5V)

Maximum VCO operating frequency: 12 MHz

(V<sub>CC</sub> = 4.5V)

- Fast comparator response time (V<sub>CC</sub> = 4.5V)

Comparator II: 25 ns Comparator III: 30 ns Comparator III: 25 ns

- VCO has high linearity and high temperature stability

- Pin and function compatible with the 74HC4046

### **Ordering Code:**

| Order Number | Package Number | Package Description                                                          |

|--------------|----------------|------------------------------------------------------------------------------|

| 74VHC4046M   | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

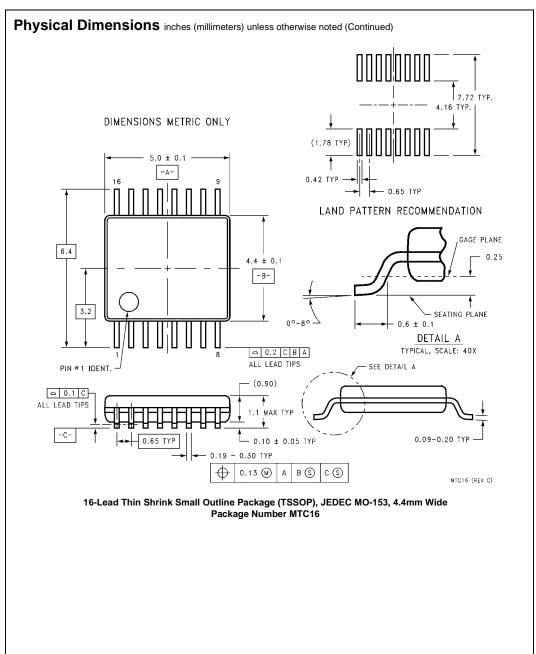

| 74VHC4046MTC | MTC16          | 16-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide  |

| 74VHC4046N   | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |

Surface mount packages are also available on Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

## Absolute Maximum Ratings(Note 1)

(Note 2)

| -0.5  to + 7.0 V          |

|---------------------------|

| $-1.5$ to $V_{CC}$ +1.5V  |

| $-0.5$ to $V_{CC} + 0.5V$ |

| ±20 mA                    |

| ±25 mA                    |

|                           |

| ±50 mA                    |

| −65°C +150°C              |

|                           |

| 600 mW                    |

| 500 mW                    |

|                           |

| 260°C                     |

|                           |

# Recommended Operating Conditions

|                    |                                     | Min | Max      | Units |

|--------------------|-------------------------------------|-----|----------|-------|

| Supply Volt        | age (V <sub>CC</sub> )              | 2   | 6        | V     |

| DC Input or        | Output Voltage                      | 0   | $V_{CC}$ | V     |

| $(V_{IN}, V_{OL})$ | <sub>JT</sub> )                     |     |          |       |

| Operating 1        | Temperature Range (T <sub>A</sub> ) | -40 | +85      | °C    |

| Input Rise         | or Fall Times                       |     |          |       |

| $(t_r, t_f)$       | $V_{CC} = 2.0V$                     |     | 1000     | ns    |

|                    | $V_{CC} = 4.5V$                     |     | 500      | ns    |

|                    | $V_{CC} = 6.0V$                     |     | 400      | ns    |

|                    |                                     |     |          |       |

$\ensuremath{\text{Note 1:}}\xspace$  Maximum Ratings are those values beyond which damage to the device may occur.

Note 2: Unless otherwise specified all voltages are referenced to ground.

Note 3: Power Dissipation temperature derating — plastic "N" package: –

12 mW/°C from 65°C to 85°C.

### DC Electrical Characteristics (Note 4)

| Symbol          | Parameter                          | Conditions                                | V <sub>CC</sub> | T <sub>A</sub> =25°C |       | T <sub>A</sub> =-40 to 85°C | V V V V V V V V V V V V V V V V V V V |

|-----------------|------------------------------------|-------------------------------------------|-----------------|----------------------|-------|-----------------------------|---------------------------------------|

| Зупівої         | Faranietei                         | Conditions                                | *cc             | Тур                  | Guara | inteed Limits               | Units                                 |

| V <sub>IH</sub> | Minimum HIGH Level                 |                                           | 2.0V            |                      | 1.5   | 1.5                         | V                                     |

|                 | Input Voltage                      |                                           | 4.5V            |                      | 3.15  | 3.15                        | V                                     |

|                 |                                    |                                           | 6.0V            |                      | 4.2   | 4.2                         | V                                     |

| V <sub>IL</sub> | Maximum LOW Level                  |                                           | 2.0V            |                      | 0.5   | 0.5                         | V                                     |

|                 | Input Voltage                      |                                           | 4.5V            |                      | 1.35  | 1.35                        | V                                     |

|                 |                                    |                                           | 6.0V            |                      | 1.8   | 1.8                         | V                                     |

| V <sub>OH</sub> | Minimum HIGH Level                 | $V_{IN} = V_{IH}$ or $V_{IL}$             | 2.0V            | 2.0                  | 1.9   | 1.9                         | V                                     |

|                 | Output Voltage                     | I <sub>OUT</sub>   ≤ 20 μA                | 4.5V            | 4.5                  | 4.4   | 4.4                         | V                                     |

|                 |                                    |                                           | 6.0V            | 6.0                  | 5.9   | 5.9                         | V                                     |

|                 |                                    | $V_{IN} = V_{IH}$ or $V_{IL}$             |                 |                      |       |                             |                                       |

|                 |                                    | I <sub>OUT</sub>   ≤ 4.0 mA               | 4.5V            | 4.2                  | 3.98  | 3.84                        | V                                     |

|                 |                                    | I <sub>OUT</sub>   ≤ 5.2 mA               | 6.0V            | 5.7                  | 5.48  | 5.34                        | V                                     |

| V <sub>OL</sub> | Maximum LOW Level                  | $V_{IN} = V_{IH}$ or $V_{IL}$             | 2.0V            | 0                    | 0.1   | 0.1                         | V                                     |

|                 | Output Voltage                     | I <sub>OUT</sub>   ≤ 20 μA                | 4.5V            | 0                    | 0.1   | 0.1                         | V                                     |

|                 |                                    |                                           | 6.0V            | 0                    | 0.1   | 0.1                         | V                                     |

|                 |                                    | $V_{IN} = V_{IH}$ or $V_{IL}$             |                 |                      |       |                             |                                       |

|                 |                                    | I <sub>OUT</sub>   ≤ 4.0 mA               | 4.5V            | 0.2                  | 0.26  | 0.33                        | V                                     |

|                 |                                    | I <sub>OUT</sub>   ≤ 5.2 mA               | 6.0V            | 0.2                  | 0.26  | 0.33                        | V                                     |

| I <sub>IN</sub> | Maximum Input Current (Pins 3,5,9) | V <sub>IN</sub> = V <sub>CC</sub> or GND  | 6.0V            |                      | ±0.1  | ±1.0                        | μΑ                                    |

| I <sub>IN</sub> | Maximum Input Current (Pin 14)     | V <sub>IN</sub> = V <sub>CC</sub> or GND  | 6.0V            | 20                   | 50    | 80                          | μΑ                                    |

| I <sub>OZ</sub> | Maximum 3-STATE Output             | V <sub>OUT</sub> = V <sub>CC</sub> or GND | 6.0V            |                      | ±0.25 | ±2.5                        | μΑ                                    |

|                 | Leakage Current (Pin 13)           |                                           |                 |                      |       |                             |                                       |

| I <sub>CC</sub> | Maximum Quiescent Supply           | V <sub>IN</sub> = V <sub>CC</sub> or GND  | 6.0V            | 30                   | 40    | 65                          | μΑ                                    |

|                 | Current                            | $I_{OUT} = 0 \mu A$                       |                 |                      |       |                             |                                       |

|                 |                                    | $V_{IN} = V_{CC}$ or GND                  | 6.0V            | 600                  | 750   | 1200                        | μΑ                                    |

|                 |                                    | Pin 14 Open                               |                 |                      |       |                             |                                       |

Note 4: For a power supply of 5V  $\pm$ 10% the worst case output voltages (V<sub>OH</sub>, and V<sub>OL</sub>) occur for VHC at 4.5V. Thus the 4.5V values should be used when designing with this supply. Worst case V<sub>IH</sub> and V<sub>IL</sub> occur at V<sub>CC</sub> = 5.5V and 4.5V respectively. (The V<sub>IH</sub> value at 5.5V is 3.85V.) The worst case leakage current (I<sub>IN</sub>, I<sub>CC</sub>, and I<sub>OZ</sub>) occur for CMOS at the higher voltage and so the 6.0V values should be used.

# $\textbf{AC Electrical Characteristics} \ \ V_{\text{CC}} = 2.0 \ \text{to 6.0V, C}_{L} = 50 \ \text{pF, t}_{r} = t_{f} = 6 \ \text{ns (unless otherwise specified.)}$

| Symbol                              | Parameters                          | Conditions                                | v <sub>cc</sub> | T <sub>A</sub> =25C T <sub>A</sub> =-40 to 85°C |          |           | Units |

|-------------------------------------|-------------------------------------|-------------------------------------------|-----------------|-------------------------------------------------|----------|-----------|-------|

| J,11001                             |                                     |                                           |                 | Тур                                             | Guarante | ed Limits |       |

|                                     | AC Coupled                          | C (series) = 100 pF                       | 2.0V            | 25                                              | 100      | 150       | mV    |

|                                     | Input Sensitivity,                  | $f_{IN} = 500 \text{ kHz}$                | 4.5V            | 50                                              | 150      | 200       | mV    |

|                                     | Signal In                           |                                           | 6.0V            | 135                                             | 250      | 300       | mV    |

| t <sub>r</sub> , t <sub>f</sub>     | Maximum Output                      |                                           | 2.0V            | 30                                              | 75       | 95        | ns    |

|                                     | Rise and Fall Time                  |                                           | 4.5V            | 9                                               | 15       | 19        | ns    |

|                                     |                                     |                                           | 6.0V            | 8                                               | 12       | 15        | ns    |

| C <sub>IN</sub>                     | Maximum Input                       |                                           | 7               |                                                 |          |           | pF    |

|                                     | Capacitance                         |                                           |                 |                                                 |          |           |       |

| Phase Con                           | parator I                           |                                           |                 | l                                               | I        |           |       |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation                 |                                           | 3.3V            | 65                                              | 117      | 146       | ns    |

|                                     | Delay                               |                                           | 4.5V            | 25                                              | 40       | 50        | ns    |

|                                     |                                     |                                           | 6.0V            | 20                                              | 34       | 43        | ns    |

| Phase Con                           | nparator II                         |                                           |                 |                                                 |          |           |       |

| PZL                                 | Maximum 3-STATE                     |                                           | 3.3V            | 75                                              | 130      | 160       | ns    |

| PZL                                 | Enable Time                         |                                           | 4.5V            | 25                                              | 45       | 56        | ns    |

|                                     | Lilable fille                       |                                           | 6.0V            | 22                                              | 38       | 48        |       |

|                                     | Maximum 3-STATE                     |                                           |                 | 88                                              | 140      | 175       | ns    |

| t <sub>PZH</sub> , t <sub>PHZ</sub> |                                     |                                           | 3.3V            |                                                 |          |           | ns    |

|                                     | Enable Time                         |                                           | 4.5V            | 30                                              | 48       | 60        | ns    |

|                                     |                                     |                                           | 6.0V            | 25                                              | 41       | 51        | ns    |

| PLZ                                 | Maximum 3-STATE                     |                                           | 3.3V            | 90                                              | 140      | 175       | ns    |

|                                     | Disable Time                        |                                           | 4.5V            | 32                                              | 48       | 60        | ns    |

|                                     |                                     |                                           | 6.0V            | 28                                              | 41       | 51        | ns    |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation                 |                                           | 3.3V            | 100                                             | 146      | 180       | ns    |

|                                     | Delay HIGH-to-LOW                   |                                           | 4.5V            | 34                                              | 50       | 63        | ns    |

|                                     | to Phase Pulses                     |                                           | 6.0V            | 27                                              | 43       | 53        | ns    |

| Phase Con                           | parator III                         |                                           |                 |                                                 |          |           |       |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Maximum Propagation                 |                                           | 3.3V            | 75                                              | 117      | 146       | ns    |

|                                     | Delay                               |                                           | 4.5V            | 25                                              | 40       | 50        | ns    |

|                                     |                                     |                                           | 6.0V            | 22                                              | 34       | 43        | ns    |

| C <sub>PD</sub>                     | Maximum Power                       | All Comparators                           |                 | 130                                             |          |           | pF    |

|                                     | Dissipation                         | V <sub>IN</sub> = V <sub>CC</sub> and GND |                 |                                                 |          |           |       |

|                                     | Capacitance                         |                                           |                 |                                                 |          |           |       |

|                                     |                                     | 10.14                                     |                 |                                                 |          |           |       |

| voltage Co                          | ntrolled Oscillator (Spec           | ified to operate from V <sub>CC</sub> = 3 | 3.0V to 6.0V)   |                                                 |          |           |       |

| $f_{MAX}$                           | Maximum                             | $C_1 = 50 \text{ pF}$                     |                 |                                                 |          |           |       |

|                                     | Operating                           | $R_1 = 100\Omega$                         | 4.5V            | 7                                               | 4.5      |           | MHz   |

|                                     | Frequency                           | $R_2 = \infty$                            | 6.0V            | 11                                              | 7        |           | MH    |

|                                     |                                     | $VCO_{in} = V_{CC}$                       |                 |                                                 |          |           |       |

|                                     |                                     | $C_1 = 0 pF$                              | 4.5V            | 12                                              |          |           | MHz   |

|                                     |                                     | $R_1=100\Omega$                           | 6.0             | 14                                              |          |           | MHz   |

|                                     |                                     | $VCO_{in} = V_{CC}$                       |                 |                                                 |          |           |       |

|                                     | Duty Cycle                          |                                           |                 | 50                                              |          |           | %     |

| Demodulat                           | or Output                           | 1                                         |                 | I.                                              | 1        | 1         |       |

|                                     | Offset Voltage                      | $R_s = 20 \text{ k}\Omega$                | 4.5V            | 0.75                                            | 1.3      | 1.5       | V     |

|                                     | VCO <sub>in</sub> -V <sub>dem</sub> | 1 -                                       |                 |                                                 |          |           |       |

|                                     | Offset                              | $R_s = 20 \text{ k}\Omega$                | 4.5V            |                                                 |          |           |       |

|                                     | Variation                           | VCO <sub>in</sub> = 1.75V                 | 7.57            | 0.65                                            |          |           | V     |

|                                     | - andion                            | 2.25V                                     |                 | 0.03                                            |          |           | ٧     |

|                                     |                                     |                                           |                 |                                                 |          |           |       |

|                                     |                                     | 2.75V                                     |                 | 0.75                                            | Ī        | i l       |       |

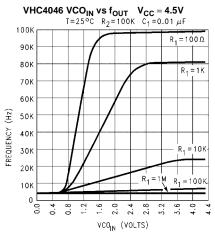

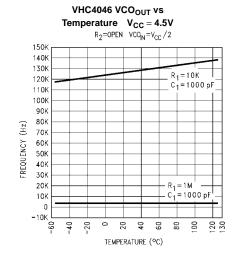

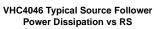

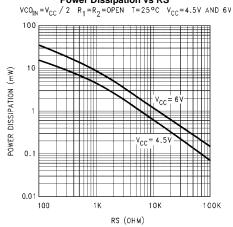

# **Typical Performance Characteristics**

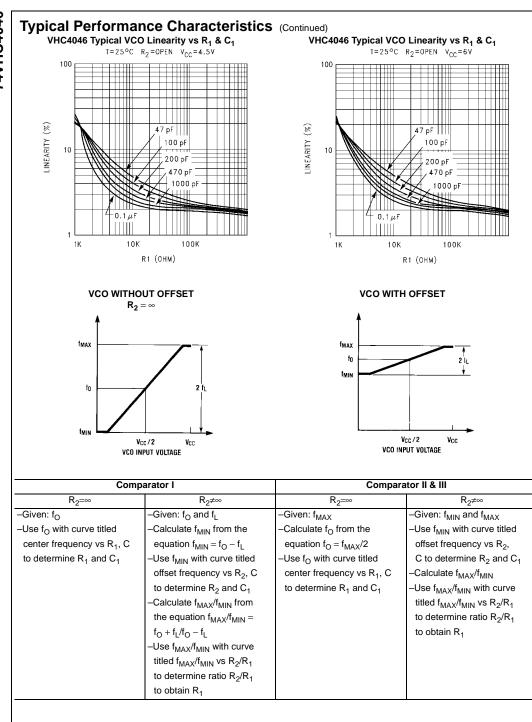

## Typical Performance Characteristics (Continued)

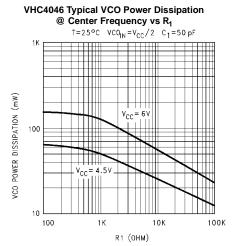

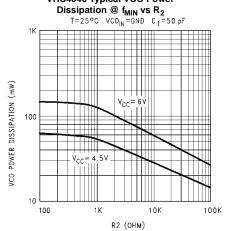

# VHC4046 Typical VCO Power

## **Typical Performance Characteristics** (Continued)

#### Temperature $V_{CC} = 6V$ $R_2 = OPEN VCQ_N = V_{CC}/2$ 180K R<sub>1</sub> = 10K — C<sub>1</sub> = 1000 pF 160K 120K 100K FREQUENCY (Hz) 80K 60K 40K 20K C1 = 1000 pF -10K└ -40 20 9 8 -20 80 40 TEMPERATURE (°C)

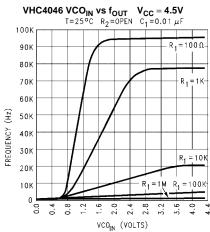

VHC4046 VCO<sub>OUT</sub> vs

## **Detailed Circuit Description**

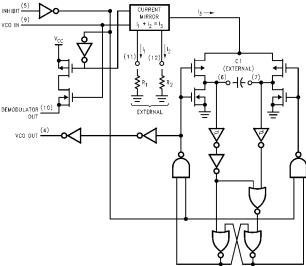

# VOLTAGE CONTROLLED OSCILLATOR/SOURCE FOLLOWER

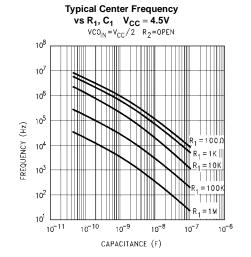

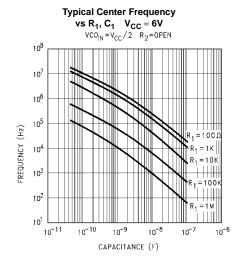

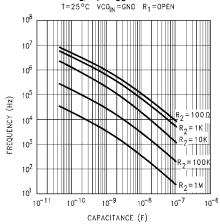

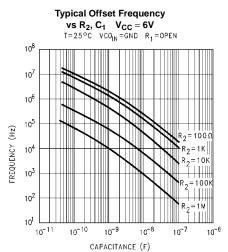

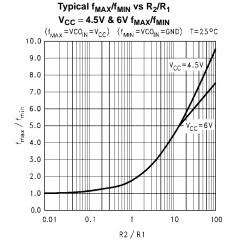

The VCO requires two or three external components to operate. These are  $R_1$ ,  $R_2$ ,  $C_1$ . Resistor  $R_1$  and capacitor  $C_1$  are selected to determine the center frequency of the VCO.  $R_1$  controls the lock range. As R1's resistance decreases the range of  $f_{\text{MIN}}$  to  $f_{\text{MAX}}$  increases. Thus the VCO's gain increases. As  $C_1$  is changed the offset (if used) of  $R_2$ , and the center frequency is changed. (See typical

performance curves)  $R_2$  can be used to set the offset frequency with 0V at VCO input. If  $R_2$  is omitted the VCO range is from 0Hz. As  $R_2$  is decreased the offset frequency is increased. The effect of  $R_2$  is shown in the design information table and typical performance curves. By increasing the value of  $R_2$  the lock range of the PLL is offset above 0Hz and the gain (Hz/Volt) does not change. In general, when offset is desired,  $R_2$  and  $C_1$  should be chosen first, and then  $R_1$  should be chosen to obtain the proper center frequency.

FIGURE 1. Logic Diagram for VCO

Internally the resistors set a current in a current mirror as shown in *Figure 1*. The mirrored current drives one side of the capacitor once the capacitor charges up to the threshold of the Schmitt Trigger the oscillator logic flips the capacitor over and causes the mirror to charge the opposite side of the capacitor. The output from the internal logic is then taken to pin 4.

The input to the VCO is a very high impedance CMOS input and so it will not load down the loop filter, easing the filters design. In order to make signals at the VCO input accessible without degrading the loop performance a source follower transistor is provided. This transistor can be used by connecting a resistor to ground and its drain output will follow the VCO input signal.

An inhibit signal is provided to allow disabling of the VCO and the source follower. This is useful if the internal VCO is not being used. A logic high on inhibit disables the VCO and source follower.

The output of the VCO is a standard high speed CMOS output with an equivalent LSTTL fanout of 10. The VCO output is approximately a square wave. This output can either directly feed the comparator input of the phase comparators or feed external prescalers (counters) to enable frequency synthesis.

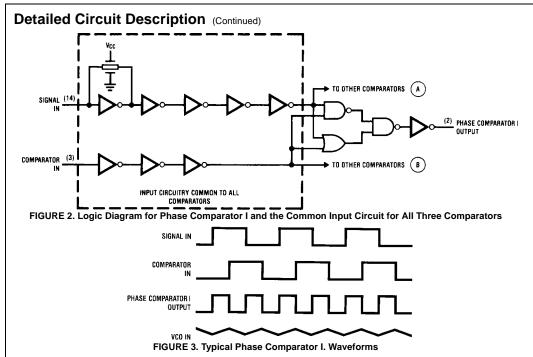

#### PHASE COMPARATORS

All three phase comparators share two inputs, Signal In and Comparator In. The Signal In has a special DC bias network that enables AC coupling of input signals. If the signals are not AC coupled then this input requires logic levels the same as standard 74VHC. The Comparator input is a standard digital input. Both input structures are shown in *Figure 2*.

The outputs of these comparators are essentially standard 74VHC voltage outputs. (Comparator II is 3-STATE.)

Thus in normal operation  $V_{CC}$  and ground voltage levels are fed to the loop filter. This differs from some phase detectors which supply a current output to the loop filter and this should be considered in the design. (The CD4046 also provides a voltage.)

Figure 4 shows the state tables for all three comparators.

#### PHASE COMPARATOR I

This comparator is a simple XOR gate similar to the 74HC86, and its operation is similar to an overdriven balanced modulator. To maximize lock range the input frequencies must have a 50% duty cycle. Typical input and output waveforms are shown in *Figure* 3. The output of the phase detector feeds the loop filter which averages the output voltage. The frequency range upon which the PLL will lock onto if initially out of lock is defined as the capture range. The capture range for phase detector I is dependent on the loop filter employed. The capture range can be as large as the lock range which is equal to the VCO frequency range.

To see how the detector operates refer to Figure 3. When two square wave inputs are applied to this comparator, an output waveform whose duty cycle is dependent on the phase difference between the two signals results. As the phase difference increases the output duty cycle increases and the voltage after the loop filter increases. Thus in order to achieve lock, when the PLL input frequency increases the VCO input voltage must increase and the phase difference between comparator in and signal in will increase. At an input frequency equal  $f_{\rm MIN}$ , the VCO input is at 0V and this requires the phase detector output to be ground hence the two input signals must be in phase. When the input fre-

quency is  $f_{MAX}$  then the VCO input must be  $V_{CC}$  and the phase detector inputs must be 180° out of phase.

The XOR is more susceptible to locking onto harmonics of the signal input than the digital phase detector II. This can be seen by noticing that a signal 2 times the VCO frequency results in the same output duty cycle as a signal equal the VCO frequency. The difference is that the output frequency of the 2f example is twice that of the other example. The loop filter and the VCO range should be designed to prevent locking on to harmonics.

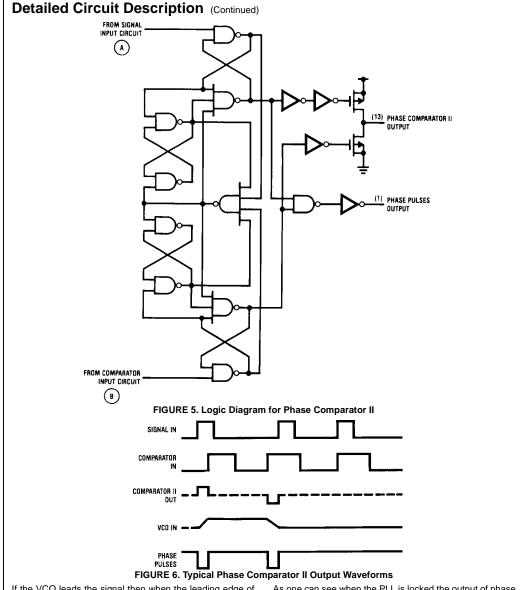

#### PHASE COMPARATOR II

This detector is a digital memory network. It consists of four flip-flops and some gating logic, a three state output and a phase pulse output as shown in *Figure 5*. This comparator acts only on the positive edges of the input signals and is thus independent of signal duty cycle.

Phase comparator II operates in such a way as to force the PLL into lock with 0 phase difference between the VCO output and the signal input positive waveform edges. Figure 6 shows some typical loop waveforms. First assume that the signal input phase is leading the comparator input. This means that the VCO's frequency must be increased to bring its leading edge into proper phase alignment. Thus the phase detector II output is set HIGH. This will cause the loop filter to charge up the VCO input increasing the VCO frequency. Once the leading edge of the comparator input is detected the output goes 3-STATE holding the VCO input at the loop filter voltage. If the VCO still lags the signal then the phase detector will again charge up to VCO input for the time between the leading edges of both waveforms.

# Detailed Circuit Description (Continued) Phase Comparator State Diagrams

FIGURE 4. PLL State Tables

If the VCO leads the signal then when the leading edge of the VCO is seen the output of the phase comparator goes LOW. This discharges the loop filter until the leading edge of the signal is detected at which time the output 3-STATEs itself again. This has the effect of slowing down the VCO to again make the rising edges of both waveform coincident.

When the PLL is out of lock the VCO will be running either slower or faster than the signal input. If it is running slower the phase detector will see more signal rising edges and so the output of the phase comparator will be high a majority of the time, raising the VCO's frequency. Conversely, if the VCO is running faster than the signal the output of the detector will be low most of the time and the VCO's output frequency will be decreased.

As one can see when the PLL is locked the output of phase comparator II will be almost always 3-STATE except for minor corrections at the leading edge of the waveforms. When the detector is 3-STATE the phase pulse output is HIGH. This output can be used to determine when the PLL is in the locked condition.

This detector has several interesting characteristics. Over the entire VCO frequency range there is no phase difference between the comparator input and the signal input. The lock range of the PLL is the same as the capture range. Minimal power is consumed in the loop filter since in lock the detector output is a high impedance. Also when no signal is present the detector will see only VCO leading edges, and so the comparator output will stay low forcing the VCO to f<sub>MIN</sub> operating frequency.

## **Detailed Circuit Description** (Continued)

Phase comparator II is more susceptible to noise causing the phase lock loop to unlock. If a noise pulse is seen on the signal input, the comparator treats it as another positive edge of the signal and will cause the output to go HIGH until the VCO leading edge is seen, potentially for a whole signal input period. This would cause the VCO to speed up during that time. When using the phase comparator I the output of that phase detector would be disturbed for only the short duration of the noise spike and would cause less upset.

#### PHASE COMPARATOR III

This comparator is a simple S-R Flip-Flop which can function as a phase comparator *Figure 7*. It has some similar characteristics to the edge sensitive comparator. To see

how this detector works assume input pulses are applied to the signal and comparator inputs as shown in *Figure 8*. When the signal input leads the comparator input the flop is set. This will charge up the loop filter and cause the VCO to speed up, bringing the comparator into phase with the signal input. When using short pulses as input this comparator behaves very similar to the second comparator. But one can see that if the signal input is a long pulse, the output of the comparator will be forced to a one no matter how many comparator input pulses are received. Also if the VCO input is a square wave (as it is) and the signal input is pulse then the VCO will force the comparator output LOW much of the time. Therefore it is ideal to condition the signal and comparator input to short pulses. This is most easily done by using a series capacitor.

# Physical Dimensions inches (millimeters) unless otherwise noted $\frac{0.386 - 0.394}{(9.804 - 10.00)}$ 13 Ĥ 0.228 - 0.244 (5.791 - 6.198) LEAD NO.1

$\frac{0.010}{(0.254)}$  MAX

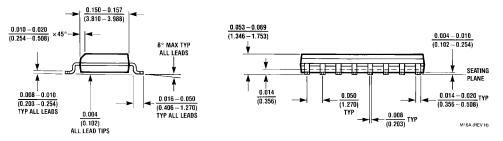

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M16A

#### Physical Dimensions inches (millimeters) unless otherwise noted (Continued) 0.740 - 0.780 0.090 (18.80 - 19.81)(2.286)**16 15 14 13 12 11 10 9** 16 15 INDEX AREA 0.250 ± 0.010 $\overline{(6.350 \pm 0.254)}$ PIN NO. 1 PIN NO. 1 1 2 3 4 5 6 7 8 1 2 OPTION 01 OPTION 02 0.065 $\frac{0.130 \pm 0.005}{(3.302 \pm 0.127)}$ $\frac{0.060}{(1.524)}$ TYP (1.651)4° TYP 0.300 - 0.320OPTIONAL (7.620 - 8.128) 0.145 - 0.200 (3.683 - 5.080)95°±5° 0.008 = 0.016 (0.203 = 0.406) TYP 90° ± 4° TYP 0.020 $\frac{0.280}{(7.112)}$ MIN (0.508)0.125 - 0.150 (3.175 - 3.810) $0.030 \pm 0.015$ $(0.762 \pm 0.381)$ 0.014 - 0.023 0.100 ± 0.010 (0.325 **+**0.040 **-**0.015 (0.356 - 0.584) $(2.540 \pm 0.254)$ 0.050 ± 0.010 N16E (REV F) TYP (1.270 ± 0.254)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com