# Quad Channel Low Capacitance ESD Protection Array UM5204EECD SOT23-6 UM5204EECE SOT23-6

#### **General Description**

UM5204EECD/EECE is surge rated diode arrays designed to protect high speed data interfaces. This series has been specifically designed to protect sensitive components which are connected to data and transmission lines from over-voltage caused by ESD (electrostatic discharge), electrical fast transients (EFT) and lighting.

The unique design incorporates surge rated, low capacitance steering diodes and a TVS diode in a single package. During transient conditions, the steering diodes direct the transient to either the positive side of the power supply line or to ground. The internal TVS diode prevents over-voltage on the power line, protecting any downstream components.

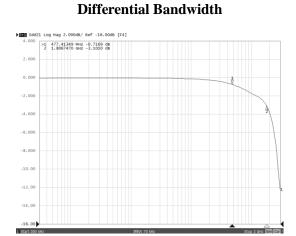

UM5204EECD/EECE has a low typical capacitance of 1pF and operates with virtually no insertion loss to 2GHz. This makes the device ideal for protection of high-speed data line such as USB2.0, Firewire, DVI and gigabit Ethernet interface.

The low capacitance array configuration allows the user to protect four high-speed data or transmission lines. The low inductance construction minimizes voltage overshoot during high current surges. This device is optimized for ESD protection of portable electronics. They may be used to meet the ESD immunity requirements of IEC 61000-4-2, Level 4 ( $\pm 15$ kV air,  $\pm 8$ kV contact discharge).

#### Applications

**USB 2.0**

(HDMI) SIM Ports

USB OTG

10/100/1000Mbit Ethernet Monitors and Flat Panel Displays

**IEEE 1394** Firewire Ports

Digital Visual Interface (DVI)

High-Definition Multimedia Interface

#### Features

- Transient Protection for High-Speed Data Lines to IEC 61000-4-2 (ESD) ±20kV (Air), ±12kV

- $\begin{array}{c} \text{IEC } 61000\text{-}4\text{-}2 \ \text{(ESD)} \pm 20\text{KV} \ \text{(Air),} \pm 12\text{KV} \\ \text{(Contact)} \\ \text{IEC } 61000 \ \text{A} \ \text{A} \ \text{(EET)} \ 40\text{A} \ (5/50 \ \text{Contact)} \end{array}$

- IEC 61000-4-4 (EFT) 40A (5/50ns)

- IEC 61000-4-5 (Lighting) 10A (8/20µs)

- Array of Surge Rated Diodes with Internal TVS Diode

- Protects up to Four I/O Lines & Power Line

- Low Capacitance (<1pF) for High-Speed Interfaces, No Insertion Loss to 2.0GHz

- Low Leakage Current and Clamping Voltage

- Low Operating Voltage: 5.0V

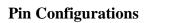

**Top View**

### **Ordering Information**

| Part Number | Working<br>Voltage | Packaging Type | Channel | Marking<br>Code | Shipping Qty                  |

|-------------|--------------------|----------------|---------|-----------------|-------------------------------|

| UM5204EECD  | 5.0V               | SOT23-6        | 4       | UCF             | 3000pcs/7 Inch<br>Tape & Reel |

| UM5204EECE  | 5.0V               | SOT23-6        | 4       | UCC             | 3000pcs/7 Inch<br>Tape & Reel |

# Absolute Maximum Ratings

| Rating                                                         | Symbol           | Value       | Unit  |

|----------------------------------------------------------------|------------------|-------------|-------|

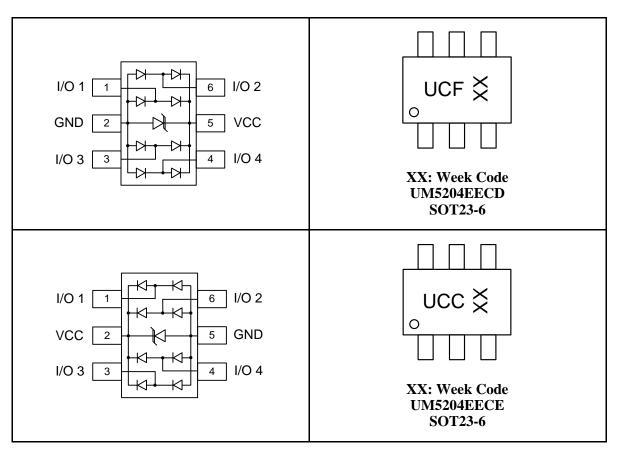

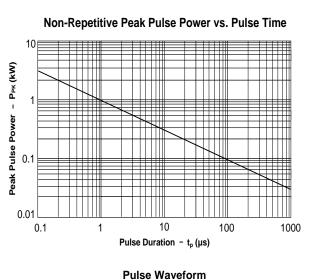

| Peak Pulse Power ( $t_P=8/20\mu s$ )                           | $P_{pk}$         | 200         | Watts |

| Peak Pulse Current ( $t_P=8/20\mu s$ )                         | I <sub>PP</sub>  | 10          | А     |

| Peak Pulse Current (t <sub>P</sub> =5/50ns)                    | $I_{PP}$         | 40          | А     |

| ESD per IEC 61000-4-2 (Air)<br>ESD per IEC 61000-4-2 (Contact) | V <sub>ESD</sub> | ±20<br>±12  | kV    |

| Operating Temperature                                          | T <sub>J</sub>   | -55 to +125 | °C    |

| Storage Temperature                                            | T <sub>STG</sub> | -55 to +150 | °C    |

### **Electrical Characteristics (Note 1)**

| Parameter                    | Symbol           | Test Conditions                                                            | Min  | Тур | Max | Unit |

|------------------------------|------------------|----------------------------------------------------------------------------|------|-----|-----|------|

| Reverse Stand-Off<br>Voltage | V <sub>RWM</sub> | VCC to GND                                                                 | ND 5 |     | 5.0 | V    |

| Reverse Breakdown<br>Voltage | $V_{BR}$         | $ \begin{array}{c c} I_{T}=1mA, \\ VCC \text{ to GND} \\ \end{array} $ 6.0 |      |     | V   |      |

| Reverse Leakage<br>Current   | I <sub>R</sub>   | V <sub>RWM</sub> =5V,<br>VCC to GND                                        |      |     | 2   | μA   |

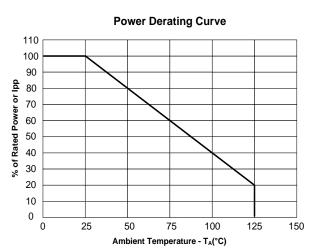

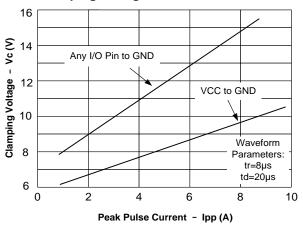

| Clamping Voltage             | V <sub>C</sub>   | I <sub>PP</sub> =1A, 8/20µs<br>Any I/O Pin to GND                          |      | 8   | 10  | V    |

| Clamping Voltage             | V <sub>C</sub>   | I <sub>PP</sub> =5A, 8/20µs<br>Any I/O Pin to GND                          |      |     | 15  | V    |

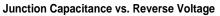

| Junction<br>Capacitance      | Cj               | V <sub>R</sub> =0V, f=1MHz<br>Any I/O Pin to GND                           |      |     | 2   | pF   |

|                              |                  | V <sub>R</sub> =0V, f=1MHz ,<br>Between I/O Pins                           |      |     | 1   | pF   |

|                              |                  | V <sub>R</sub> =0V, f=1MHz<br>VCC to GND                                   |      | 60  |     | pF   |

|                              |                  | V <sub>R</sub> =2.5V, f=1MHz<br>VCC to GND                                 |      | 40  |     | pF   |

| Reverse Recovery<br>Time     | Trr              | Any I/O Pin to VCC                                                         |      | 130 |     | ns   |

|                              |                  | GND to VCC                                                                 |      | 300 |     | ns   |

|                              |                  | GND to any I/O Pin                                                         |      | 400 |     | ns   |

Note 1: I/O pins are pin 1, 3, 4, and 6

# UM5204

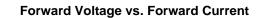

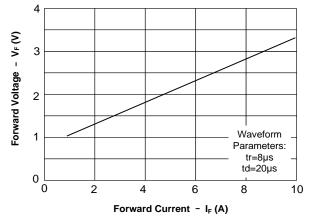

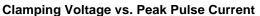

### **Typical Operating Characteristics**

### **Typical Operating Characteristics (Continued)**

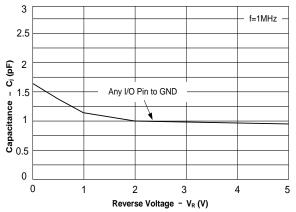

### Single End Bandwidth

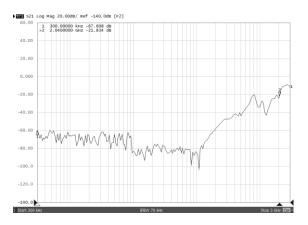

### Crosstalk

#### **Applications Information**

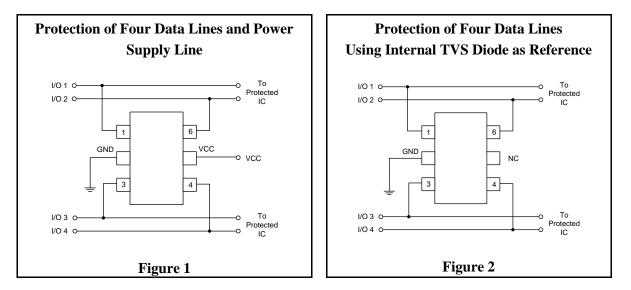

#### **Device Connection Options for Protection of Four High-Speed Data Lines**

This device is designed to protect four data lines by clamping them to a fixed reference. When the voltage on the protected line exceeds the reference voltage the steering diodes are forward biased, conducting the transient current away from the sensitive circuitry. Data lines are connected at I/O pins. GND pin should be connected directly to a ground plane. The path length is kept as short as possible to minimize parasitic inductance. The positive reference is connected at VCC pin. The options for connecting the positive reference are as follows:

1. To protect data lines and the power line, connect VCC pin directly to the positive supply rail (VCC). In this configuration the data lines are referenced to the supply voltage. The internal TVS diode prevents over-voltage on the supply rail. See Figure 1.

2. In applications where the supply rail does not exit the system, the internal TVS may be used as the reference. In this case, VCC pin is not connected. The steering diodes will begin to conduct when the voltage on the protected line exceeds the working voltage of the TVS (plus one diode drop).

3. In applications where complete supply isolation is desired, the internal TVS is again used as the reference and VCC is connected to one of the I/O inputs. An example of this configuration is the protection of a SIM port. The Clock, Reset, I/O, and VCC lines are connected at I/O pins. GND pin is connected to ground and VCC pin is not connected. See Figure 2.

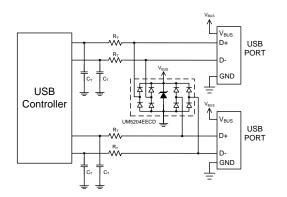

#### **Universal Serial Bus ESD Protection**

The UM5204EECD/EECE may also be used to protect the USB ports on monitors, computers, peripherals or portable systems. Each device will protect up to two USB ports (Figure 3). When the voltage on the data lines exceed the bus voltage (plus one diode drop), the internal rectifiers are forward biased conducting the transient current away from the protected controller chip. The TVS diode directs the surge to ground. The TVS diode also acts to suppress ESD strikes directly on the voltage bus. Thus, both power and data pins are protected with a single device.

**Figure 3 Dual USB Port Protection**

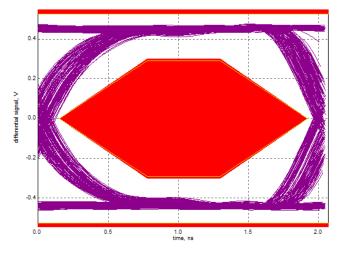

Figure 4 USB Eye Diagram

Note: Figure 4 is tested by the MSO9254A oscilloscope of Agilent including E2678 probe, 1169 differential probe and E2645B-66401 fixture, when the chip is linked into the data line.

#### **10/100 Ethernet Protection**

Ethernet ICs are vulnerable to damage from electrostatic discharge (ESD). The internal protection in the PHY chip, if any, often is not enough due to the high energy of the discharges specified by IEC61000-4-2. If the discharge is catastrophic, it will destroy the protected IC. If it is less severe, it will cause latent failures that are very difficult to find.

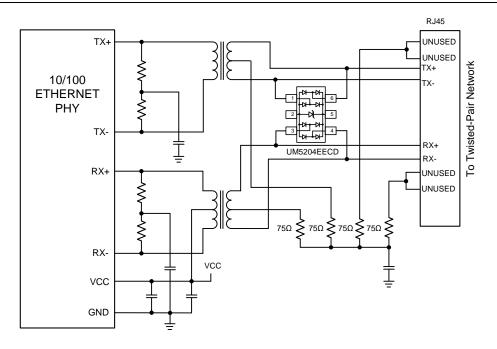

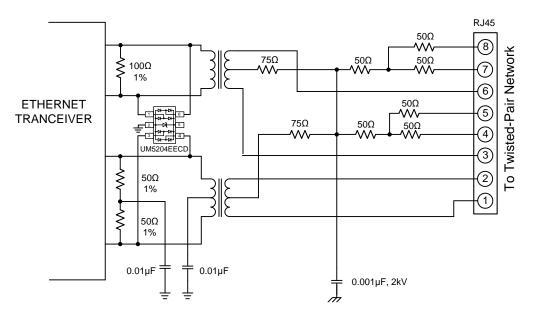

10/100 Ethernet operates at 125MHz clock over a twisted pair interface. In a typical system, the twisted pair interface for each port consists of two differential signal pairs: one for the transmitter and one for the receiver, with the transmitter input being the most sensitive to damage. The fatal discharge occurs differentially across the transmitter or receiver line pair and is capacitively coupled through the transformer to the Ethernet chip. Figure 5 shows how to design the UM5204EECD/EECE on the line side of a 10/100 ethernet port to provide differential mode protection. The common mode isolation of the transformer will provide common mode protection to the rating of the transformer isolation which is usually >1.5kV. If more common mode protection is needed, figure 6 shows how to design the UM5204EECD/EECE on the IC side of the 10/100 Ethernet circuit to provide differential and common mode protection. The uM5204EECD/EECE can not be grounded on the line side because the hi-pot test requires the line side not to be grounded.

Figure 5 10/100 Ethernet Differential Protection

Figure 6 10/100 Ethernet Differential and Common Mode Protection

#### Matte Tin Lead Finish

Matte tin has become the industry standard lead-free replacement for SnPb lead finishes. A matte tin finish is composed of 100% tin solder with large grains. Since the solder volume on the leads is small compared to the solder paste volume that is placed on the land pattern of the PCB, the reflow profile will be determined by the requirements of the solder paste. Therefore, these devices are compatible with both lead-free and SnPb assembly techniques. In addition, unlike other lead-free compositions, matte tin does not have any added alloys that can cause degradation of the solder joint.

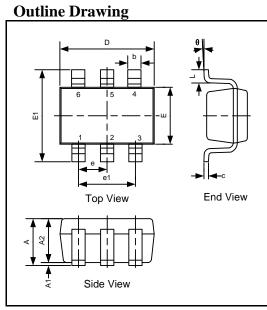

# **Package Information**

### **UM5204EECD SOT23-6**

| DIMENSIONS |             |      |      |          |        |       |  |

|------------|-------------|------|------|----------|--------|-------|--|

| Symbol     | MILLIMETERS |      |      | INCHES   |        |       |  |

| Symbol     | Min         | Тур  | Max  | Min      | Тур    | Max   |  |

| А          | 1.013       | 1.15 | 1.40 | 0.040    | 0.045  | 0.055 |  |

| A1         | 0.00        | 0.05 | 0.10 | 0.000    | 0.002  | 0.004 |  |

| A2         | 1.00        | 1.10 | 1.30 | 0.039    | 0.043  | 0.051 |  |

| b          | 0.30        | -    | 0.50 | 0.012    | -      | 0.020 |  |

| с          | 0.10        | 0.15 | 0.20 | 0.004    | 0.006  | 0.008 |  |

| D          | 2.82        | -    | 3.10 | 0.111    | -      | 0.122 |  |

| Е          | 1.50        | 1.60 | 1.70 | 0.059    | 0.063  | 0.067 |  |

| E1         | 2.60        | 2.80 | 3.00 | 0.102    | 0.110  | 0.118 |  |

| e          | 0.95REF     |      |      | C        | .037RE | F     |  |

| e1         | 1.90REF     |      |      | 0.075REF |        |       |  |

| L          | 0.30        | -    | 0.60 | 0.012    | _      | 0.024 |  |

| θ          | 0°          | -    | 8°   | 0°       | -      | 8°    |  |

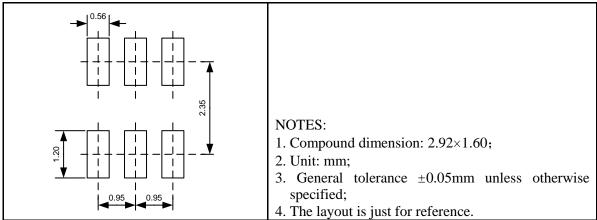

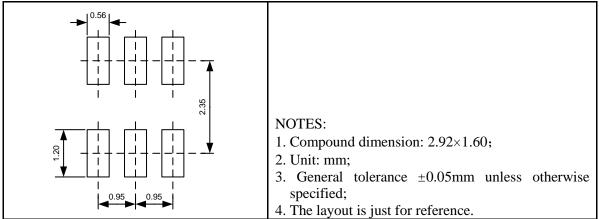

#### Land Pattern

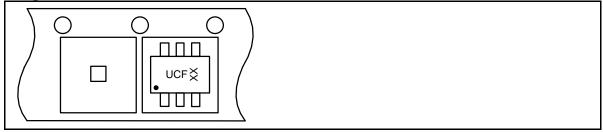

#### **Tape and Reel Orientation**

INCHES

Тур

0.045

0.002

0.043

-

0.006

-

0.063

0.110

0.037REF

0.075REF

-

-

Max

0.055

0.004

0.051

0.020

0.008

0.122

0.067

0.118

0.024

8°

Min

0.040

0.000

0.039

0.012

0.004

0.111

0.059

0.102

0.012

$0^{\circ}$

| Outline Drawing |               |            |             |        |      |     |  |

|-----------------|---------------|------------|-------------|--------|------|-----|--|

| ı D ı           | A 11          | DIMENSIONS |             |        |      |     |  |

|                 | ¥<br>⊥        | Symbol     | MILLIMETERS |        |      |     |  |

|                 |               |            | Min         | Тур    | Max  | M   |  |

|                 |               | А          | 1.013       | 1.15   | 1.40 | 0.0 |  |

|                 |               | A1         | 0.00        | 0.05   | 0.10 | 0.0 |  |

|                 |               | A2         | 1.00        | 1.10   | 1.30 | 0.0 |  |

|                 | $\mathcal{T}$ | b          | 0.30        | -      | 0.50 | 0.0 |  |

|                 | , H ,         | с          | 0.10        | 0.15   | 0.20 | 0.0 |  |

|                 | -▶   ◀-○      | D          | 2.82        | -      | 3.10 | 0.1 |  |

| Top View        | End View      | E          | 1.50        | 1.60   | 1.70 | 0.0 |  |

|                 | E1            | 2.60       | 2.80        | 3.00   | 0.1  |     |  |

|                 | e             | 0.95REF    |             |        |      |     |  |

|                 |               | e1         | 1           | .90REF | 7    |     |  |

| Side View       |               | L          | 0.30        | -      | 0.60 | 0.0 |  |

|                 |               | θ          | $0^{\circ}$ | -      | 8°   | 0   |  |

# **UM5204EECE SOT23-6**

Land Pattern

#### **Tape and Reel Orientation**

# **GREEN COMPLIANCE**

Union Semiconductor is committed to environmental excellence in all aspects of its operations including meeting or exceeding regulatory requirements with respect to the use of hazardous substances. Numerous successful programs have been implemented to reduce the use of hazardous substances and/or emissions.

All Union components are compliant with the RoHS directive, which helps to support customers in their compliance with environmental directives. For more green compliance information, please visit:

http://www.union-ic.com/index.aspx?cat\_code=RoHSDeclaration

# **IMPORTANT NOTICE**

The information in this document has been carefully reviewed and is believed to be accurate. Nonetheless, this document is subject to change without notice. Union assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the contained information, or to notify a person or organization of any update. Union reserves the right to make changes, at any time, in order to improve reliability, function or design and to attempt to supply the best product possible.

Union Semiconductor, Inc Add: Unit 606, No.570 Shengxia Road, Shanghai 201210 Tel: 021-51093966 Fax: 021-51026018 Website: www.union-ic.com