CXA1871S View Datasheet(PDF) - Sony Semiconductor

Part Name

Description

Manufacturer

CXA1871S Datasheet PDF : 46 Pages

| |||

CXA1871S

Pin

Pin

Symbol

No.

voltage

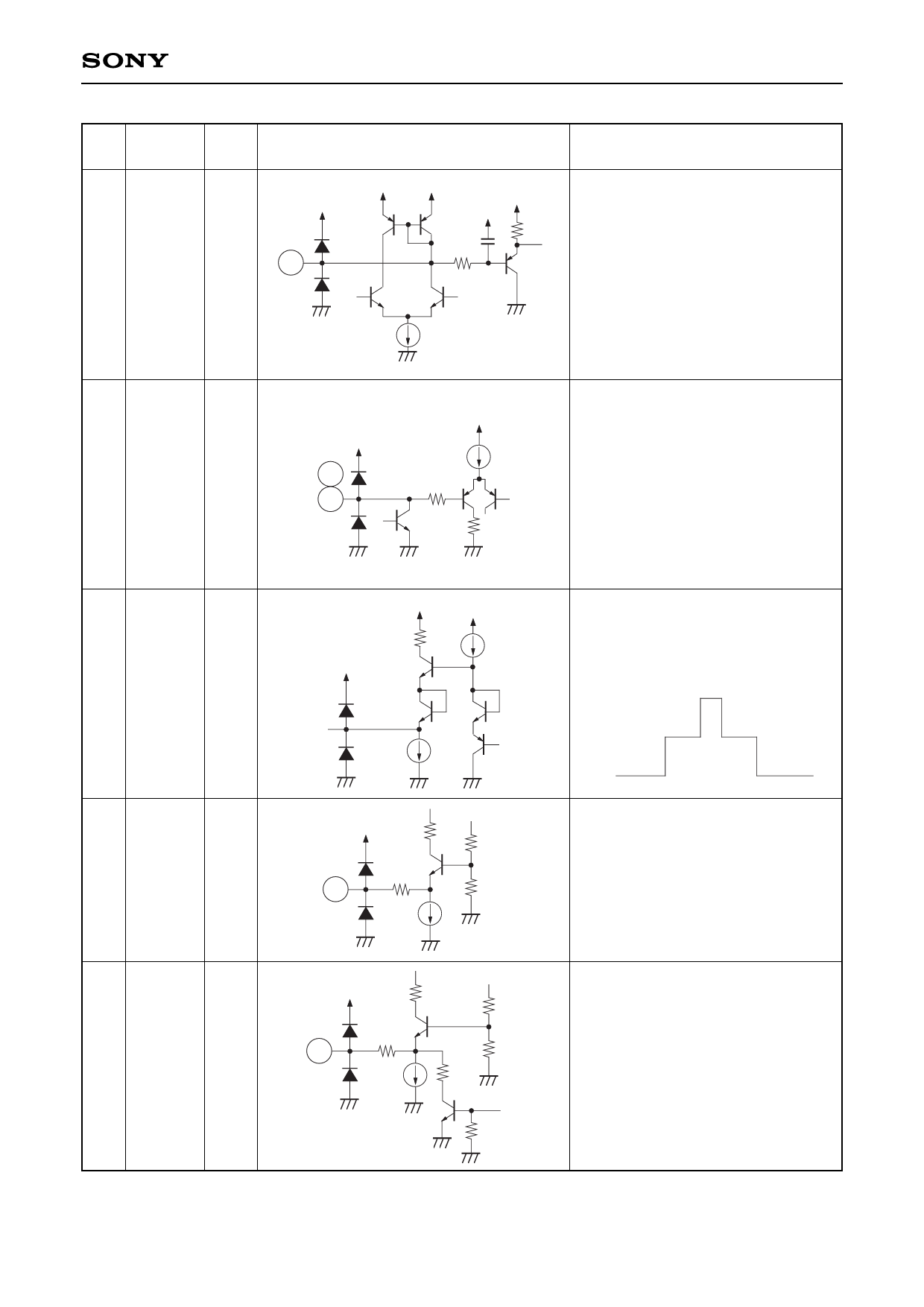

Equivalent circuit

Description

VCC

VCC

39

39 REG 7 V

VCC

VCC

VCC

40 k

4p

1.2 k

Regulator pin for voltage generated

internally from VCC. Connect a

capacitor for stabilization.

50 µA

40 SCL

—

41 SDA

42 SCP

—

43 H SYNC 2.6 V

VCC

40

41

VCC

4k

4k

VCC

1.2 k

VCC

VCC

500 µA

VCC

14 k

24 k

150

43

20 k

10 µA

I2C bus SCL (Serial Clock) and SDA

(Serial Data) pins.

Vilmax = 1.5 V

Vihmin = 3 V

Volmax = 0.4 V

Outputs BGP, HBLK and VBLK as

SCP (Sand Cathle Pulse).

The Typ. waveform is as follows.

BGP

H,VBLK

5.0 V

2.5 V

0.3 V

H sync separation input pin. Inputs a

2 Vp-p video signal via a capacitor

and resistor.

44 V SYNC 3.8 V

VCC

10 k

26 k

150

44

20 µA

31 k

10 k

20 k

—10—

V sync separation input pin. Inputs a

2 Vp-p video signal via a capacitor

and resistor.