TDA9160 View Datasheet(PDF) - Philips Electronics

Part Name

Description

Manufacturer

TDA9160 Datasheet PDF : 27 Pages

| |||

Philips Semiconductors

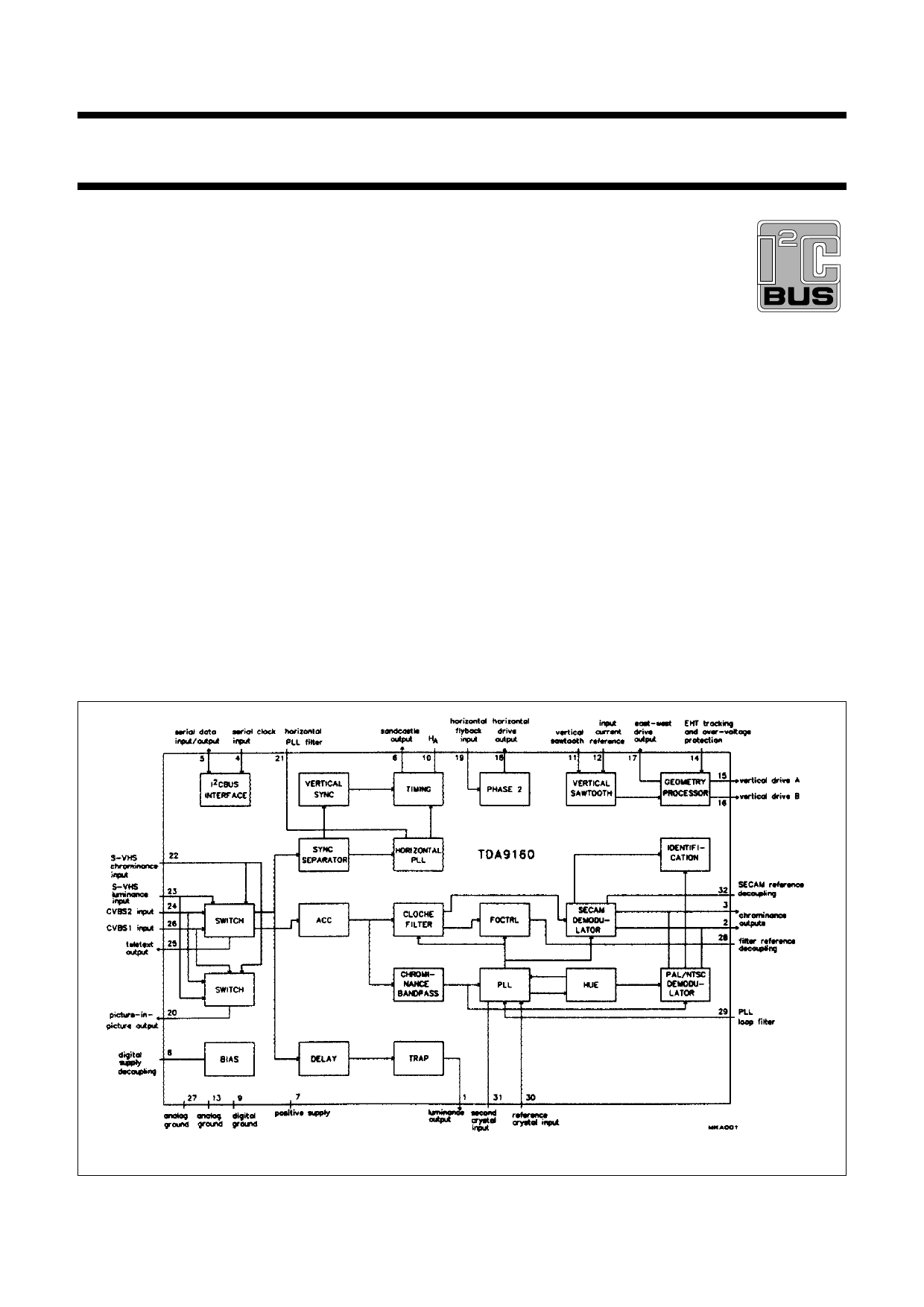

PAL/NTSC/SECAM decoder/sync processor

Preliminary specification

TDA9160

FEATURES

• Multistandard PAL, NTSC and

SECAM

• I2C-bus controlled

• I2C-bus addresses can be selected

by hardware

• Alignment free

• Few external components

• Designed for use with baseband

delay lines

• Integrated video filters

• Horizontal and vertical drive output

• East-West correction drive output

• Two CVBS inputs

• S-VHS input

• Vertical divider system

• HA synchronization pulse

• Two level sandcastle pulse

GENERAL DESCRIPTION

The TDA9160 is an I2C-bus

controlled, alignment-free

PAL/NTSC/SECAM

decoder/processor. The device

contains horizontal and vertical drive

outputs and an east-west correction

drive circuit. The TDA9160 has been

designed for use with baseband

chrominance delay lines and

DC-coupled vertical and east-west

output circuits.

The device has three inputs, two for

CVBS and one for S-VHS. The main

signal is available at the luminance

and colour difference outputs and,

also, at the TXT output

(unprocessed). The signal at the PIP

output can be selected independently

from the main signal.

The circuit provides a drive pulse for

the horizontal output stage, a

differential sawtooth current for the

vertical output stage and an east-west

drive current for the EW output stage.

These signals can be used to provide

geometry correction of the picture. A

two level sandcastle pulse and an HA

pulse are made available for

synchronization purposes

.The I2C-bus address of the TDA9160

can be programmed by hardware.

December 1991

Fig.1 Block diagram.

2