AD5422 View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

AD5422 Datasheet PDF : 44 Pages

| |||

AD5412/AD5422

Data Sheet

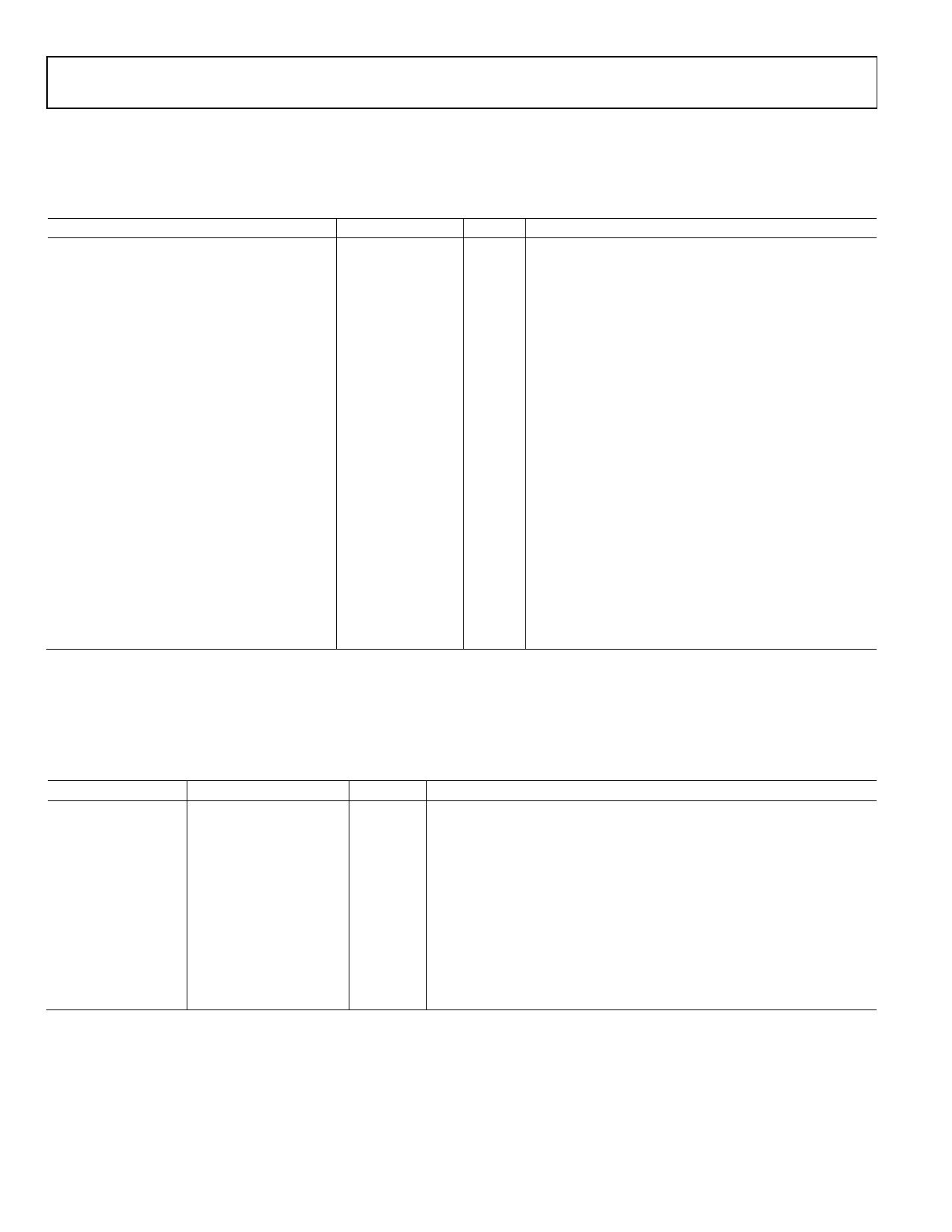

AC PERFORMANCE CHARACTERISTICS

AVDD = 10.8 V to 26.4 V, AVSS = −26.4 V to −3 V/0 V, AVDD + |AVSS| < 52.8 V, GND = 0 V, REFIN = +5 V external; DVCC = 2.7 V to 5.5 V.

VOUT: RLOAD = 1 kΩ, CL = 200 pF, IOUT: RLOAD = 350 Ω; all specifications TMIN to TMAX, unless otherwise noted.

Table 4.

Parameter1

Min Typ Max Unit Test Conditions/Comments

DYNAMIC PERFORMANCE

Voltage Output

Output Voltage Settling Time

25 µs

10 V step to ±0.03 % FSR

32

µs

20 V step to ±0.03 % FSR

18 µs

5 V step to ±0.03 % FSR

8

µs

512 LSB step to ±0.03 % FSR (16-Bit LSB)

Slew Rate

0.8

V/µs

Power-On Glitch Energy

10

nV-sec

Digital-to-Analog Glitch Energy

10

nV-sec

Glitch Impulse Peak Amplitude

20

mV

Digital Feedthrough

1

nV-sec

Output Noise (0.1 Hz to 10 Hz Bandwidth)

0.1

LSB p-p 16-bit LSB

Output Noise (100 kHz Bandwidth)

200

µV rms

1/f Corner Frequency

1

kHz

Output Noise Spectral Density

150

nV/√Hz Measured at 10 kHz, midscale output, 10 V range

AC PSRR

−75

dB

200 mV 50 Hz/60 Hz sine wave superimposed on power

supply voltage

Current Output

Output Current Settling Time

10

µs

16 mA step to 0.1% FSR

40

µs

16 mA step to 0.1% FSR, L = 1 mH

AC PSRR

−75

dB

200 mV 50 Hz/60 Hz sine wave superimposed on power

supply voltage

1 Guaranteed by characterization, not production tested.

TIMING CHARACTERISTICS

AVDD = 10.8 V to 26.4 V, AVSS = −26.4 V to −3 V/0 V, AVDD + |AVSS| < 52.8V, GND = 0 V, REFIN = +5 V external; DVCC = 2.7 V to 5.5 V.

VOUT: RLOAD = 1 kΩ, CL = 200 pF, IOUT: RLOAD = 300 Ω; all specifications TMIN to TMAX, unless otherwise noted.

Table 5.

Parameter1, 2, 3

WRITE MODE

t1

t2

t3

t4

t5

t6

t7

t8

t9

t10

Limit at TMIN, TMAX

33

13

13

13

5

5

5

40

20

5

Unit

ns min

ns min

ns min

ns min

µs min

ns min

ns min

ns min

ns min

µs max

Description

SCLK cycle time

SCLK low time

SCLK high time

LATCH delay time

LATCH high time

Data setup time

Data hold time

LATCH low time

CLEAR pulse width

CLEAR activation time

Rev. O | Page 10 of 44