HC-49/U View Datasheet(PDF) - Sony Semiconductor

Part Name

Description

Manufacturer

HC-49/U Datasheet PDF : 25 Pages

| |||

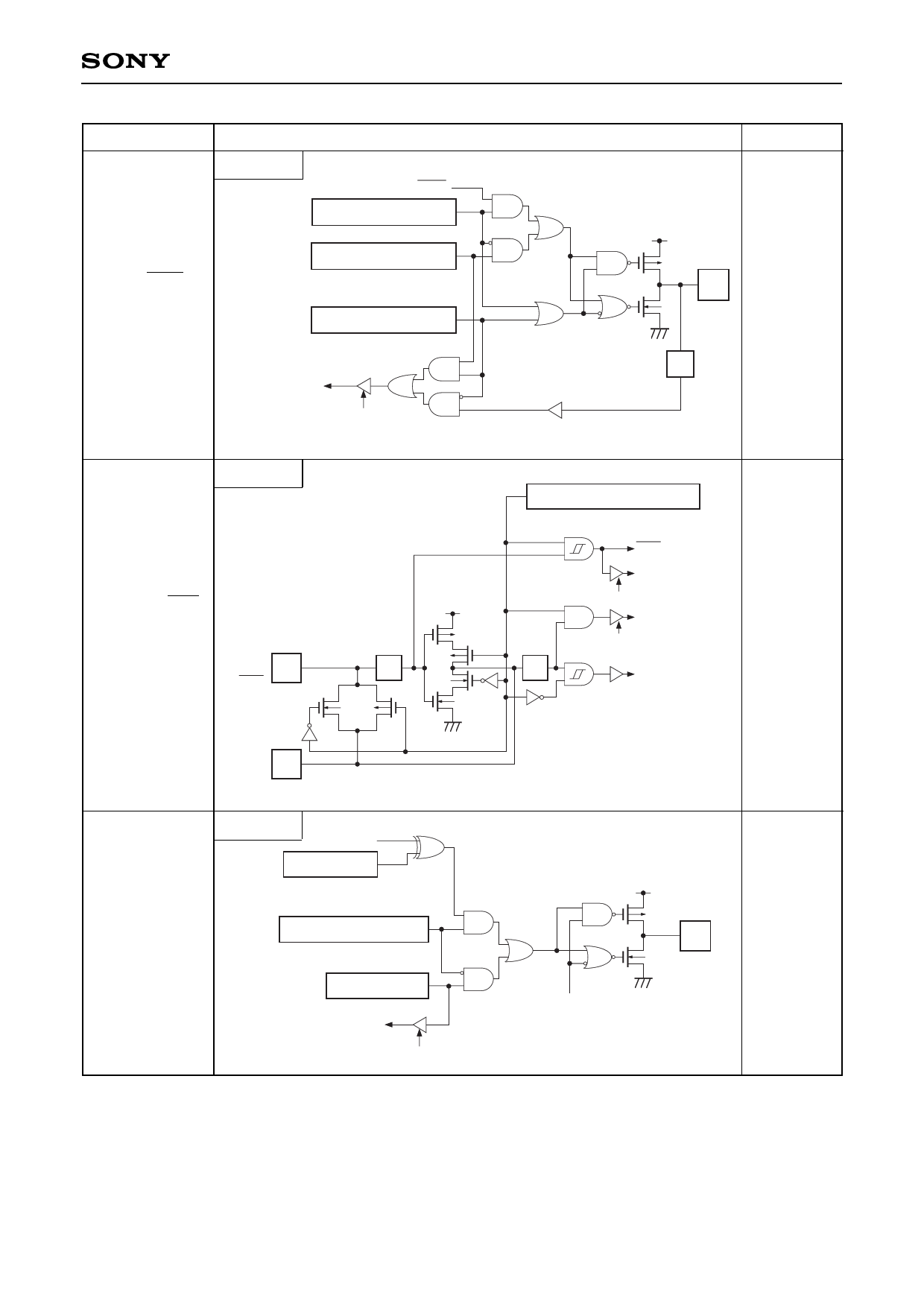

CXP750096/750010, CXP750097/750011

Pin

PE1/PWM

1 pin

Port E

Circuit format

PWM

Port E function selection

“0” after a reset

Port E data

“1” after a reset

Port E direction

“1” after a reset

Internal data bus

RD (Port E)

After a reset

High level

IP

Port E

PE2/TEX/INT0

PE3/TX

PE2/

TEX/

IP

INT0

TEX oscillation circuit control

“1” after a reset

Schmitt input

INT0

Intrenal data bus

RD (Port E)

Internal data bus

RD (Port E)

Schmitt input

IP

Clock input

Oscillation

halted

Port input

2 pins

PE4/YM

PE5/YS

PE6/I

3 pins

PE3/

TX

Port E

YM, YS, I

Output polarity

“0” after a reset

Port E function selection

“1” after a reset

Port E data

Internal data bus

RD (Port E)

Writing data to output polarity

register and port data register

brings output to active.

Hi-Z

– 10 –