ST8024 View Datasheet(PDF) - Sitronix Technology Co., Ltd.

Part Name

Description

Manufacturer

ST8024 Datasheet PDF : 28 Pages

| |||

ST8024

7

FUNCTIONAL DESCRIPTION

7.1

Pin Functions

(Segment mode)

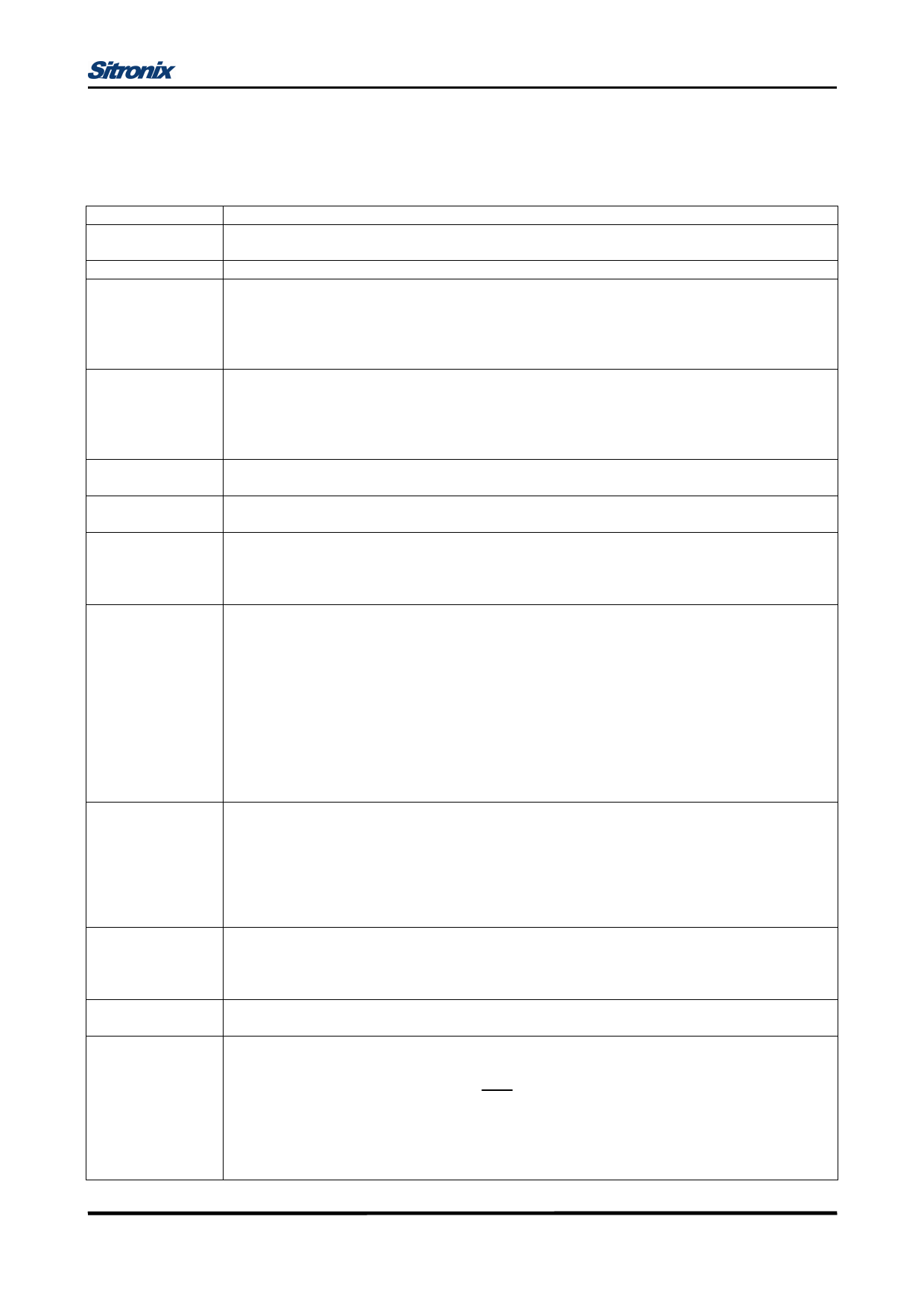

SYMBOL

VDD

VSS

V0L, V0R

V12L, V12R

V43L, V43R

DI7-DI0

XCK

LP

L/R

/DISPOFF

FR

MD

S/C

ElO1, EIO2

FUNCTION

Logic system power supply pin,

Connected to +2.5 to +5.5 V.

Ground pin, connected to 0 V.

Bias power supply pins for LCD drive voltage

Normally use the bias voltages set by a resistor divider

Ensure that voltages are set such that VSS < V43 < V12 < V0.

ViL and ViR (i = 0,12, 43) must connect to an external power supply, and supply regular

voltage which is assigned by specification for each power pin

Input pins for display data

In 4-bit parallel mode, DI3-DI0 are the display data input pins, and DI7-DI4 must be

connected to LGND or VDD.

In 8-bit parallel mode, All DI7-Dl0 pins are the display data input pins.

Refer to section 7.2.2.

Clock input pin for taking display data

Data is read at the falling edge of the clock pulse.

Latch pulse input pin for display data

Data is latched at the falling edge of the clock pulse.

Input pin for selecting the reading direction of display data

When set to LGND level "L", data is read sequentially from Y240 to Y1.

When set to VDD level "H", data is read sequentially from Y1 to Y240.

Refer to section 7.2.2.

Control input pin for output of non-select level

The input signal is level-shifted from logic voltage level to LCD drive voltage level, and

controls the LCD drive circuit.

When set to LGND level "L", the LCD drive output pins (Y1-Y240) are set to level Vss.

When set to "L", the contents of the line latch are reset, but the display data are read in

the data latch regardless of the condition of /DISPOFF. When the /DISPOFF function is

canceled, the driver outputs non-select level (V12 or V43), then outputs the contents of

the data latch at the next falling edge of the LP. At that time, if /DISPOFF removal time

does not correspond to what is shown in AC characteristics, it can not output the

reading data correctly.

Table of truth values is shown in "TRUTH TABLE" in Functional Operations.

AC signal input pin for LCD drive waveform

The input signal is level-shifted from logic voltage level to LCD drive voltage level, and

controls the LCD drive circuit.

Normally it inputs a frame inversion signal.

The LCD drive output pins' output voltage levels can be set using the line latch output

signal and the FR signal.

Table of truth values is shown in "TRUTH TABLE" in Functional Operations.

Mode selection pin

When set to LGND level "L", 8-bit parallel input mode is set.

When set to VDD level "H", 4-bit parallel input mode is set.

Refer to section 7.2.2.

Segment mode/common mode selection pin

When set to VDD level "H", segment mode is set.

Input/output pins for chip selection

When L/R input is at LGND level "L", ElO1 is set for output, and EIO2 is set for input.

When L/R input is at VDD level "H", ElO1 is set for input, and EIO2 is set for output.

During output, set to "H" while LP • XCK is "H" and after 240 bits of data have been

read, set to "L” for one cycle (from falling edge to failing edge of XCK), after which it

returns to "H".

During input, the chip is selected while El is set to "L" after the LP signal is input. The

chip is non-selected after 240 bits of data have been read.

Ver 2.1

Page 7/28

2009/08/19