AD1896YRS View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

AD1896YRS Datasheet PDF : 24 Pages

| |||

AD1896

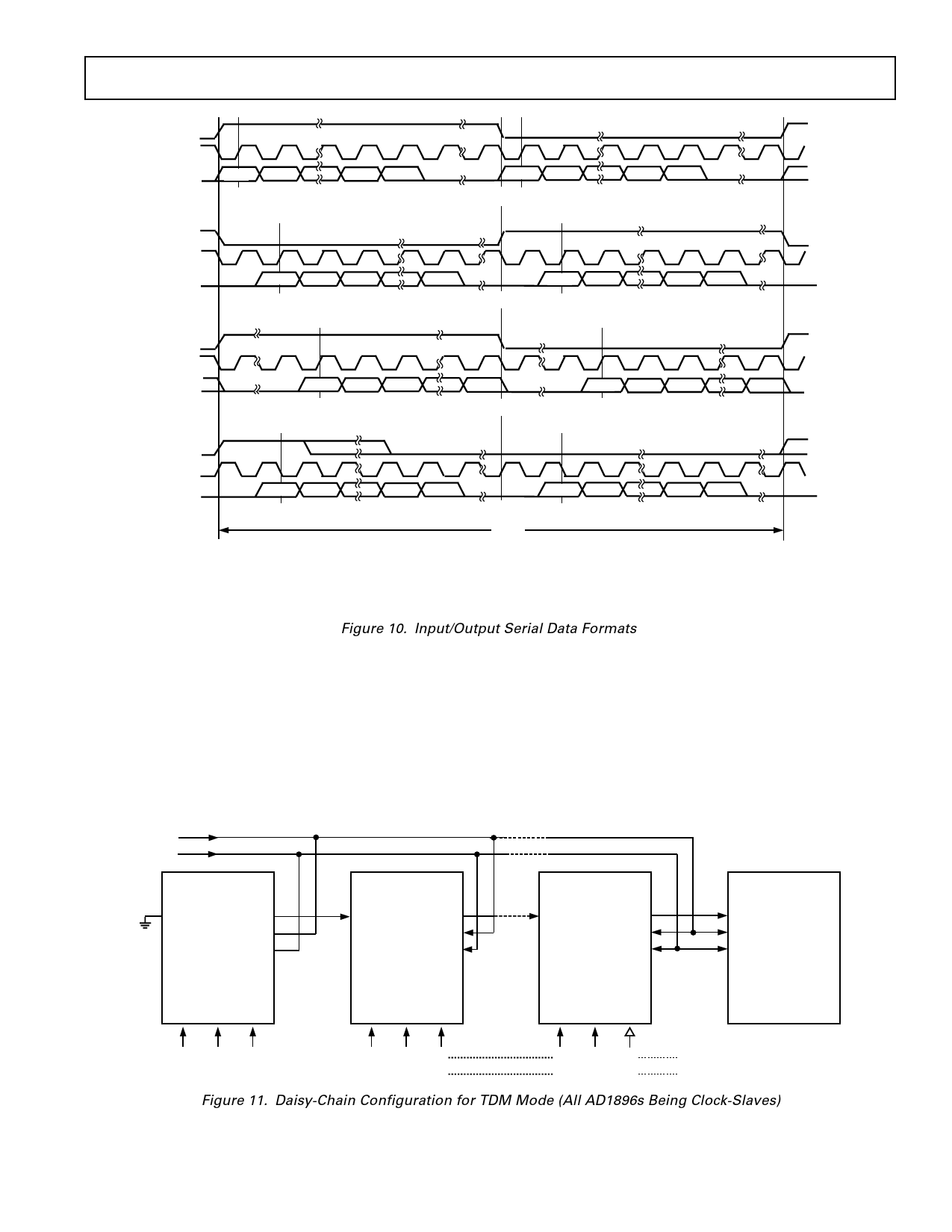

LRCLK

SCLK

SDATA

MMSSBB

LRCLK

SCLK

SDATA

MSB

LEFT CHANNEL

RIGHT CHANNEL

LSB

MSB

LEFT JUSTIFIED MODE – 16 TO 24 BITS PER CHANNEL

LSB

LEFT CHANNEL

LSB

MMSSBB

I2S MODE – 16 TO 24 BITS PER CHANNEL

RIGHT CHANNEL

LSB

LRCLK

SCLK

SDATA

LEFT CHANNEL

RIGHT CHANNEL

MSB

LSB

MSB

RIGHT JUSTIFIED MODE – SELECT NUMBER OF BITS PER CHANNEL

LSB

LRCLK

SCLK

SDATA

MSB

LSB

MSB

TDM MODE – 16 TO 24 BITS PER CHANNEL

1/fs

NOTES:

1. LRCLK NORMALLY OPERATES AT ASSOCIATIVE INPUT OR OUTPUT SAMPLE FREQUENCY (fs)

2. SCLK FREQUENCY IS NORMALLY 64 ؋ LRCLK EXCEPT FOR TDM MODE WHICH IS N ؋ 64 ؋ fs,

WHERE N = NUMBER OF STEREO CHANNELS IN THE TDM CHAIN, IN MASTER MODE N = 4

3. PLEASE NOTE THAT 8 BITS OF EACH 32-BIT SUBFRAME ARE USED FOR TRANSMITTING

MATCHED-PHASE MODE DATA. PLEASE REFER TO FIGURE 14.

LSB

Figure 10. Input/Output Serial Data Formats

TDM MODE APPLICATION

In TDM mode, several AD1896s can be daisy-chained together

and connected to the serial input port of a SHARC® DSP. The

AD1896 contains a 64-bit parallel load shift register. When the

LRCLK_O pulse arrives, each AD1896 parallel loads its left and

right data into the 64-bit shift register. The input to the shift

register is connected to TDM_IN while the output is connected

to SDATA_O. By connecting the SDATA_O to the TDM_IN

of the next AD1896, a large shift register is created which is

clocked by SCLK_O.

The number of AD1896s that can be daisy-chained together is

limited by the maximum frequency of SCLK_O, which is about

25 MHz. For example, if the output sample rate, fS, is 48 kHz,

up to eight AD1896s could be connected since 512 × fS is less

than 25 MHz. In Master/TDM Mode, the number of AD1896s

that can be daisy-chained is fixed to four.

LRCLK

SCLK

AD1896

TDM_IN

SDATA_O

LRCLK_O

SCLK_O

AD1896

TDM_IN

SDATA_O

LRCLK_O

SCLK_O

AD1896

TDM_IN

SDATA_O

LRCLK_O

SCLK_O

SHARC

DSP

DR0

RFS0

RCLK0

PHASE-MASTER

M2 M1 M0

SLAVE-1

M2 M1 M0

SLAVE-n

M2 M1 M0

0

0

0

0

0

0

1

0

0

0

0

0

1

0

0

STANDARD MODE

MATCHED-PHASE MODE

Figure 11. Daisy-Chain Configuration for TDM Mode (All AD1896s Being Clock-Slaves)

SHARC is a registered trademark of Analog Devices, Inc.

REV. 0

–21–