M2S56D20AKT View Datasheet(PDF) - Elpida Memory, Inc

Part Name

Description

Manufacturer

M2S56D20AKT Datasheet PDF : 41 Pages

| |||

DDR SDRAM

E0338M10 (Ver.1.0)

(Previous Rev.1.54E)

Jan. '03 CP(K)

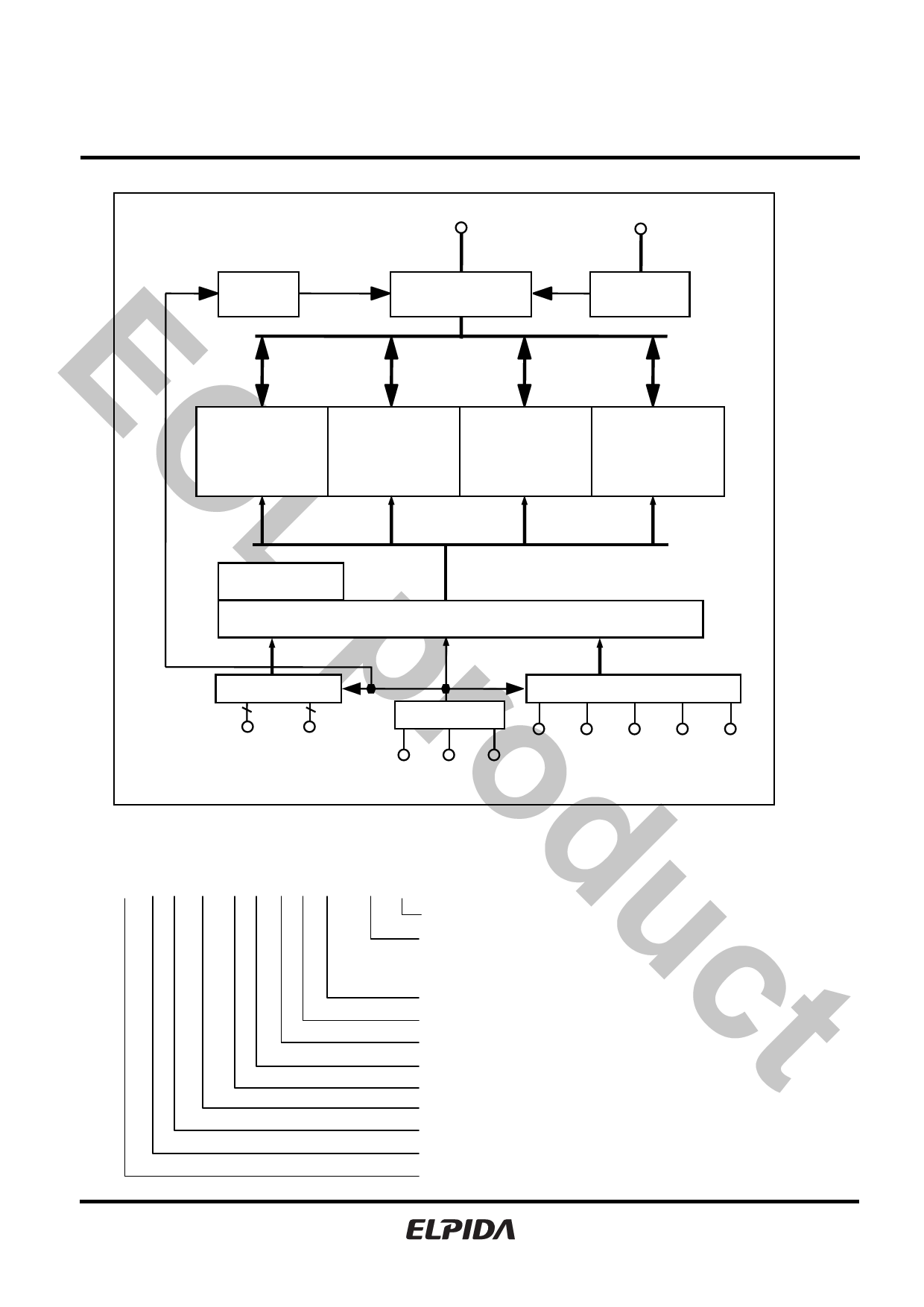

BLOCK DIAGRAM

DLL

M2S56D20/ 30/ 40ATP

M2S56D20/ 30/ 40AKT

256M Double Data Rate Synchronous DRAM

DQ0 - 15

UDQS,LDQS

I/O Buffer

QS Buffer

Memory

Array

Bank #0

Memory

Array

Bank #1

Memory

Array

Bank #2

Memory

Array

Bank #3

Mode Register

Control Circuitry

Address Buffer

A0-12 BA0,1

Clock Buffer

Control Signal Buffer

/CS /RAS /CAS /WE UDM,

CLK /CLK CKE

LDM

TYPE DESIGNATION CODE

This rule is applied to only Synchronous DRAM family.

M 2 S 56 D 3 0 A KT – 60 UL

Power Grade UL/U: Ultra Low power L: Low power, Blank: standard

Speed Grade 75: 133MHz@CL=2.5,100MHz@CL=2.0 (DDR266B)

75A: 133MHz@CL=2.5,133MHz@CL=2.0 (DDR266A)

60: 166MHz@CL=2.5,133MHz@CL=2.0 (DDR333B)

Package Type TP: TSOP(II), KT: sTSOP(Small TSOP)

Process Generation

Function Reserved for Future Use

Organization 2 n 2: x4, 3: x8, 4: x16

DDR Synchronous DRAM

Density 56: 256M bits

Interface V:LVTTL, S:SSTL_3, _2

Memory Style (DRAM)

Mitsubishi Main Designation

6