BT16501ADL View Datasheet(PDF) - Philips Electronics

Part Name

Description

Manufacturer

BT16501ADL Datasheet PDF : 13 Pages

| |||

Philips Semiconductors

18-bit universal bus transceiver (3-State)

Product specification

74ABT16501A

74ABTH16501A

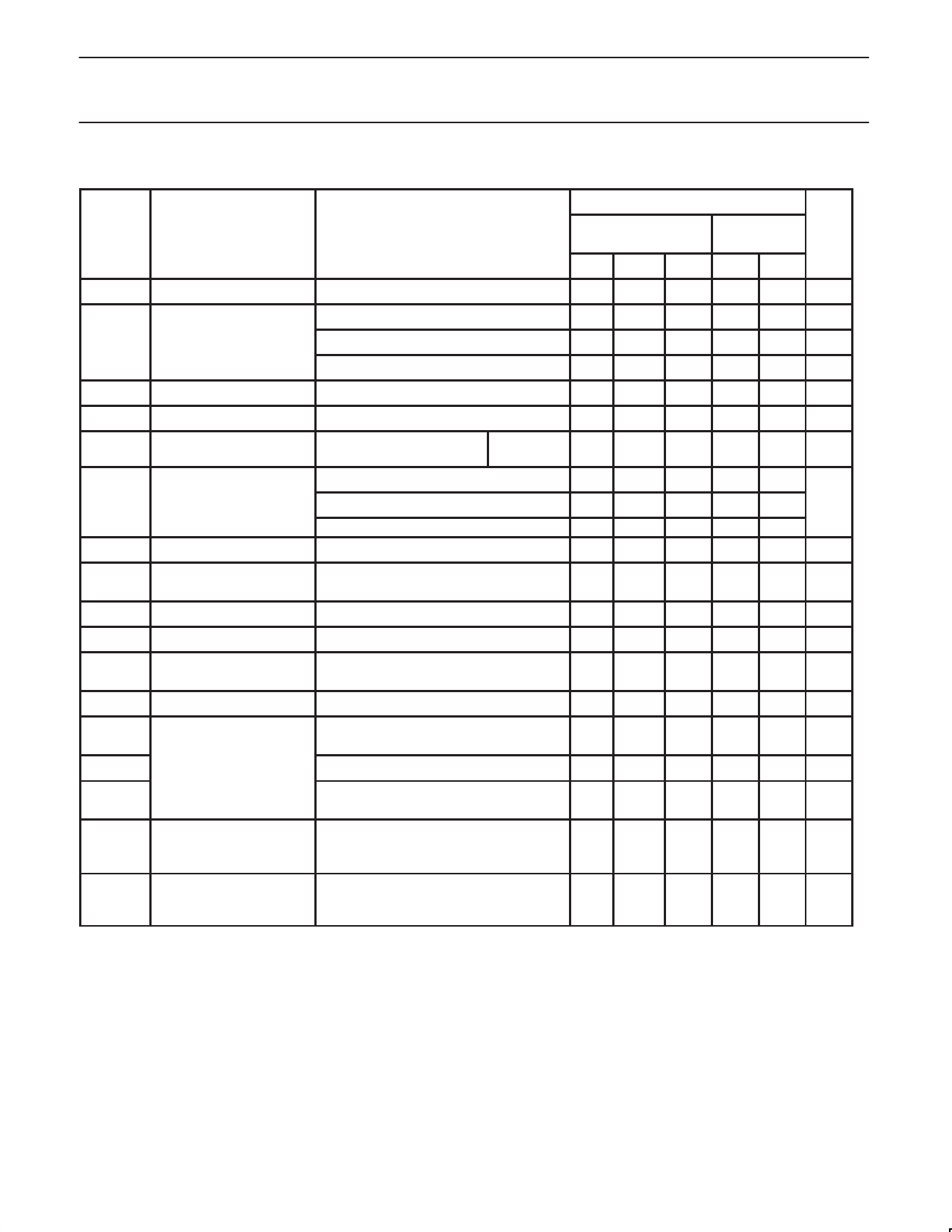

DC ELECTRICAL CHARACTERISTICS

LIMITS

SYMBOL

PARAMETER

TEST CONDITIONS

Tamb = +25°C

Tamb = –40°C

to +85°C

UNIT

MIN TYP MAX MIN MAX

VIK

Input clamp voltage

VCC = 4.5V; IIK = –18mA

–0.8 –1.2

–1.2 V

VCC = 4.5V; IOH = –3mA; VI = VIL or VIH

2.5 2.9

2.5

V

VOH

High-level output voltage

VCC = 5.0V; IOH = –3mA; VI = VIL or VIH

3.0 4.0

3.0

V

VCC = 4.5V; IOH = –32mA; VI = VIL or VIH

2.0 2.4

2.0

V

VOL

Low-level output voltage

VCC = 4.5V; IOL = 64mA; VI = VIL or VIH

0.35 0.55

0.55 V

VRST Power-up output voltage3 VCC = 5.5V; IO = 1mA; VI = GND or VCC

0.13 0.55

0.55 V

II

Input leakage

current

VCC = 5.5V; VI = GND or

5.5V

Control pins

"0.01 ±1.0

±1.0 µA

IHOLD

IOFF

Bus Hold current A and B

ports5 74ABTH16501A

Power-off leakage current

VCC = 4.5V; VI = 0.8V

VCC = 4.5V; VI = 2.0V

VCC = 5.5V; VI = 0 to 5.5V

VCC = 0.0V; VO or VI ≤ 4.5V

35

35

–75

–75

µA

±800

"2 ±100

±100 µA

IPU/PD

Power-up/down 3-State

output current4

VCC = 2.1V; VO = 0.0V or VCC;

VI = GND or VCC; VOE = Don’t care

"2 ±50

±50 µA

IIH + IOZH 3-State output High current VCC = 5.5V; VO = 5.5V; VI = VIL or VIH

1.0

10

10

µA

IIL + IOZL 3-State output Low current VCC = 5.5V; VO = 0.0V; VI = VIL or VIH

–1.0 –10

–10 µA

ICEX

Output High leakage

current

VCC = 5.5V; VO = 5.5V; VI = GND or VCC

2.0

50

50

µA

IO

Output current1

VCC = 5.5V; VO = 2.5V

–50 –80 –180 –50 –180 mA

ICCH

VCC = 5.5V; Outputs High, VI = GND or

VCC

0.5

2

2

mA

ICCL Quiescent supply current VCC = 5.5V; Outputs Low, VI = GND or VCC

9

19

19 mA

ICCZ

VCC = 5.5V; Outputs 3–State;

VI = GND or VCC

0.5

2

2

mA

∆ICC

Additional supply current

per input pin2

74ABT16501A

VCC = 5.5V; one input at 3.4V,

other inputs at VCC or GND

5.0

50

50

µA

∆ICC

Additional supply current

per input pin2

74ABTH16501A

VCC = 5.5V; one input at 3.4V,

other inputs at VCC or GND

200 500

500 µA

NOTES:

1. Not more than one output should be tested at a time, and the duration of the test should not exceed one second.

2. This is the increase in supply current for each input at 3.4V.

3. For valid test results, data must not be loaded into the flip-flops (or latches) after applying the power.

4. This parameter is valid for any VCC between 0V and 2.1V, with a transition time of up to 10msec. From VCC = 2.1V to VCC = 5V ± 10% a

transition time of up to 100µsec is permitted.

5. This is the bus hold overdrive current required to force the input to the opposite logic state.

1998 Feb 27

8