M2V56S20ATP-7 View Datasheet(PDF) - MITSUBISHI ELECTRIC

Part Name

Description

Manufacturer

M2V56S20ATP-7 Datasheet PDF : 51 Pages

| |||

SDRAM (Rev.1.31)

Single Data Rate

Apr. '02

MITSUBISHI LSIs

M2V56S20/ 30/ 40 ATP

M2V56S20/ 30/ 40 AKT

256M Synchronous DRAM

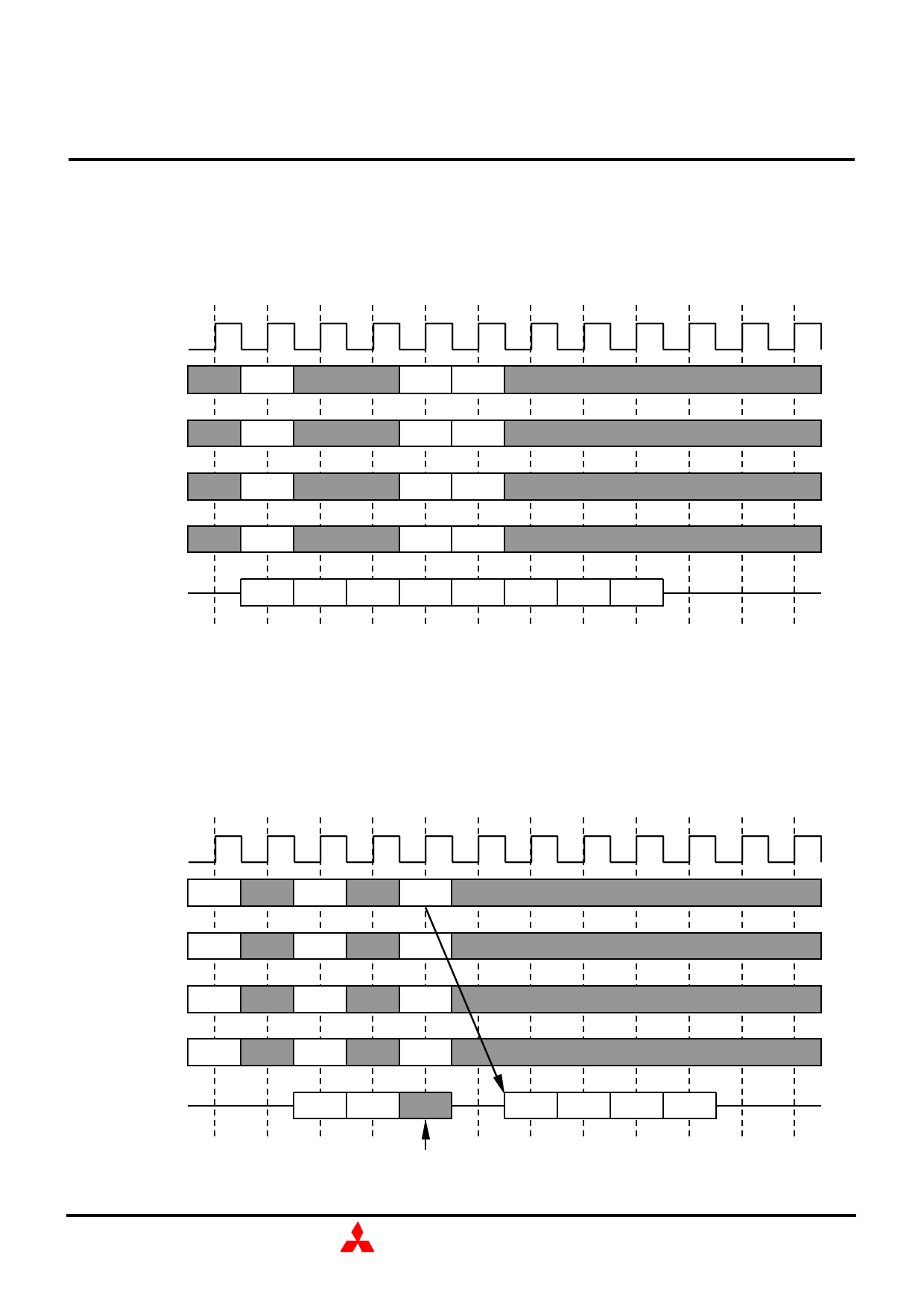

[ Write Interrupted by Write ]

Burst write operation can be interrupted by new write of any active bank. Random column access is

allowed. WRITE to WRITE interval is minimum 1 CLK.

CLK

Command

A0-9,11-12

A10

BA0-1

DQ

Write Interrupted by Write (BL=4)

Write

Write Write

Ya

Yb Yc

0

0

0

00

00 10

Da0 Da1 Da2 Db0 Dc0 Dc1 Dc2 Dc3

[ Write Interrupted by Read ]

Burst write operation can be interrupted by read of any active bank. Random column access is allowed.

WRITE to READ interval is minimum 1 CLK. The input data on DQ at the interrupting READ cycle is

"Don't Care".

CLK

Command ACT

A0-9,11-12 Xa

A10 Xa

BA0-1 00

DQ

Write Interrupted by Read (CL=2, BL=4)

Write

READ

Ya

Yb

0

0

00

00

Da0 Da1

Qb0 Qb1 Qb2 Qb3

don't care

MITSUBISHI ELECTRIC

23