# EZ-USB® FX3S SuperSpeed USB Controller

#### **Features**

- Universal serial bus (USB) integration

- □ USB 3.0 and USB 2.0 peripherals compliant with USB 3.0 specification 1.0

- □ 5-Gbps USB 3.0 PHY compliant with PIPE 3.0

- □ High-speed On-The-Go (HS-OTG) host and peripheral compliant with OTG Supplement Version 2.0

- □ Thirty-two physical endpoints

- □ Support for battery charging Spec 1.1 and accessory charger adaptor (ACA) detection

- General Programmable Interface (GPIF™ II)

- □ Programmable 100-MHz GPIF II enables connectivity to a wide range of external devices

- □ 8- and 16-bit data bus

- As many as 16 configurable control signals

- Mass storage support

- □ SD 3.0 (SDXC) UHS-1

- □ eMMC 4.41

- ☐ Two ports that can support memory card sizes up to 2TB

- System I/O expansion with two secure digital I/O (SDIO) ports

- Native USB-attached storage (UAS), mass-storage class (MSC), human interface device (HID), full, and Turbo-MTP™ support

- Fully accessible 32-bit CPU

- □ ARM926EJ core with 200-MHz operation

- □ 512-KB or 256-KB embedded SRAM

- Additional connectivity to the following peripherals

- □ I<sup>2</sup>C master controller at 1 MHz

- □ I2S master (transmitter only) at sampling frequencies of 32 kHz, 44.1 kHz, and 48 kHz

- □ UART support of up to 4 Mbps

- □ SPI master at 33 MHz

- Selectable clock input frequencies

- □ 19.2, 26, 38.4, and 52 MHz

- □ 19.2-MHz crystal input support

- Ultra low-power in core power-down mode

- □ Less than 60 µA with VBATT on

- □ 20 µA with VBATT off

- Independent power domains for core and I/O

- □ Core operation at 1.2 V

- □ I2S, UART, and SPI operation at 1.8 to 3.3 V

- □ I<sup>2</sup>C operation at 1.2 V

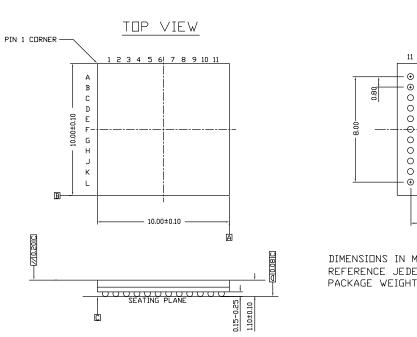

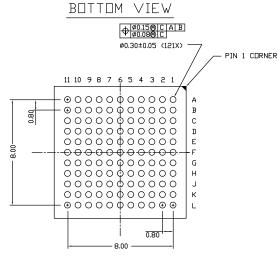

- 10- × 10-mm, 0.8-mm pitch Pb-free ball grid array (BGA) package

- EZ-USB<sup>®</sup> software and development kit (DVK) for easy code development

# **Applications**

- Digital video camcorders

- Digital still cameras

- Printers

- Scanners

- Video capture cards

- Test and measurement equipment

- Surveillance cameras

- Personal navigation devices

- Medical imaging devices

- Video IP phones

- Portable media players

- Industrial cameras

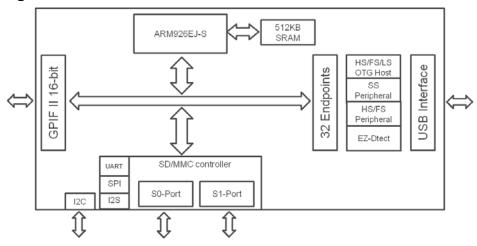

# Logic Block Diagram

# Contents

| Functional Overview                   | 3  |

|---------------------------------------|----|

| Application Examples                  | 3  |

| USB Interface                         |    |

| OTG                                   |    |

| ReNumeration                          |    |

| EZ-Dtect                              | 5  |

| VBUS Overvoltage Protection           | 5  |

| Carkit UART Mode                      | 5  |

| Host Processor Interface (P-Port)     | 6  |

| GPIF II                               |    |

| Slave FIFO interface                  | 6  |

| Asynchronous SRAM                     | 6  |

| Asynchronous Address/Data Multiplexed |    |

| Synchronous ADMux Interface           |    |

| Processor MMC (PMMC) Slave Interface  | 7  |

| CPU                                   | 8  |

| Storage Port (S-Port)                 | 8  |

| SD/MMC Clock Stop                     |    |

| SD CLK Output Clock Stop              |    |

| Card Insertion and Removal Detection  |    |

| Write Protection (WP)                 | 9  |

| SDIO Interrupt                        | 9  |

| SDIO Read-Wait Feature                | 9  |

| JTAG Interface                        | 9  |

| Other Interfaces                      | 9  |

| UART Interface                        |    |

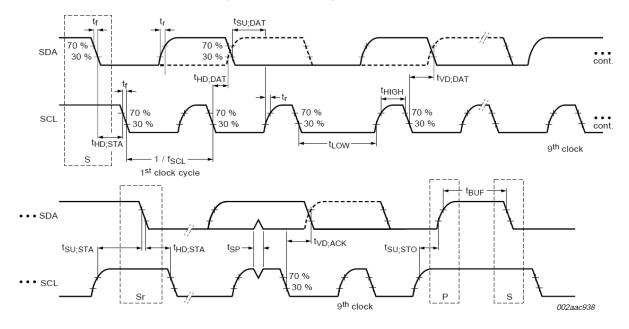

| I2C Interface                         |    |

| I2S Interface                         |    |

| SPI Interface                         | 9  |

| Boot Options                          |    |

| Reset                                 |    |

| Hard Reset                            |    |

| Soft Reset                            |    |

| Clocking                              |    |

| 32-kHz Watchdog Timer Clock Input     |    |

| Power                                 |    |

| Power Modes                           |    |

| I OMELINIORES                         | 12 |

| Configuration Options15                   |

|-------------------------------------------|

| Digital I/Os15                            |

| GPIOs15                                   |

| System-level ESD15                        |

| Pin Description16                         |

| Absolute Maximum Ratings20                |

| Operating Conditions20                    |

| AC Timing Parameters22                    |

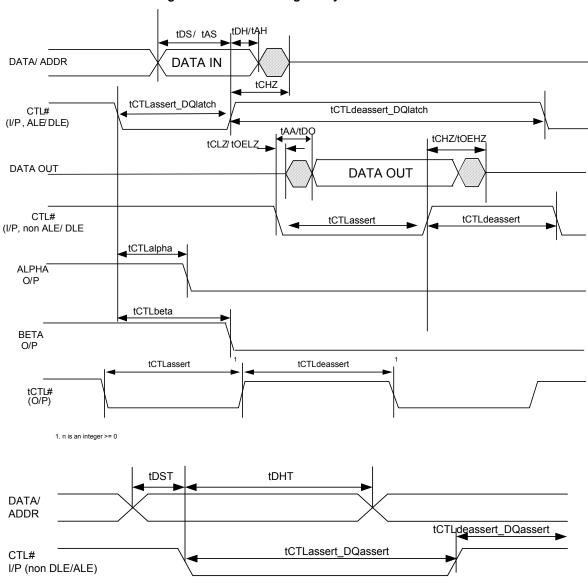

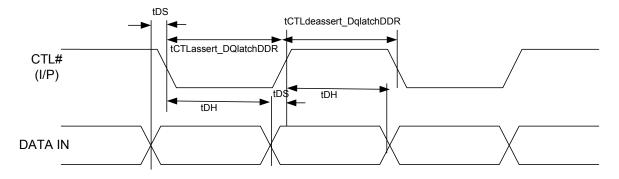

| GPIF II Timing22                          |

| Asynchronous SRAM Timing25                |

| ADMux Timing for Asynchronous Access28    |

| Synchronous ADMux Timing30                |

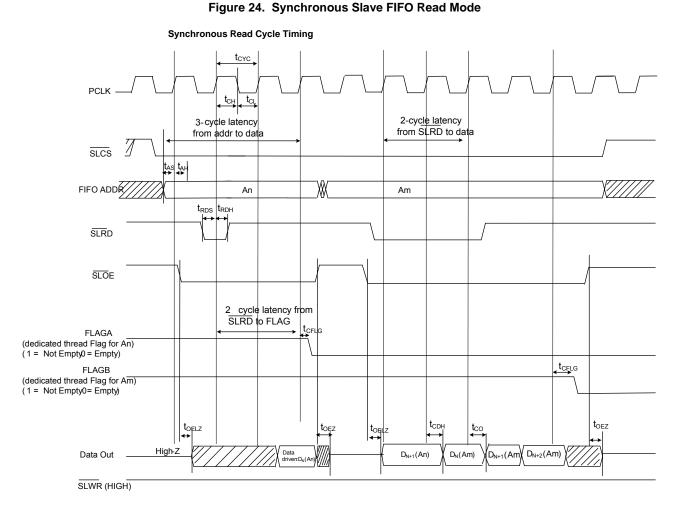

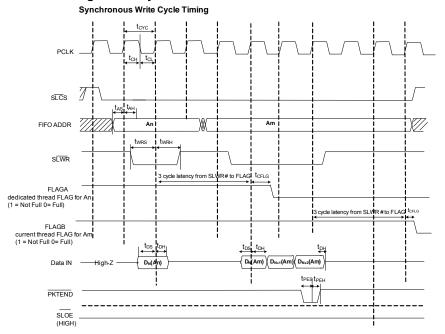

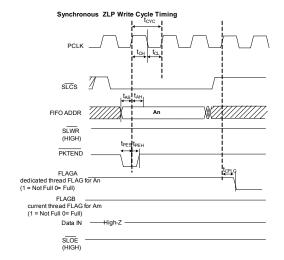

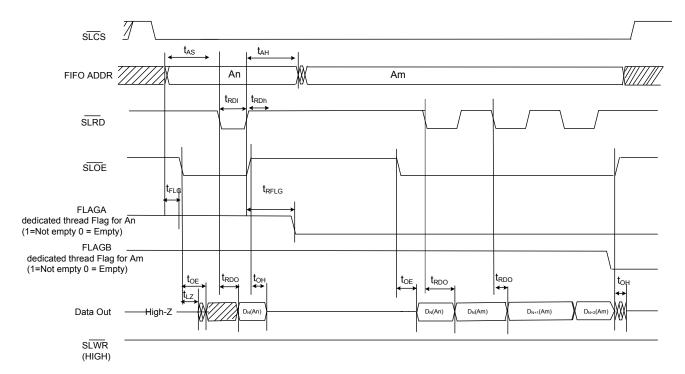

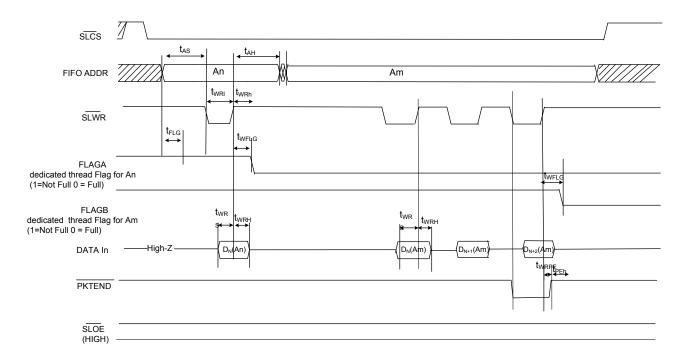

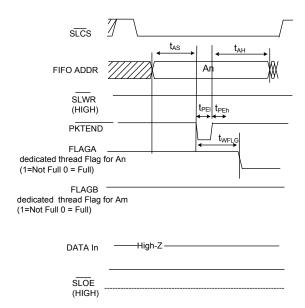

| Slave FIFO Interface33                    |

| Synchronous Slave FIFO                    |

| Write Sequence Description34              |

| Asynchronous Slave FIFO                   |

| Read Sequence Description35               |

| Asynchronous Slave FIFO                   |

| Write Sequence Description36              |

| Storage Port Timing38                     |

| Serial Peripherals Timing41               |

| Reset Sequence45                          |

| Package Diagram47                         |

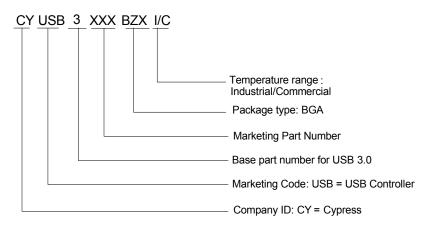

| Ordering Information48                    |

| Ordering Code Definitions48               |

| Acronyms49                                |

| Document Conventions49                    |

| Units of Measure49                        |

| Document History Page50                   |

| Sales, Solutions, and Legal Information50 |

| Worldwide Sales and Design Support50      |

| Products50                                |

| PSoC Solutions50                          |

### **Functional Overview**

Cypress's EZ-USB FX3S is the next-generation USB 3.0 peripheral controller, providing integrated and flexible features. FX3S has a fully configurable, parallel, general programmable interface called GPIF II, which can connect to any processor, ASIC, or FPGA. GPIF II is an enhanced version of the GPIF in FX2LP, Cypress's flagship USB 2.0 product. It provides easy and glueless connectivity to popular interfaces, such as asynchronous SRAM, asynchronous and synchronous address data multiplexed interfaces, and parallel ATA. FX3S has integrated the USB 3.0 and USB 2.0 physical layers (PHYs) along with a 32-bit ARM926EJ-S microprocessor for powerful data processing and for building custom applications. It implements an architecture that enables 185-MBps data transfer from GPIF II to the USB interface.

FX3S features an integrated storage controller and can support up to two independent mass storage devices on its storage ports. It can support SD 3.0 and eMMC 4.41 memory cards. It can also support SDIO on these ports.

An integrated USB 2.0 OTG controller enables applications in which FX3S may serve dual roles; for example, EZ-USB FX3S may function as an OTG Host to MSC as well as HID-class devices. FX3S contains 512 KB or 256 KB of on-chip SRAM for code and data. EZ-USB FX3S also provides interfaces to connect to serial peripherals such as UART, SPI, I<sup>2</sup>C, and I2S. FX3S comes with application development tools. The software development kit comes with application examples for accelerating time to market.

FX3S complies with the USB 3.0 v1.0 specification and is also backward compatible with USB 2.0. It also complies with the Battery Charging Specification v1.1 and USB 2.0 OTG Specification v2.0.

# **Application Examples**

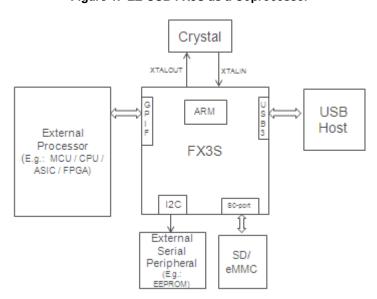

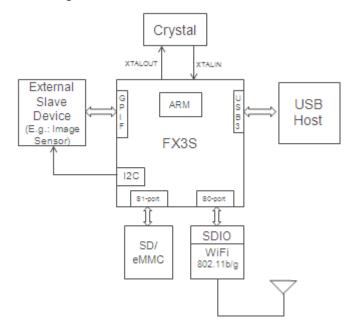

In a typical application (see Figure 1), FX3S functions as a coprocessor and connects to an external processor, which manages system-level functions. Figure 2 shows a typical application diagram when FX3S functions as the main processor.

Figure 1. EZ-USB FX3S as a Coprocessor

#### Note

Document Number: 001-84160 Rev. \*B

<sup>1.</sup> Assuming that GPIF II is configured for a 16-bit data bus (available with certain part numbers; see Ordering Information on page 48), synchronous interface operating at 100 MHz. This number also includes protocol overheads.

Figure 2. EZ-USB FX3S as Main Processor

### **USB** Interface

FX3S complies with the following specifications and supports the following features:

- Supports USB peripheral functionality compliant with the USB 3.0 Specification Revision 1.0 and is also backward compatible with the USB 2.0 Specification.

- Complies with OTG Supplement Revision 2.0. It supports High-Speed, Full-Speed, and Low-Speed OTG dual-role device capability. As a peripheral, FX3S is capable of SuperSpeed, High-Speed, and Full-Speed. As a host, it is capable of High-Speed, Full-Speed, and Low-Speed.

- Supports Carkit Pass-Through UART functionality on USB D+/D- lines based on the CEA-936A specification.

- Supports up to 16 IN and 16 OUT endpoints.

- Supports the USB 3.0 Streams feature. It also supports USB Attached SCSI (UAS) device-class to optimize mass-storage access performance.

- As a USB peripheral, FX3S supports UAS, USB Video Class (UVC), Mass Storage Class (MSC), and Media Transfer Protocol (MTP) USB peripheral classes. As a USB peripheral, all other device classes are supported only in the pass-through mode when handled entirely by a host processor external to the device.

- As an OTG host, FX3S supports MSC and HID device classes. **Note** When the USB port is not in use, disable the PHY and transceiver to save power.

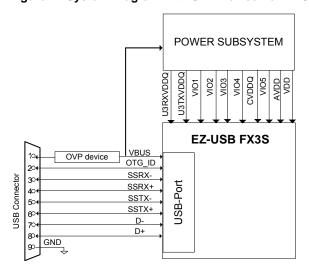

Figure 3. USB Interface Signals

#### **OTG**

FX3S is compliant with the OTG Specification Revision 2.0. In the OTG mode, FX3S supports both A and B device modes and supports Control, Interrupt, Bulk, and Isochronous data transfers.

FX3S requires an external charge pump (either standalone or integrated into a PMIC) to power VBUS in the OTG A-device mode.

The Target Peripheral List for OTG host implementation consists of MSC- and HID-class devices.

FX3S does not support Attach Detection Protocol (ADP).

### **OTG Connectivity**

In OTG mode, FX3S can be configured to be an A, B, or dual-role device. It can connect to the following:

- ACA device

- Targeted USB peripheral

- SRP-capable USB peripheral

- HNP-capable USB peripheral

- OTG host

- HNP-capable host

- OTG device

#### ReNumeration

Because of FX3S's soft configuration, one chip can take on the identities of multiple distinct USB devices.

When first plugged into USB, FX3S enumerates automatically with the Cypress Vendor ID (0x04B4) and downloads firmware and USB descriptors over the USB interface. The downloaded firmware executes an electrical disconnect and connect. FX3S enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration, happens instantly when the device is plugged in.

#### **EZ-Dtect**

FX3S supports USB Charger and accessory detection (EZ-Dtect). The charger detection mechanism complies with the Battery Charging Specification Revision 1.1. In addition to supporting this version of the specification, FX3S also provides hardware support to detect the resistance values on the ID pin.

FX3S can detect the following resistance ranges:

- $\blacksquare$  Less than 10  $\Omega$

- Less than 1 kO

- $\blacksquare$  65 k $\Omega$  to 72 k $\Omega$

- 35 kΩ to 39 kΩ

- 99.96 k $\Omega$  to 104.4 k $\Omega$  (102 k $\Omega \pm 2\%$ )

- 119 k $\Omega$  to 132 k $\Omega$

- Higher than 220 kΩ

- 431.2 k $\Omega$  to 448.8 k $\Omega$  (440 k $\Omega \pm$  2%)

FX3S's charger detects a dedicated wall charger, Host/Hub charger, and Host/Hub.

#### **VBUS Overvoltage Protection**

The maximum input voltage on FX3S's VBUS pin is 6 V. A charger can supply up to 9 V on VBUS. In this case, an external overvoltage protection (OVP) device is required to protect FX3S from damage on VBUS. Figure 4 shows the system application diagram with an OVP device connected on VBUS. Refer to Table 7 for the operating range of VBUS and VBATT.

Figure 4. System Diagram with OVP Device For VBUS

#### **Carkit UART Mode**

The USB interface supports the Carkit UART mode (UART over D+/D-) for non-USB serial data transfer. This mode is based on the CEA-936A specification.

In the Carkit UART mode, the output signaling voltage is 3.3 V. When configured for the Carkit UART mode, TXD of UART (output) is mapped to the D– line, and RXD of UART (input) is mapped to the D+ line.

In the Carkit UART mode, FX3S disables the USB transceiver and D+ and D- pins serve as pass-through pins to connect to the UART of the host processor. The Carkit UART signals may be routed to the GPIF II interface or to GPIO[48] and GPIO[49], as shown in Figure 5 on page 6.

In this mode, FX3S supports a rate of up to 9600 bps.

Carkit UART Pass-through **UART TXD** RXD(DP) TXD Carkit UART Pass-through UART RXD -Port RXD Interface on GPIF II DP **USB PHY** DM GPIQ[48] TXD(DM) (UART\_TX) Carkit UART Pass-through GPI0[49] Interface on GPIOs (UART RX)

Figure 5. Carkit UART Pass-through Block Diagram

# **Host Processor Interface (P-Port)**

A configurable interface enables FX3S to communicate with various devices such as Sensor, FPGA, Host Processor, or a Bridge chip. FX3S supports the following P-Port interfaces.

- GPIF II (16-bit)

- Slave FIFO Interface

- 16-bit Asynchronous SRAM Interface

- 16-bit Asynchronous address/data multiplexed (ADMux) Interface

- 16-bit Synchronous address/data multiplexed (ADMux) Interface

- Processor MMC slave Interface compatible with MMC System specification, MMCA Technical Committee, Version 4.2 with eMMC 4.3 and 4.4 Pass-Through boot

The following sections describe these P-Port interfaces.

#### **GPIF II**

The high-performance GPIF II interface enables functionality similar to, but more advanced than, FX2LP's GPIF and Slave FIFO interfaces.

The GPIF II is a programmable state machine that enables a flexible interface that may function either as a master or slave in industry-standard or proprietary interfaces. Both parallel and serial interfaces may be implemented with GPIF II.

Here are a list of GPIF II features:

- Functions as master or slave

- Provides 256 firmware programmable states

- Supports 8-bit and 16-bit parallel data bus

- Enables interface frequencies up to 100 MHz

- Supports 16 configurable control pins when a 16/8 data bus is used. All control pins can be either input/output or bi-directional.

GPIF II state transitions are based on control input signals. The control output signals are driven as a result of the GPIF II state transitions. The INT# output signal can be controlled by GPIF II. Refer to the GPIFII Designer tool. The GPIF II state machine's behavior is defined by a GPIF II descriptor. The GPIF II descriptor is designed such that the required interface specifica-

tions are met. 8 kB of memory (separate from the 512 kB of embedded SRAM) is dedicated to the GPIF II waveform where the GPIF II descriptor is stored in a specific format.

Cypress's GPIF II Designer Tool enables fast development of GPIF II descriptors and includes examples for common interfaces.

Example implementations of GPIF II are the asynchronous slave FIFO and synchronous slave FIFO interfaces.

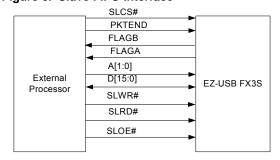

#### Slave FIFO interface

The Slave FIFO interface signals are shown in Figure 6. This interface allows an external processor to directly access up to four buffers internal to FX3S. Further details of the Slave FIFO interface are described on page 33.

**Note** Access to all 32 buffers is also supported over the slave FIFO interface. For details, contact Cypress Applications Support.

Figure 6. Slave FIFO Interface

Note: Multiple Flags may be configured

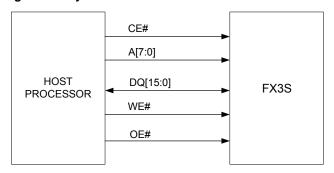

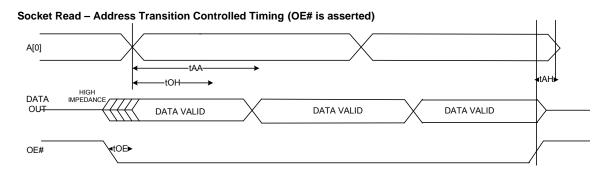

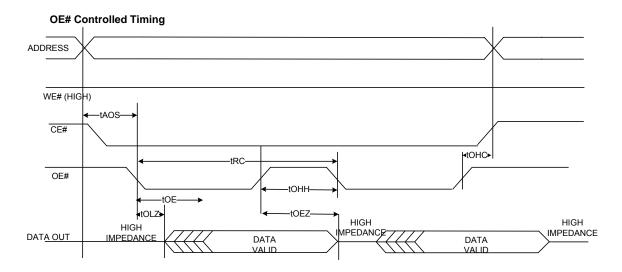

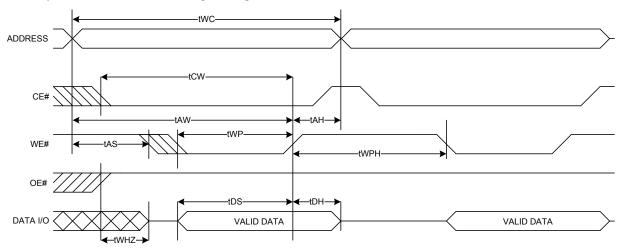

#### **Asynchronous SRAM**

This interface consists of standard asynchronous SRAM interface signals as shown in Figure 7 on page 7. This interface is used to access both the configuration registers and buffer memory of FX3S. Both single-cycle and burst accesses are supported by asynchronous interface signals.

The most significant address bit, A[7], determines whether the configuration registers or buffer memory are accessed. When the configuration registers are selected by asserting the address bit A[7], the address bus bits A[6:0] point to a configuration register. When A[7] is deasserted, the buffer memory is

accessed as indicated by the P-Port DMA transfer register and the transfer size is determined by the P-Port DMA transfer size register.

Application processors with a DMA controller that use address auto-increment during DMA transfers, can override this by connecting any higher-order address line (such as A[15]/A[23]/A[31]) of the application processor to FX3S's A[7].

In the asynchronous SRAM mode, when reading from a buffer memory, FX3S supports two methods of reading out next data from the buffer. The next data may be read out on the rising edge of OE# or by toggling the least significant address bit A[0].

In this mode, the P-Port interface works with a 32.5-ns minimum access cycle providing an interface data rate of up to 61.5 MB per second.

Figure 7. Asynchronous SRAM Interface

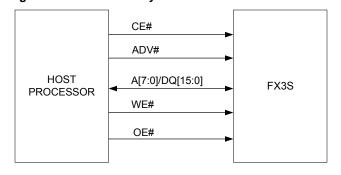

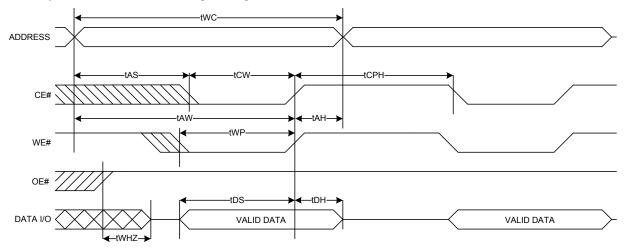

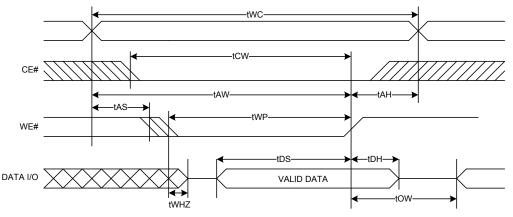

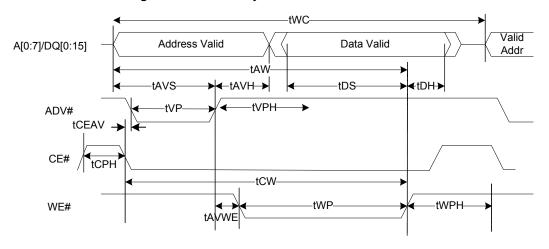

#### Asynchronous Address/Data Multiplexed

The physical ADMux memory interface consists of signals shown in Figure 8. This interface supports processors that implement a multiplexed address/data bus.

Figure 8. ADMux Memory Interface

FX3S's ADMux interface supports a 16-bit time-multiplexed address/data SRAM bus.

For read operations, assert both CE# and OE#.

For write operations, assert both CE# and WE#. OE# is "Don't Care" during a write operation (during both address and data phase of the write cycle). The input data is latched on the rising edge of WE# or CE#, whichever occurs first. Latch the addresses prior to the write operation by toggling Address Valid (ADV#). Assert Address Valid (ADV#) during the address phase of the write operation, as shown in Figure 19 on page 28.

ADV# must be LOW during the address phase of a read/write operation. ADV# must be HIGH during the data phase of a read/write operation, as shown in Figure 18 and Figure 19 on page 28.

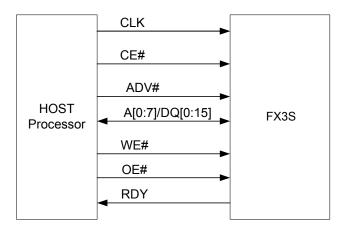

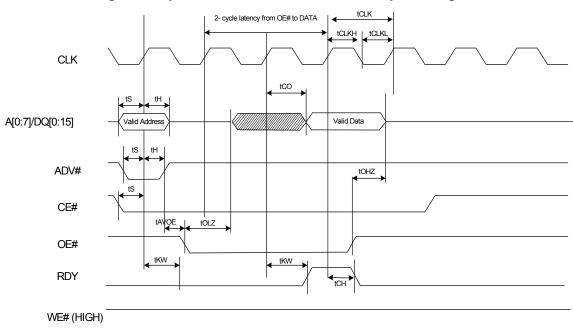

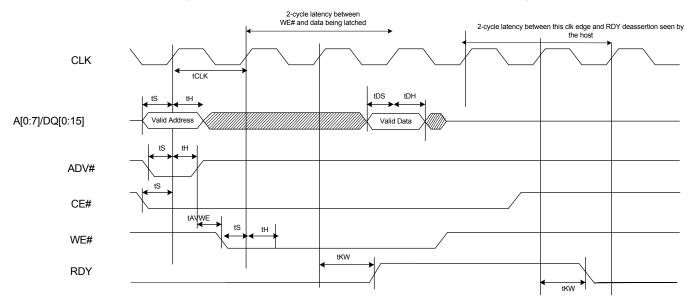

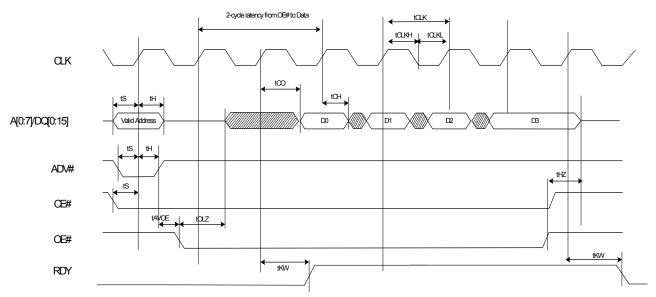

#### Synchronous ADMux Interface

FX3S's P-Port supports a synchronous address/data multiplexed interface. This operates at an interface frequency of up to 100 MHz and supports a 16-bit data bus.

The RDY output signal from the FX3S device indicates a data valid for read transfers and is acknowledged for write transfers.

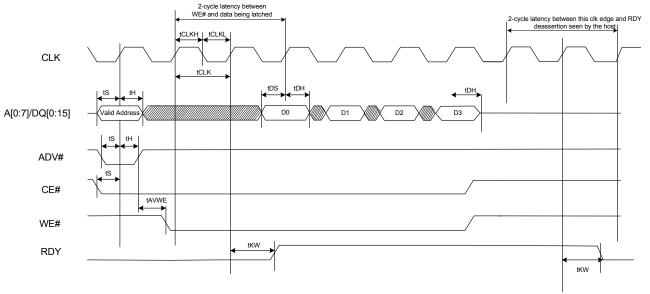

Figure 9. Synchronous ADMux Interface

See the Synchronous ADMux Interface timing diagrams for details

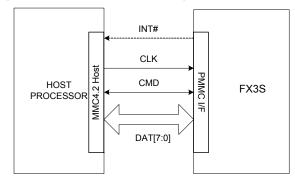

# Processor MMC (PMMC) Slave Interface

FX3S supports an MMC slave interface on the P-Port. This interface is named "PMMC" to distinguish it from the S-Port MMC interface.

Figure 10 illustrates the signals used to connect to the host processor.

The PMMC interface's GO\_IRQ\_STATE command allows FX3S to communicate asynchronous events without requiring the INT# signal. The use of the INT# signal is optional.

Figure 10. PMMC Interface Configuration

The MMC slave interface features are as follows:

- Interface operations are compatible with the MMC-System Specification, MMCA Technical Committee, Version 4.2.

- Supports booting from an eMMC device connected to the S-Port. This feature is supported for eMMC devices operating up to 52-MHz SDR.

- Supports PMMC interface voltage ranges of 1.7 V to 1.95 V and 2.7 V to 3.6 V.

- Supports open drain (both drive and receive open drain signals) on CMD pin to allow GO\_IRQ\_STATE (CMD40) for PMMC.

- Interface clock-frequency range: 0 to 52 MHz.

- Supports 1-bit, 4-bit, or 8-bit mode of operation. This configuration is determined by the MMC initialization procedure.

- FX3S responds to standard initialization phase commands as specified for the MMC 4.2 slave device.

- PMMC mode MMC 4.2 command classes: Class 0 (Basic), Class 2 (Block read), and Class 4 (Block write), Class 9 (I/O).

FX3S supports the following PMMC commands:

- Class 0: Basic

- CMD0, CMD1, CMD2, CMD3, CMD4, CMD6, CMD7, CMD8, CMD9, CMD10, CMD12, CMD13, CMD15, CMD19, CMD5 (wakeup support)

- Class 2: Block Read

- CMD16, CMD17, CMD18, CMD23

- Class 4: Block Write

- CMD16, CMD23, CMD24, CMD25

- Class 9: I-O

CMD39, CMD40

#### CPU

FX3S has an on-chip 32-bit, 200-MHz ARM926EJ-S core CPU. The core has direct access to 16 kB of Instruction Tightly Coupled Memory (TCM) and 8 kB of Data TCM. The ARM926EJ-S core provides a JTAG interface for firmware debugging.

FX3S offers the following advantages:

- Integrates 512 KB of embedded SRAM for code and data and 8 KB of Instruction cache and Data cache.

- Implements efficient and flexible DMA connectivity between the various peripherals (such as, USB, GPIF II, I<sup>2</sup>S, SPI, UART), requiring firmware only to configure data accesses between peripherals, which are then managed by the DMA fabric.

- Allows easy application development on industry-standard development tools for ARM926EJ-S.

Examples of the FX3S firmware are available with the Cypress EZ-USB FX3S Development Kit. Software APIs that can be ported to an external processor are available with the Cypress EZ-USB FX3S Software Development Kit.

# **Storage Port (S-Port)**

FX3S has two independent storage ports (S0-Port and S1-Port). Both storage ports support the following specifications:

- MMC-system specification, MMCA Technical Committee, Version 4.41

- SD specification, Version 3.0

- SDIO host controller compliant with SDIO Specification Version 2.00 (Jan.30, 2007)

Both storage ports support the following features:

#### SD/MMC Clock Stop

FX3S supports the stop clock feature, which can save power if the internal buffer is full when receiving data from the SD/MMC/SDIO.

# SD\_CLK Output Clock Stop

During the data transfer, the SD\_CLK clock can be enabled (on) or disabled (stopped) at any time by the internal flow control mechanism.

SD\_CLK output frequency is dynamically configurable using a clock divisor from a system clock. The clock choice for the divisor is user-configurable through a register. For example, the following frequencies may be configured:

- 400 kHz For the SD/MMC card initialization

- 20 MHz For a card with 0- to 20-MHz frequency

- 24 MHz For a card with 0- to 26-MHz frequency

- 48 MHz For a card with 0- to 52-MHz frequency (48-MHz frequency on SD\_CLK is supported when the clock input to FX3S is 19.2 MHz or 38.4 MHz)

- 52 MHz For a card with 0- to 52-MHz frequency (52-MHz frequency on SD\_CLK is supported when the clock input to FX3S is 26 MHz or 52 MHz)

- 100 MHz For a card with 0- to 100-MHz frequency

If the DDR mode is selected, data is clocked on both the rising and falling edge of the SD clock. DDR clocks run up to 52 MHz.

#### **Card Insertion and Removal Detection**

FX3S supports the two-card insertion and removal detection mechanisms.

- Use of SD\_D[3] data: During system design, this signal must have an external 470-kΩ pull-down resistor connected to SD\_D[3]. SD cards have an internal 10-kΩ pull-up resistor. When the card is inserted or removed from the SD/MMC connector, the voltage level at the SD\_D[3] pin changes and triggers an interrupt to the CPU. The older generations of MMC cards do not support this card detection mechanism.

- Use of the S0/S1\_INS pin: Some SD/MMC connectors facilitate a micro switch for card insertion/removal detection. This micro switch can be connected to S0/S1\_INS. When the card is inserted or removed from the SD/MMC connector, it turns the micro switch on and off. This changes the voltage level at the pin that triggers the interrupt to the CPU. The card-detect micro switch polarity is assumed to be the same as the write-protect

micro switch polarity. A low indicates that the card is inserted. This S0/S1\_INS pin is shared between the two S-Ports. Register configuration determines which port gets to use this pin. This pin is mapped to the S1VDDQ power domain; if S0VDDQ and S1VDDQ are at different voltage levels, this pin cannot be used as S1\_INS.

#### Write Protection (WP)

The S0\_WP/S1\_WP (SD Write Protection) on S-Port is used to connect to the WP micro switch of SD/MMC card connector. This pin internally connects to a CPU-accessible GPIO for firmware to detect the SD card write protection.

#### **SDIO Interrupt**

The SDIO interrupt functionality is supported as specified in the SDIO specification Version 2.00 (January 30, 2007).

#### **SDIO Read-Wait Feature**

FX3S supports the optional read-wait and suspend-resume features as defined in the SDIO specification Version 2.00 (January 30, 2007).

#### JTAG Interface

FX3S's JTAG interface has a standard five-pin interface to connect to a JTAG debugger in order to debug firmware through the CPU-core's on-chip-debug circuitry.

Industry-standard debugging tools for the ARM926EJ-S core can be used for the FX3S application development.

#### Other Interfaces

FX3S supports the following serial peripherals:

- **■** UART

- I<sup>2</sup>C

- I<sup>2</sup>S

- SP

The SPI, UART, and I<sup>2</sup>S interfaces are multiplexed on the serial peripheral port.

#### **UART Interface**

The UART interface of FX3S supports full-duplex communication. It includes the signals noted in Table 1.

**Table 1. UART Interface Signals**

| Signal | Description   |

|--------|---------------|

| TX     | Output signal |

| RX     | Input signal  |

| CTS    | Flow control  |

| RTS    | Flow control  |

The UART is capable of generating a range of baud rates, from 300 bps to 4608 Kbps, selectable by the firmware. If flow control is enabled, then FX3S's UART only transmits data when the CTS input is asserted. In addition to this, FX3S's UART asserts the RTS output signal, when it is ready to receive data.

# I<sup>2</sup>C Interface

FX3S's I<sup>2</sup>C interface is compatible with the I<sup>2</sup>C Bus Specification Revision 3. This I<sup>2</sup>C interface is capable of operating only as I<sup>2</sup>C master; therefore, it may be used to communicate with other I<sup>2</sup>C slave devices. For example, FX3S may boot from an EEPROM connected to the I<sup>2</sup>C interface, as a selectable boot option.

FX3S's I<sup>2</sup>C Master Controller also supports multi-master mode functionality.

The power supply for the I<sup>2</sup>C interface is VIO5, which is a separate power domain from the other serial peripherals. This gives the I<sup>2</sup>C interface the flexibility to operate at a different voltage than the other serial interfaces.

The I<sup>2</sup>C controller supports bus frequencies of 100 kHz, 400 kHz, and 1 MHz. When VIO5 is 1.2 V, the maximum operating frequency supported is 100 kHz. When VIO5 is 1.8 V, 2.5 V, or 3.3 V, the operating frequencies supported are 400 kHz and 1 MHz. The I<sup>2</sup>C controller supports the clock-stretching feature to enable slower devices to exercise flow control.

The I<sup>2</sup>C interface's SCL and SDA signals require external pull-up resistors. The pull-up resistors must be connected to VIO5.

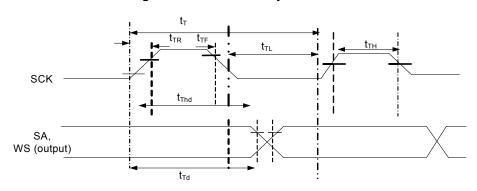

#### I<sup>2</sup>S Interface

FX3S has an I<sup>2</sup>S port to support external audio codec devices. FX3S functions as I<sup>2</sup>S Master as transmitter only. The I<sup>2</sup>S interface consists of four signals: clock line (I2S\_CLK), serial data line (I2S\_SD), word select line (I2S\_WS), and master system clock (I2S\_MCLK). FX3S can generate the system clock as an output on I2S\_MCLK or accept an external system clock input on I2S MCLK.

The sampling frequencies supported by the I<sup>2</sup>S interface are 32 kHz, 44.1 kHz, and 48 kHz.

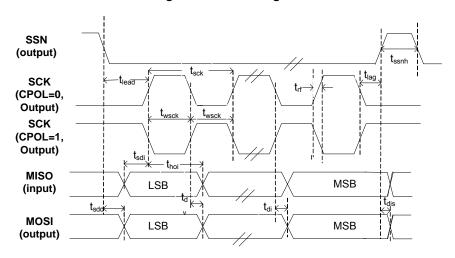

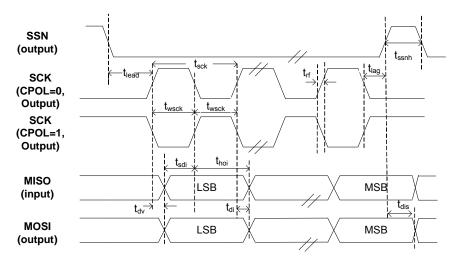

#### **SPI Interface**

FX3S supports an SPI Master interface on the Serial Peripherals port. The maximum operation frequency is 33 MHz.

The SPI controller supports four modes of SPI communication (see SPI Timing Specification on page 44 for details on the modes) with the Start-Stop clock. This controller is a single-master controller with a single automated SSN control. It supports transaction sizes ranging from 4 bits to 32 bits.

# **Boot Options**

FX3S can load boot images from various sources, selected by the configuration of the PMODE pins. Following are the FX3S boot options:

- Boot from USB

- Boot from I<sup>2</sup>C

- Boot from SPI (SPI devices supported are M25P16 (16 Mbit), M25P80 (8 Mbit), and M25P40 (4 Mbit)) or their equivalents

- Boot from eMMC (S0-port)

- Boot from GPIF II ASync ADMux mode

- Boot from GPIF II Sync ADMux mode

- Boot from GPIF II ASync SRAM mode

- Boot from PMMC (P-Port)

Table 2. FX3S Booting Options

| PMODE[2:0] [2] | Boot From                                         |

|----------------|---------------------------------------------------|

| F00            | Sync ADMux (16-bit)                               |

| F01            | Async ADMux (16-bit)                              |

| F10            | PMMC Legacy                                       |

| F11            | USB boot                                          |

| F0F            | Async SRAM (16-bit)                               |

| F1F            | I <sup>2</sup> C, On Failure, USB Boot is Enabled |

| 1FF            | I <sup>2</sup> C only                             |

| 0F1            | SPI, On Failure, USB Boot is Enabled              |

| 000            | S0-Port (eMMC) On failure, USB boot is enabled    |

| 100            | S0-port (eMMC)                                    |

#### Reset

#### **Hard Reset**

A hard reset is initiated by asserting the Reset# pin on FX3S. The specific reset sequence and timing requirements are detailed in Figure 31 on page 46 and Table 19 on page 45. All I/Os are tristated during a hard reset.

#### Soft Reset

In a soft reset, the processor sets the appropriate bits in the PP INIT control register. There are two types of Soft Reset:

- CPU Reset The CPU Program Counter is reset. Firmware does not need to be reloaded following a CPU Reset.

- Whole Device Reset This reset is identical to Hard Reset.

- The firmware must be reloaded following a Whole Device Reset.

# Clocking

FX3S allows either a crystal to be connected between the XTALIN and XTALOUT pins or an external clock to be connected at the CLKIN pin. The XTALIN, XTALOUT, CLKIN, and CLKIN 32 pins can be left unconnected if they are not used.

Crystal frequency supported is 19.2 MHz, while the external clock frequencies supported are 19.2, 26, 38.4, and 52 MHz.

FX3S has an on-chip oscillator circuit that uses an external 19.2-MHz (±100 ppm) crystal (when the crystal option is used). An appropriate load capacitance is required with a crystal. Refer to the specification of the crystal used to determine the appropriate load capacitance. The FSLC[2:0] pins must be configured appropriately to select the crystal- or clock-frequency option. The configuration options are shown in Table 3.

Clock inputs to FX3S must meet the phase noise and jitter requirements specified in Table 4 on page 11.

The input clock frequency is independent of the clock and data rate of the FX3S core or any of the device interfaces (including P-Port and S-Port). The internal PLL applies the appropriate clock multiply option depending on the input frequency.

Table 3. Crystal/Clock Frequency Selection

| FSLC[2] | FSLC[1] | FSLC[0] | Crystal/Clock<br>Frequency |

|---------|---------|---------|----------------------------|

| 0       | 0       | 0       | 19.2-MHz crystal           |

| 1       | 0       | 0       | 19.2-MHz input CLK         |

| 1       | 0       | 1       | 26-MHz input CLK           |

| 1       | 1       | 0       | 38.4-MHz input CLK         |

| 1       | 1       | 1       | 52-MHz input CLK           |

2. F indicates Floating.

Table 4. FX3S Input Clock Specifications

| Parameter                   | Description    | Specifi | Units       |        |

|-----------------------------|----------------|---------|-------------|--------|

| Farameter                   | Description    | Min     | Max         | Offics |

| Phase noise                 | 100-Hz offset  | _       | <b>–</b> 75 | dB     |

|                             | 1- kHz offset  | _       | -104        | dB     |

|                             | 10-kHz offset  | _       | -120        | dB     |

|                             | 100-kHz offset | _       | -128        | dB     |

|                             | 1-MHz offset   | _       | -130        | dB     |

| Maximum frequency deviation |                | _       | 150         | ppm    |

| Duty cycle                  |                | 30      | 70          | %      |

| Overshoot                   |                | _       | 3           | %      |

| Undershoot                  |                | _       | -3          | %      |

| Rise time/fall time         |                | _       | 3           | ns     |

# 32-kHz Watchdog Timer Clock Input

FX3S includes a watchdog timer. The watchdog timer can be used to interrupt the ARM926EJ-S core, automatically wake up the FX3S in Standby mode, and reset the ARM926EJ-S core. The watchdog timer runs a 32-kHz clock, which may be optionally supplied from an external source on a dedicated FX3S pin.

The firmware can disable the watchdog timer.

Requirements for the optional 32-kHz clock input are listed in Table 5.

Table 5. 32-kHz Clock Input Requirements

| Parameter           | Min | Max  | Units |

|---------------------|-----|------|-------|

| Duty cycle          | 40  | 60   | %     |

| Frequency deviation | _   | ±200 | ppm   |

| Rise time/fall time | _   | 200  | ns    |

#### **Power**

FX3S has the following power supply domains:

- IO\_VDDQ: This is a group of independent supply domains for digital I/Os. The voltage level on these supplies is 1.8 V to 3.3 V. FX3S provides six independent supply domains for digital I/Os listed as follows (see Pin Description on page 16 for details on each of the power domain signals):

- □ VIO1: GPIF II I/O

- □ VIO2: S0-Port Supply

- □ VIO3: S1-Port Supply

- □ VIO4: S1-Port and Low Speed Peripherals (UART/SPI/I2S) Supply

- □ VIO5: I<sup>2</sup>C and JTAG (supports 1.2 V to 3.3 V)

- □ CVDDQ: Clock

- $\square$  V<sub>DD</sub>: This is the supply voltage for the logic core. The nominal supply-voltage level is 1.2 V. This supplies the core logic circuits. The same supply must also be used for the following:

- AVDD: This is the 1.2-V supply for the PLL, crystal oscillator, and other core analog circuits

- U3TXVDDQ/U3RXVDDQ: These are the 1.2-V supply voltages for the USB 3.0 interface.

- VBATT/VBUS: This is the 3.2-V to 6-V battery power supply for the USB I/O and analog circuits. This supply powers the USB transceiver through FX3S's internal voltage regulator. VBATT is internally regulated to 3.3 V.

# **Power Modes**

FX3S supports the following power modes:

- Normal mode: This is the full-functional operating mode. The internal CPU clock and the internal PLLs are enabled in this mode.

- $\hfill \square$  Normal operating power consumption does not exceed the sum of I\_{CC} Core max and I\_{CC} USB max (see Table 7 for current consumption specifications).

- □ The I/O power supplies VIO2, VIO3, VIO4, and VIO5 can be turned off when the corresponding interface is not in use. VIO1 cannot be turned off at any time if the GPIF II interface is used in the application.

- Low-power modes (see Table 6 on page 12):

- □ Suspend mode with USB 3.0 PHY enabled (L1)

- □ Suspend mode with USB 3.0 PHY disabled (L2)

- □ Standby mode (L3)

- ☐ Core power-down mode (L4)

Table 6. Entry and Exit Methods for Low-Power Modes

| <b>Low-Power Mode</b> | Characteristics                                                                                                                                                                                                    | Methods of Entry                                                                                                                                                                                                                                             | Methods of Exit                                                                                                                                                                                           |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | <ul> <li>The power consumption in this mode does not exceed ISB<sub>1</sub></li> <li>USB 3.0 PHY is enabled and is in U3 mode (one of the suspend modes defined by the USB 3.0 specification). This one</li> </ul> | ■ Firmware executing on ARM926EJ-S core can put FX3S into suspend mode. For example, on USB suspend condition, firmware may decide to put FX3S into suspend mode  ■ External Processor, through the use of mailbox registers, can put FX3S into suspend mode | Methods of Exit  ■ D+ transitioning to low or high ■ D-transitioning to low or high ■ Impedance change on OTG_ID pin ■ Resume condition on SSRX± ■ Detection of VBUS ■ Level detect on UART CTS (program- |

|                       | ■ The states of the configuration registers, buffer memory, and all internal RAM are maintained                                                                                                                    |                                                                                                                                                                                                                                                              | mable polarity)  GPIF II interface assertion of CTL[0]                                                                                                                                                    |

|                       | ■ All transactions must be completed before FX3S enters Suspend mode (state of outstanding transactions are not preserved)                                                                                         |                                                                                                                                                                                                                                                              | ■ Assertion of RESET#                                                                                                                                                                                     |

|                       | ■ The firmware resumes operation from where it was suspended (except when woken up by RESET# assertion) because the program counter does not reset                                                                 |                                                                                                                                                                                                                                                              |                                                                                                                                                                                                           |

Table 6. Entry and Exit Methods for Low-Power Modes (continued)

| Table 6. Entry and Exit Methods for Low-Power Modes (continued) |                                                                                                                                                    |                                                                                                     |                                                    |  |  |  |  |

|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|

| <b>Low-Power Mode</b>                                           | Characteristics                                                                                                                                    | Methods of Entry                                                                                    | Methods of Exit                                    |  |  |  |  |

| Suspend Mode<br>with USB 3.0 PHY<br>Disabled (L2)               | ■ The power consumption in this mode does not exceed ISB <sub>2</sub>                                                                              | ■ Firmware executing on ARM926EJ-S core can put FX3S into suspend mode. For example, on USB suspend | ■ D+ transitioning to low or high                  |  |  |  |  |

| Disabled (L2)                                                   | ■ USB 3.0 PHY is disabled and the USB interface is in suspend mode                                                                                 | condition, firmware may decide to put FX3S into suspend mode                                        | ■ D- transitioning to low or high                  |  |  |  |  |

|                                                                 | ■ The clocks are shut off. The PLLs are disabled                                                                                                   | ■ External Processor, through the use of mailbox registers can put FX3S into                        | ■ Impedance change on<br>OTG_ID pin                |  |  |  |  |

|                                                                 | ■ All I/Os maintain their previous state                                                                                                           | suspend mode                                                                                        | ■ Resume condition on SSRX±                        |  |  |  |  |

|                                                                 | ■ USB interface maintains the previous state                                                                                                       |                                                                                                     | ■ Detection of VBUS                                |  |  |  |  |

|                                                                 | ■ Power supply for the wakeup source and core power must be retained. All other power domains can be turned on/off individually                    |                                                                                                     | ■ Level detect on UART_CTS (programmable polarity) |  |  |  |  |

|                                                                 | ■ The states of the configuration registers,                                                                                                       |                                                                                                     | ■ GPIF II interface assertion of CTL[0]            |  |  |  |  |

|                                                                 | buffer memory and all internal RAM are maintained                                                                                                  |                                                                                                     | ■ Assertion of RESET#                              |  |  |  |  |

|                                                                 | ■ All transactions must be completed before FX3S enters Suspend mode (state of outstanding transactions are not preserved)                         |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ The firmware resumes operation from where it was suspended (except when woken up by RESET# assertion) because the program counter does not reset |                                                                                                     |                                                    |  |  |  |  |

| Standby Mode (L3)                                               | ■ The power consumption in this mode does not exceed ISB3                                                                                          | ■ Firmware executing on ARM926EJ-S core or external processor configures                            | ■ Detection of VBUS                                |  |  |  |  |

| (LO)                                                            | ■ All configuration register settings and                                                                                                          | the appropriate register                                                                            | ■ Level detect on UART CTS (Program-               |  |  |  |  |

|                                                                 | program/data RAM contents are                                                                                                                      |                                                                                                     | mable Polarity)                                    |  |  |  |  |

|                                                                 | preserved. However, data in the buffers or other parts of the data path, if any, is                                                                |                                                                                                     | ■ GPIF II interface                                |  |  |  |  |

|                                                                 | not guaranteed. Therefore, the external                                                                                                            |                                                                                                     | assertion of CTL[0]                                |  |  |  |  |

|                                                                 | processor should take care that the data<br>needed is read before putting FX3S into<br>this Standby Mode                                           |                                                                                                     | ■ Assertion of RESET#                              |  |  |  |  |

|                                                                 | ■ The program counter is reset after waking up from Standby                                                                                        |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ GPIO pins maintain their configuration                                                                                                           |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ Crystal oscillator is turned off                                                                                                                 |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ Internal PLL is turned off                                                                                                                       |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ USB transceiver is turned off                                                                                                                    |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ ARM926EJ-S core is powered down.<br>Upon wakeup, the core re-starts and runs<br>the program stored in the program/data<br>RAM                    |                                                                                                     |                                                    |  |  |  |  |

|                                                                 | ■ Power supply for the wakeup source and core power must be retained. All other power domains can be turned on/off individually                    |                                                                                                     |                                                    |  |  |  |  |

# Table 6. Entry and Exit Methods for Low-Power Modes (continued)

| <b>Low-Power Mode</b> | Characteristics                                                                                                                              | Methods of Entry           | Methods of Exit       |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|

|                       |                                                                                                                                              | ■ Turn off V <sub>DD</sub> | ■ Reapply VDD         |

| Mode (L4)             | does not exceed ISB <sub>4</sub>                                                                                                             |                            | ■ Assertion of RESET# |

|                       | Core power is turned off                                                                                                                     |                            |                       |

|                       | All buffer memory, configuration<br>registers, and the program RAM do not<br>maintain state. After exiting this mode,<br>reload the firmware |                            |                       |

|                       | ■ In this mode, all other power domains can be turned on/off individually                                                                    |                            |                       |

# **Configuration Options**

Configuration options are available for specific usage models. Contact Cypress Applications or Marketing for details.

# Digital I/Os

FX3S has internal firmware-controlled pull-up or pull-down resistors on all digital I/O pins. An internal 50-k $\Omega$  resistor pulls the pins high, while an internal 10-k $\Omega$  resistor pulls the pins low to prevent them from floating. The I/O pins may have the following states:

- Tristated (High-Z)

- Weak pull-up (via internal 50 kΩ)

- Pull-down (via internal 10 kΩ)

- Hold (I/O hold its value) when in low-power modes

- The JTAG TDI, TMC, and TRST# signals have fixed 50-kΩ internal pull-ups, and the TCK signal has a fixed 10-kΩ pull-down resistor.

All unused I/Os should be pulled high by using the internal pull-up resistors. All unused outputs should be left floating. All I/Os can be driven at full-strength, three-quarter strength, half-strength, or quarter-strength. These drive strengths are configured separately for each interface.

#### **GPIOs**

EZ-USB enables a flexible pin configuration both on the GPIF II and the serial peripheral interfaces. Any unused control pins (except CTL[15]) on the GPIF II interface can be used as GPIOs.

Similarly, any unused pins on the serial peripheral interfaces may be configured as GPIOs. See the Pin Description on page 16 for pin configuration options.

All GPIF II and GPIO pins support an external load of up to 16 pF for every pin.

#### **EMI**

FX3S meets EMI requirements outlined by FCC 15B (USA) and EN55022 (Europe) for consumer electronics. FX3S can tolerate reasonable EMI, conducted by the aggressor, outlined by these specifications and continue to function as expected.

# System-level ESD

FX3S has built-in ESD protection on the D+, D-, and GND pins on the USB interface. The ESD protection levels provided on these ports are:

- ±2.2-KV human body model (HBM) based on JESD22-A114 Specification

- ±6-KV contact discharge and ±8-KV air gap discharge based on IEC61000-4-2 level 3A

- ± 8-KV Contact Discharge and ±15-KV Air Gap Discharge based on IEC61000-4-2 level 4C.

This protection ensures the device continues to function after ESD events up to the levels stated in this section.

The SSRX+, SSRX-, SSTX+, and SSTX- pins only have up to ±2.2-KV HBM internal ESD protection.

|   | riguie II. 1 700 Ban map (Top View) |          |          |          |          |          |          |          |              |              |          |

|---|-------------------------------------|----------|----------|----------|----------|----------|----------|----------|--------------|--------------|----------|

|   | 1                                   | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9            | 10           | 11       |

| Α | U3VSSQ                              | U3RXVDDQ | SSRXM    | SSRXP    | SSTXP    | SSTXM    | AVDD     | VSS      | DP           | DM           | NC       |

| В | VIO4                                | FSLC[0]  | R_USB3   | FSLC[1]  | U3TXVDDQ | CVDDQ    | AVSS     | vss      | VSS          | VDD          | TRST#    |

| С | GPIO[54]                            | GPIO[55] | VDD      | GPIO[57] | RESET#   | XTALIN   | XTALOUT  | R_USB2   | OTG_ID       | TDO          | VIO5     |

| D | GPIO[50]                            | GPIO[51] | GPIO[52] | GPIO[53] | GPIO[56] | CLKIN_32 | CLKIN    | VSS      | I2C_GPIO[58] | 12C_GPIO[59] | O[60]    |

| Е | GPIO[47]                            | VSS      | VIO3     | GPIO[49] | GPIO[48] | FSLC[2]  | TDI      | TMS      | VDD          | VBATT        | VBUS     |

| F | VIO2                                | GPIO[45] | GPIO[44] | GPIO[41] | GPIO[46] | TCK      | GPIO[2]  | GPIO[5]  | GPIO[1]      | GPIO[0]      | VDD      |

| G | VSS                                 | GPIO[42] | GPIO[43] | GPIO[30] | GPIO[25] | GPIO[22] | GPIO[21] | GPIO[15] | GPIO[4]      | GPIO[3]      | VSS      |

| Н | VDD                                 | GPIO[39] | GPIO[40] | GPIO[31] | GPIO[29] | GPIO[26] | GPIO[20] | GPIO[24] | GPIO[7]      | GPIO[6]      | VIO1     |

| J | GPIO[38]                            | GPIO[36] | GPIO[37] | GPIO[34] | GPIO[28] | GPIO[16] | GPIO[19] | GPIO[14] | GPIO[9]      | GPIO[8]      | VDD      |

| K | GPIO[35]                            | GPIO[33] | VSS      | VSS      | GPIO[27] | GPIO[23] | GPIO[18] | GPIO[17] | GPIO[13]     | GPIO[12]     | GPIO[10] |

| L | VSS                                 | VSS      | VSS      | GPIO[32] | VDD      | VSS      | VDD      | INT#     | VIO1         | GPIO[11]     | VSS      |

Figure 11. FX3S Ball Map (Top View)

# **Pin Description**

|     | FX3S Pin Description |     |          |                      |                      |                    |            |                |              |  |

|-----|----------------------|-----|----------|----------------------|----------------------|--------------------|------------|----------------|--------------|--|

|     |                      |     |          |                      |                      | P                  | -Port      |                |              |  |

| Pin | Power<br>Domain      | I/O | Name     | GPIF II<br>Interface | Slave FIFO Interface | РММС               | Async SRAM | Async<br>ADMux | SyncADMux    |  |

| F10 | VIO1                 | I/O | GPIO[0]  | DQ[0]                | DQ[0]                | MMC_D0             | DQ[0]      | DQ[0]/A[0]     | DQ[0]/A[0]   |  |

| F9  | VIO1                 | I/O | GPIO[1]  | DQ[1]                | DQ[1]                | MMC_D1             | DQ[1]      | DQ[1]/A[1]     | DQ[1]/A[1]   |  |

| F7  | VIO1                 | I/O | GPIO[2]  | DQ[2]                | DQ[2]                | MMC_D2             | DQ[2]      | DQ[2]/A[2]     | DQ[2]/A[2]   |  |

| G10 | VIO1                 | I/O | GPIO[3]  | DQ[3]                | DQ[3]                | MMC_D3             | DQ[3]      | DQ[3]/A[3]     | DQ[3]/A[3]   |  |

| G9  | VIO1                 | I/O | GPIO[4]  | DQ[4]                | DQ[4]                | MMC_D4             | DQ[4]      | DQ[4]/A[4]     | DQ[4]/A[4]   |  |

| F8  | VIO1                 | I/O | GPIO[5]  | DQ[5]                | DQ[5]                | MMC_D5             | DQ[5]      | DQ[5]/A[5]     | DQ[5]/A[5]   |  |

| H10 | VIO1                 | I/O | GPIO[6]  | DQ[6]                | DQ[6]                | MMC_D6             | DQ[6]      | DQ[6]/A[6]     | DQ[6]/A[6]   |  |

| Н9  | VIO1                 | I/O | GPIO[7]  | DQ[7]                | DQ[7]                | MMC_D7             | DQ[7]      | DQ[7]/A[7]     | DQ[7]/A[7]   |  |

| J10 | VIO1                 | I/O | GPIO[8]  | DQ[8]                | DQ[8]                | GPIO               | DQ[8]      | DQ[8]/A[8]     | DQ[8]/A[8]   |  |

| J9  | VIO1                 | I/O | GPIO[9]  | DQ[9]                | DQ[9]                | GPIO               | DQ[9]      | DQ[9]/A[9]     | DQ[9]/A[9]   |  |

| K11 | VIO1                 | I/O | GPIO[10] | DQ[10]               | DQ[10]               | GPIO               | DQ[10]     | DQ[10]/A[10]   | DQ[10]/A[10] |  |

| L10 | VIO1                 | I/O | GPIO[11] | DQ[11]               | DQ[11]               | GPIO               | DQ[11]     | DQ[11]/A[11]   | DQ[11]/A[11] |  |

| K10 | VIO1                 | I/O | GPIO[12] | DQ[12]               | DQ[12]               | GPIO               | DQ[12]     | DQ[12]/A[12]   | DQ[12]/A[12] |  |

| K9  | VIO1                 | I/O | GPIO[13] | DQ[13]               | DQ[13]               | GPIO               | DQ[13]     | DQ[13]/A[13]   | DQ[13]/A[13] |  |

| J8  | VIO1                 | I/O | GPIO[14] | DQ[14]               | DQ[14]               | GPIO               | DQ[14]     | DQ[14]/A[14]   | DQ[14]/A[14] |  |

| G8  | VIO1                 | I/O | GPIO[15] | DQ[15]               | DQ[15]               | GPIO               | DQ[15]     | DQ[15]/A[15]   | DQ[15]/A[15] |  |

| J6  | VIO1                 | I/O | GPIO[16] | PCLK                 | CLK                  | MMC_CLK            | CLK        | CLK            | CLK          |  |

| K8  | VIO1                 | I/O | GPIO[17] | CTL[0]               | SLCS#                | GPIO               | CE#        | CE#            | CE#          |  |

| K7  | VIO1                 | I/O | GPIO[18] | CTL[1]               | SLWR#                | MMC_CMD            | WE#        | WE#            | WE#          |  |

| J7  | VIO1                 | I/O | GPIO[19] | CTL[2]               | SLOE#                | GPIO               | OE#        | OE#            | OE#          |  |

| H7  | VIO1                 | I/O | GPIO[20] | CTL[3]               | SLRD#                | GPIO               | DACK#      | DACK#          | DACK#        |  |

| G7  | VIO1                 | I/O | GPIO[21] | CTL[4]               | FLAGA                | GPIO               | DRQ#       | DRQ#           | DRQ#         |  |

| G6  | VIO1                 | I/O | GPIO[22] | CTL[5]               | FLAGB                | GPIO               | A[7]       | GPIO           | GPIO         |  |

| K6  | VIO1                 | I/O | GPIO[23] | CTL[6]               | GPIO                 | GPIO               | A[6]       | GPIO           | RDY          |  |

| H8  | VIO1                 | I/O | GPIO[24] | CTL[7]               | PKTEND#              | GPIO               | A[5]       | GPIO           | GPIO         |  |

| G5  | VIO1                 | I/O | GPIO[25] | CTL[8]               | GPIO                 | GPIO               | A[4]       | GPIO           | GPIO         |  |

| H6  | VIO1                 | I/O | GPIO[26] | CTL[9]               | GPIO                 | GPIO               | A[3]       | GPIO           | GPIO         |  |

| K5  | VIO1                 | I/O | GPIO[27] | CTL[10]              | GPIO                 | GPIO               | A[2]       | ADV#           | ADV#         |  |

| J5  | VIO1                 | I/O | GPIO[28] | CTL[11]              | A1                   | CARKIT_UART<br>_RX | A[1]       | GPIO           | GPIO         |  |

| H5  | VIO1                 | I/O | GPIO[29] | CTL[12]              | A0                   | CARKIT_UART<br>_TX | A[0]       | GPIO           | GPIO         |  |

| G4  | VIO1                 | I/O | GPIO[30] | PMODE[0]             | PMODE[0]             | PMODE[0]           | PMODE[0]   | PMODE[0]       | PMODE[0]     |  |

| H4  | VIO1                 | I/O | GPI0[31] | PMODE[1]             | PMODE[1]             | PMODE[1]           | PMODE[1]   | PMODE[1]       | PMODE[1]     |  |

| L4  | VIO1                 | I/O | GPIO[32] | PMODE[2]             | PMODE[2]             | PMODE[2]           | PMODE[2]   | PMODE[2]       | PMODE[2]     |  |

| L8  | VIO1                 | I/O | INT#     | INT#/CTL[15]         | CTL[15]              | INT#               | INT#       | INT#           | INT#         |  |

| C5  | CVDDQ                | I   | RESET#   | RESET#               | RESET#               | RESET#             | RESET#     | RESET#         | RESET#       |  |

|     | FX3S Pin Description |     |            |                  |          |          |         |      |                   |          |                  |

|-----|----------------------|-----|------------|------------------|----------|----------|---------|------|-------------------|----------|------------------|

|     | Power                | .// | <b>N</b> 1 |                  |          |          | S0-F    | ort  |                   |          |                  |

| Pin | Domain               | I/O | Name       | 8b               | MMC      | S        | D+GPIO  |      |                   | GPIO     |                  |

| K2  | VIO2                 | I/O | GPIO[33]   | S0_SD0           |          |          | S0_SD0  |      |                   | GPIO     |                  |

| J4  | VIO2                 | I/O | GPIO[34]   | S0               | _SD1     |          | S0_SD1  |      |                   | GPIO     |                  |

| K1  | VIO2                 | I/O | GPIO[35]   | S0               | _SD2     |          | S0_SD2  |      |                   | GPIO     |                  |

| J2  | VIO2                 | I/O | GPIO[36]   | S0               | _SD3     |          | S0_SD3  |      |                   | GPIO     |                  |

| J3  | VIO2                 | I/O | GPIO[37]   | S0               | _SD4     |          | GPIO    |      |                   | GPIO     |                  |

| J1  | VIO2                 | I/O | GPIO[38]   | S0               | _SD5     |          | GPIO    |      |                   | GPIO     |                  |

| H2  | VIO2                 | I/O | GPIO[39]   | S0               | _SD6     |          | GPIO    |      |                   | GPIO     |                  |

| НЗ  | VIO2                 | I/O | GPIO[40]   | S0               | _SD7     |          | GPIO    |      |                   | GPIO     |                  |

| F4  | VIO2                 | I/O | GPIO[41]   |                  | _CMD     | ,        | S0_CMD  |      |                   | GPIO     |                  |

| G2  | VIO2                 | I/O | GPIO[42]   | S0               | _CLK     |          | S0_CLK  |      |                   | GPIO     |                  |

| G3  | VIO2                 | I/O | GPIO[43]   | SC               | )_WP     |          | S0_WP   |      |                   | GPIO     |                  |

| F3  | VIO2                 | I/O | GPIO[44]   | S0S1_INS         |          | S0S1_INS |         |      | GPIO              |          |                  |

| F2  | VIO2                 | I/O | GPIO[45]   | MMC0_RST_OUT     |          | GPIO     |         | GPIO |                   |          |                  |

|     |                      |     |            | S1-Port          |          |          |         |      |                   |          |                  |

|     |                      |     |            | 8b MMC           | SD+UART  | SD+SPI   | SD+GPIO | GPIO | GPIO+UART<br>+I2S | SD+I2S   | UART+SPI<br>+I2S |

| F5  | VIO3                 | I/O | GPIO[46]   | S1_SD0           | S1_SD0   | S1_SD0   | S1_SD0  | GPIO | GPIO              | S1_SD0   | UART_RT<br>S     |

| E1  | VIO3                 | I/O | GPIO[47]   | S1_SD1           | S1_SD1   | S1_SD1   | S1_SD1  | GPIO | GPIO              | S1_SD1   | UART_CT<br>S     |

| E5  | VIO3                 | I/O | GPIO[48]   | S1_SD2           | S1_SD2   | S1_SD2   | S1_SD2  | GPIO | GPIO              | S1_SD2   | UART_TX          |

| E4  | VIO3                 | I/O | GPIO[49]   | S1_SD3           | S1_SD3   | S1_SD3   | S1_SD3  | GPIO | GPIO              | S1_SD3   | UART_RX          |

| D1  | VIO3                 | I/O | GPIO[50]   | S1_CMD           | S1_CMD   | S1_CMD   | S1_CMD  | GPIO | I2S_CLK           | S1_CMD   | I2S_CLK          |

| D2  | VIO3                 | I/O | GPIO[51]   | S1_CLK           | S1_CLK   | S1_CLK   | S1_CLK  | GPIO | I2S_SD            | S1_CLK   | I2S_SD           |

| D3  | VIO3                 | I/O | GPIO[52]   | S1_WP            | S1_WP    | S1_WP    | S1_WP   | GPIO | I2S_WS            | S1_WP    | I2S_WS           |

|     |                      |     |            |                  | •        |          |         |      |                   |          |                  |

| D4  | VIO4                 | I/O | GPIO[53]   | S1_SD4           | UART_RTS | SPI_SCK  | GPIO    | GPIO | UART_RTS          | GPIO     | SPI_SCK          |

| C1  | VIO4                 | I/O | GPIO[54]   | S1_SD5           | UART_CTS | SPI_SSN  | GPIO    | GPIO | UART_CTS          | I2S_CLK  | SPI_SSN          |

| C2  | VIO4                 | I/O | GPIO[55]   | S1_SD6           | UART_TX  | SPI_MISO | GPIO    | GPIO | UART_TX           | I2S_SD   | SPI_MISO         |

| D5  | VIO4                 | I/O | GPIO[56]   | S1_SD7           | UART_RX  | SPI_MOSI | GPIO    | GPIO | UART_RX           | I2S_WS   | SPI_MOSI         |

| C4  | VIO4                 | I/O | GPIO[57]   | MMC1_R<br>ST_OUT | GPIO     | GPIO     | GPIO    | GPIO | I2S_MCLK          | I2S_MCLK | I2S_MCLK         |

|     | FX3S Pin Description |     |                  |                       |  |  |

|-----|----------------------|-----|------------------|-----------------------|--|--|

| Pin | Power Domain         | I/O | Name             | USB Port              |  |  |

| C9  | VBUS/<br>VBATT       | I   | OTG_ID           | OTG_ID                |  |  |

| A3  | U3RX<br>VDDQ         | I   | SSRXM            | SSRX-                 |  |  |

| A4  | U3RX<br>VDDQ         | I   | SSRXP            | SSRX+                 |  |  |

| A6  | U3TX<br>VDDQ         | 0   | SSTXM            | SSTX-                 |  |  |

| A5  | U3TX<br>VDDQ         | 0   | SSTXP            | SSTX+                 |  |  |

| A9  | VBUS/<br>VBATT       | I/O | DP               | D+                    |  |  |

| A10 | VBUS/<br>VBATT       | I/O | DM               | D-                    |  |  |

| A11 |                      |     | NC               | No connect            |  |  |

|     |                      |     |                  | Crystal/Clocks        |  |  |

| B2  | CVDDQ                | ı   | FSLC[0]          | FSLC[0]               |  |  |

| C6  | AVDD                 | I/O | XTALIN           | XTALIN                |  |  |

| C7  | AVDD                 | I/O | XTALOUT          | XTALOUT               |  |  |

| B4  | CVDDQ                | I   | FSLC[1]          | FSLC[1]               |  |  |

| E6  | CVDDQ                | I   | FSLC[2]          | FSLC[2]               |  |  |

| D7  | CVDDQ                | I   | CLKIN            | CLKIN                 |  |  |

| D6  | CVDDQ                | I   | CLKIN_32         | CLKIN_32              |  |  |

|     |                      |     |                  | I2C and JTAG          |  |  |

| D9  | VIO5                 | I/O | I2C_GPIO[5<br>8] | I2C_SCL               |  |  |

| D10 | VIO5                 | I/O | I2C_GPIO[5<br>9] | I2C_SDA               |  |  |

| E7  | VIO5                 | I   | TDI              | TDI                   |  |  |

| C10 | VIO5                 | 0   | TDO              | TDO                   |  |  |

| B11 | VIO5                 | ı   | TRST#            | TRST#                 |  |  |

| E8  | VIO5                 | I   | TMS              | TMS                   |  |  |

| F6  | VIO5                 | I   | TCK              | TCK                   |  |  |

| D11 | VIO5                 | 0   | O[60]            | Charger detect output |  |  |

|     | FX3S Pin Description |     |          |                                                                                          |  |  |  |

|-----|----------------------|-----|----------|------------------------------------------------------------------------------------------|--|--|--|

| Pin | Power Domain         | I/O | Name     | Power                                                                                    |  |  |  |

| E10 |                      | PWR | VBATT    |                                                                                          |  |  |  |

| B10 |                      | PWR | VDD      |                                                                                          |  |  |  |

| A1  |                      | PWR | U3VSSQ   |                                                                                          |  |  |  |

| E11 |                      | PWR | VBUS     |                                                                                          |  |  |  |

| D8  |                      | PWR | VSS      |                                                                                          |  |  |  |

| H11 |                      | PWR | VIO1     |                                                                                          |  |  |  |

| E2  |                      | PWR | VSS      |                                                                                          |  |  |  |

| L9  |                      | PWR | VIO1     |                                                                                          |  |  |  |

| G1  |                      | PWR | VSS      |                                                                                          |  |  |  |

| F1  |                      | PWR | VIO2     |                                                                                          |  |  |  |

| G11 |                      | PWR | VSS      |                                                                                          |  |  |  |

| E3  |                      | PWR | VIO3     |                                                                                          |  |  |  |

| L1  |                      | PWR | VSS      |                                                                                          |  |  |  |

| B1  |                      | PWR | VIO4     |                                                                                          |  |  |  |

| L6  |                      | PWR | VSS      |                                                                                          |  |  |  |

| В6  |                      | PWR | CVDDQ    |                                                                                          |  |  |  |

| B5  |                      | PWR | U3TXVDDQ |                                                                                          |  |  |  |

| A2  |                      | PWR | U3RXVDDQ |                                                                                          |  |  |  |

| C11 |                      | PWR | VIO5     |                                                                                          |  |  |  |

| L11 |                      | PWR | VSS      |                                                                                          |  |  |  |

| A7  |                      | PWR | AVDD     |                                                                                          |  |  |  |

| B7  |                      | PWR | AVSS     |                                                                                          |  |  |  |

| C3  |                      | PWR | VDD      |                                                                                          |  |  |  |

| B8  |                      | PWR | VSS      |                                                                                          |  |  |  |

| E9  |                      | PWR | VDD      |                                                                                          |  |  |  |

| B9  |                      | PWR | VSS      |                                                                                          |  |  |  |

| F11 |                      | PWR | VDD      |                                                                                          |  |  |  |

| H1  |                      | PWR | VDD      |                                                                                          |  |  |  |

| L7  |                      | PWR | VDD      |                                                                                          |  |  |  |

| J11 |                      | PWR | VDD      |                                                                                          |  |  |  |

| L5  |                      | PWR | VDD      |                                                                                          |  |  |  |

| K4  |                      | PWR | VSS      |                                                                                          |  |  |  |

| L3  |                      | PWR | VSS      |                                                                                          |  |  |  |

| K3  |                      | PWR | VSS      |                                                                                          |  |  |  |

| L2  |                      | PWR | VSS      |                                                                                          |  |  |  |

| A8  |                      | PWR | VSS      |                                                                                          |  |  |  |

|     |                      |     |          | Precision Resistors                                                                      |  |  |  |

| C8  | VBUS/<br>VBATT       | I/O | R_usb2   | Precision resistor for USB 2.0 (Connect a 6.04 kΩ ±1% resistor between this pin and GND) |  |  |  |

| В3  | U3TX<br>VDDQ         | I/O | R_usb3   | Precision resistor for USB 3.0 (Connect a 200 Ω ±1% resistor between this pin and GND)   |  |  |  |

# **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the

outputs in high Z state......VCC+0.3

(VCC is the corresponding I/O voltage)

Static discharge voltage ESD protection levels:

- ± 2.2-KV HBM based on JESD22-A114

- Additional ESD protection levels on D+, D–, and GND pins, and serial peripheral pins

■ ± 6-KV contact discharge, ± 8-KV air gap discharge based on IEC61000-4-2 level 3A, ± 8-KV contact discharge, and ± 15-KV air gap discharge based on IEC61000-4-2 level 4C

| Latch-up current                        | > 200 mA |

|-----------------------------------------|----------|

| Maximum output short-circuit current    |          |

| for all I/O configurations. (Vout = 0V) | –100 mA  |