### 1.0 Features

- Generates one bank of ten clock outputs (1Y0 to 1Y9) from one reference clock input (CLK)

- Designed to meet the PLL Component Specifications as noted in the PC133 SDRAM Registered DIMM Design Specification

- External feedback input (FBIN) to synchronize all clock outputs to the reference input

- Operating frequency 25MHz to 140MHz

- Tight tracking skew (spread-spectrum tolerant)

- On-chip 25Ω series damping resistors for driving point-to-point loads

- Output enable (G) enables or disables low all clock outputs

- Available with an auto power-down option that turns off the PLL and forces all outputs low when the reference clock stops (FS612510-02)

- Packaged in a 24-pin TSSOP

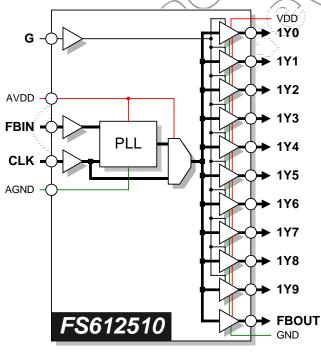

### Figure 1: Block Diagram

## 2.0 Description

The FS612510 is a low skew, low jitter CMOS zero-delay phase-lock loop (PLL) clock buffer IC designed for high-speed motherboard applications, such as those using 133MHz SDRAM.

Ten buffered clock outputs are derived from an onboard open-loop PLL. The PLL aligns the frequency and phase of all output clocks to the reference input clock CLK, including an FBOUT clock that feeds back to FBIN to close the loop. Multiple power and ground supplies help reduce the effects of noise on device performance.

All ten outputs 1Y0 to 1Y9 are enabled and disabled low by the active-high G signal. The PLL can be bypassed for test purposes by pulling AVDD to ground.

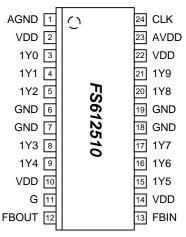

## Figure 2: Pin Configuration

#### **Table 1: Function Table**

| PLL        |      | INPUT |     | Ουτ     | PUT   |

|------------|------|-------|-----|---------|-------|

| FLL        | AVDD | G     | CLK | 1Y0-1Y9 | FBOUT |

| ١٧         | Н    | L     | L   | L       | L     |

| Dela       | Н    | L     | Н   | L       | Н     |

| Zero-Delay | Н    | Н     | L   | L       | L     |

| Ž          | Н    | Н     | Н   | Н       | Н     |

| ss         | L    | L     | L   | L       | L     |

| ypa:       | L    | L     | Н   | L       | Н     |

| PLL Bypass | L    | Н     | L   | L       | L     |

| Ы          | L    | Н     | Н   | н       | н     |

American Microsystems, Inc. reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

### **Table 2: Pin Descriptions**

Key: AI = Analog Input; AO = Analog Output; DI = Digital Input; DI<sup>U</sup> = Input with Internal Pull-Up; DI<sub>D</sub> = Input with Internal Pull-Down; DIO = Digital Input/Output; DI-3 = Three-Level Digital Input, DO = Digital Output; P = Power/Ground; # = Active Low pin

| PIN           | TYPE | NAME  | DESCRIPTION                                                                                                                                                         |                                  |

|---------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 3             | DO   | 1Y0   | Clock output                                                                                                                                                        |                                  |

| 4             | DO   | 1Y1   | Clock output                                                                                                                                                        |                                  |

| 5             | DO   | 1Y2   | Clock output                                                                                                                                                        |                                  |

| 8             | DO   | 1Y3   | Clock output                                                                                                                                                        |                                  |

| 9             | DO   | 1Y4   | Clock output                                                                                                                                                        | Enabled by G                     |

| 15            | DO   | 1Y5   | Clock output                                                                                                                                                        | Enabled by G                     |

| 16            | DO   | 1Y6   | Clock output                                                                                                                                                        |                                  |

| 17            | DO   | 1Y7   | Clock output                                                                                                                                                        |                                  |

| 20            | DO   | 1Y8   | Clock output                                                                                                                                                        |                                  |

| 21            | DO   | 1Y9   | Clock output                                                                                                                                                        |                                  |

| 23            | Р    | AVDD  | Power Supply / Test mode enable. This pin provides the power supply to the interpin is pulled low, the PLL is bypassed and the output clocks directly follow the in | ernal PLL. When the<br>put clock |

| 1             | Р    | AGND  | PLL supply ground                                                                                                                                                   |                                  |

| 24            | DI   | CLK   | Reference clock input (Note: -02 version has a pull-down on this pin)                                                                                               |                                  |

| 13            | DI   | FBIN  | Feedback clock input; must be connected to FBOUT to complete the loop                                                                                               |                                  |

| 12            | DO   | FBOUT | Feedback output clock                                                                                                                                               |                                  |

| 11            | DI   | G     | Output enable stops all clocks (1Y0 – 1Y9) in a low state when this pin is low                                                                                      |                                  |

| 6, 7, 18, 19  | Р    | GND   | Ground for all elock outputs                                                                                                                                        |                                  |

| 2, 10, 14, 22 | Р    | VDD   | Power supply for all clock outputs                                                                                                                                  |                                  |

|               |      |       |                                                                                                                                                                     |                                  |

### 3.0 Device Operation

The FS612510 is a zero-delay buffer intended for use on buffered PC133 SDRAM DIMMs.

The FS612510 precisely aligns the frequency and phase of the output clocks to the input CLK by use of an on-chip phase-lock loop (PLL). The PLL generates up to 10 low-skew, low-jitter copies of the CLK, with the outputs adjusted for 50% duty cycle.

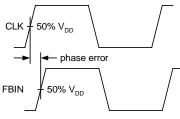

The FBOUT clock must be hardwired to the FBIN pin to complete the loop. The PLL actively adjusts the output clocks so that there is no phase error between the reference clock (CLK) and the feedback clock (FBIN).

Since the device uses a PLL to lock the output clocks to the input clock, there is a power-up stabilization time that is required for the PLL to achieve phase lock.

Note that all inputs and outputs use LVCMOS signal levels.

### 3.1 PLL Bypass

When the AVDD pin is pulled low, the reference clock signal bypasses the PLL and is muxed directly through to the outputs. The PLL is powered down, and device acts a fanout buffer.

Note that if AVDD is re-established, the PLL requires a power-up and stabilization time to lock to the input clock.

### 3.2 Output Enable/Disable

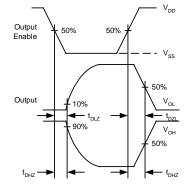

All ten outputs are enabled or disabled as a group by the G enable signal.

A logic-high on G input enables all the clock outputs to swing in phase with the reference clock. A logic-low on G forces all of the clock outputs to a logic-low state.

The function table Table 1 shows the effect of the G enable signal on the clock outputs.

### 3.3 Power-Down

The FS612510-02 version provides an auto power-down feature that shuts off the PLL, drives all outputs low, and places the device into a low current state if the reference clock stops. The power-down circuit is level sensitive, and detects either a DC high or low on the CLK input.

## 4.0 Tracking Skew

PLL-based buffer ICs may be required to follow a spreadspectrum modulated reference clock for frequencies greater than 66MHz. Spread spectrum modulation limits peak EMI emissions by intentionally introducing jitter onto a clock signal, effectively spreading the peak energy over a range of frequencies.

A downstream PLL, contained in a clock buffer IC such as this one, must carefully track the modulated input reference clock. A measure of how closely the downstream PLL follows the modulated clock is called the tracking skew. To ensure a tight tracking skew, the loop bandwidth of a downstream PLL is increased and the loop phase angle is reduced over that of typical PLL-based clock generators.

The type of modulation profile used impacts tracking skew. The maximum frequency change occurs at the profile limits where the modulation changes the slew rate polarity. To track the sudden reversal in clock frequency, the downstream PLL must have a large loop bandwidth. The ability of the downstream PLL to catch up to the modulating clock is determined by the loop transfer function phase angle.

The spread-spectrum reference clock should be either a triangle-wave or a non-linear (Lexmark) modulation profile, with a modulation frequency of 50kHz or less.

## 5.0 Electrical Specifications

### **Table 3: Absolute Maximum Ratings**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These conditions represent a stress rating only, and functional operation of the device at these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance, functionality, and reliability.

| PARAMETER                                                         | SYMBOL                                  | MIN.                  | MAX.                 | UNITS |

|-------------------------------------------------------------------|-----------------------------------------|-----------------------|----------------------|-------|

| Supply Voltage, dc, Clock Buffers (V <sub>SS</sub> = ground)      | AV <sub>DD</sub>                        | V <sub>ss</sub> - 0.5 | 7                    | V     |

| Supply Voltage, dc, Core                                          | V <sub>DD</sub>                         | V <sub>ss</sub> - 0.5 | $\rho$ 7             | V     |

| Input Voltage, dc                                                 | $\langle \langle V_{I} \rangle \rangle$ | V <sub>S\$</sub> -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage, dc                                                | N <sub>o</sub>                          | V <sub>SS</sub> - 0.5 | V <sub>DD</sub> +0.5 | V     |

| Input Clamp Current, dc ( $V_1 < 0$ or $V_1 > V_{DD}$ )           |                                         | 0-50                  | 50                   | mA    |

| Output Clamp Current, dc ( $V_1 < 0$ or $V_1 > V_{DD}$ )          | Іок                                     | -50                   | 50                   | mA    |

| Storage Temperature Range (non-condensing)                        | Tş                                      | -65                   | 150                  | °C    |

| Ambient Temperature Range, Under Bias                             | TA                                      | -55                   | 125                  | °C    |

| Junction Temperature                                              |                                         |                       | 125                  | °C    |

| Lead Temperature (soldering, 10s)                                 |                                         |                       | 260                  | °C    |

| Static Discharge Voltage Protection (MIL-STD 883E, Method 3015.7) | $\langle \vee \rangle$                  |                       | 2                    | kV    |

CAUTION: ELECTROSTATIC SENSITIVE DEVICE

Permanent damage resulting in a loss of functionality or performance may occur if this device is subjected to a high-energy electrostatic discharge.

### **Table 4: Operating Conditions**

| PARAMETER                           | SYMBOL           | CONDITIONS/DESCRIPTION | MIN. | TYP. | MAX. | UNITS |

|-------------------------------------|------------------|------------------------|------|------|------|-------|

| Supply Voltage, Core and Outputs    | V <sub>DD</sub>  | 3.3V ± 10%             | 3.0  | 3.3  | 3.6  | V     |

| Ambient Operating Temperature Range | T <sub>A</sub>   |                        | 0    |      | 70   | °C    |

| Output Load Capacitance             | CL               |                        |      |      | 15   | pF    |

| Input Frequency                     | f <sub>CLK</sub> | CLK                    | 50   |      | 140  | MHz   |

| Input Duty Cycle                    |                  | CLK                    | 40   |      | 60   | %     |

| Input Rise/Fall Time                |                  | CLK                    |      |      | 3    | ns    |

### **Table 5: DC Electrical Specifications**

Unless otherwise stated, all power supplies = 3.3V%, no load on any output, and ambient temperature range T<sub>A</sub> = 0°C to 70°C. Parameters denoted with an asterisk (\*) represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are ± 30 from typical. Negative currents indicate current flows out of the device.

| PARAMETER                        | SYMBOL                  | CONDITIONS/DESCRIPTION                               | MIN.                     | TYP. | MAX.                 | UNITS |

|----------------------------------|-------------------------|------------------------------------------------------|--------------------------|------|----------------------|-------|

| Overall                          |                         |                                                      |                          |      |                      |       |

| Supply Current, Dynamic          |                         | f <sub>CLK</sub> = 133.33MHz; V <sub>DD</sub> = 3.3V | $\sim$                   | 135  |                      | mA    |

| Supply Current, Static           | I <sub>DDL</sub>        | Outputs low; V <sub>DD</sub> = 3.3V                  |                          | 3    |                      | mA    |

| Output Enable Input (G)          |                         |                                                      | (0                       |      |                      |       |

| High-Level Input Voltage         | VIH                     |                                                      | 2.0                      | 9    | V <sub>DD</sub> +0.3 | V     |

| Low-Level Input Voltage          | VIL                     |                                                      | V <sub>SS</sub> -0.3     |      | 0.8                  | V     |

| Input Leakage Current            | I,                      |                                                      | -5                       |      | 5                    | μA    |

| Clock Inputs (CLK, FBIN)         |                         |                                                      | $\mathcal{O}\mathcal{O}$ |      |                      |       |

| High-Level Input Voltage         | V <sub>IH</sub>         |                                                      | 2.0                      |      | V <sub>DD</sub> +0.3 | V     |

| Low-Level Input Voltage          | V <sub>IL</sub>         |                                                      | V <sub>SS</sub> -0.3     |      | 0.8                  | V     |

| Input Leakage Current            | L                       | -01 version                                          | -5                       |      | 5                    |       |

| input Leakage Current            |                         | -02 version has a pull-down on CLK                   |                          | 28   |                      | μA    |

| Input Loading Capacitance *      | C <sub>L(in)</sub>      | As seen by an external clock driver                  |                          | 4    |                      | pF    |

| Clock Outputs (1Y0:9, FBOUT)     |                         |                                                      |                          |      |                      |       |

| High-Level Output Source Current | $\langle \cdot \rangle$ | $V_{DD} = 2.9V, V_{O} = 2.0V$                        |                          | -18  | -12                  | mA    |

| High-Level Output Source Current | NOH                     | $V_{DD} = 3.7 V, V_{O} = 2.0 V$                      |                          | -35  | -12                  | ШA    |

| Low-Level Output Sink Current    |                         | $V_{DD} = 2.9V, V_{O} = 0.8V$                        | 12                       | 16   |                      | mA    |

| Low-Level Output Sink Current    |                         | $V_{pp} = 3.7V, V_0 = 0.8V$                          | 12                       | 17   |                      | ШA    |

| Output Impedance                 | Zo (                    | $\langle \mathcal{A} \rangle$                        |                          | 33   |                      | Ω     |

| Tristate Output Current          | Toz                     |                                                      | -10                      |      | 10                   | μA    |

| Short Circuit Source Current*    | Нозн                    | $V_0 = 0V$ ; shorted for 30s, max.                   |                          | -60  |                      | mA    |

| Short Circuit Sink Current *     | IOSL                    | $V_0 = 3.3V$ ; shorted for 30s, max.                 |                          | 90   |                      | mA    |

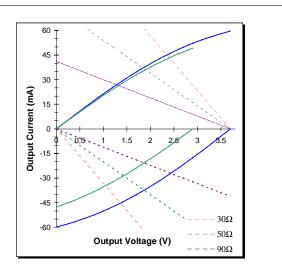

## Table 6: Clock Output Drive (1Y0:4, 2Y0:3, FBOUT)

| Voltage | age Low Drive Current (mA) |     | High Drive C | Current (mA) |

|---------|----------------------------|-----|--------------|--------------|

| 0.1 V   | -47                        | -59 | 2            | 2            |

| 0.2 V   | -45                        | -58 | 4            | 4            |

| 0.4 V   | -43                        | -56 | 8            | 9            |

| 0.6 V   | -40                        | -55 | 12           | 13           |

| 0.8 V   | -38                        | -52 | 16           | 17           |

| 1.0 V   | -35                        | -50 | 20           | 21           |

| 1.2 V   | -32                        | -47 | 24           | 25           |

| 1.4 V   | -29                        | -45 | 27           | 29           |

| 1.6 V   | -26                        | -41 | 31           | 33           |

| 1.8 V   | -22                        | -38 | 34           | 36           |

| 2.0 V   | -18                        | -35 | 38           | 40           |

| 2.2 V   | -15                        | -31 | 41           | 43           |

| 2.4 V   | -10                        | -28 | 43           | 46           |

| 2.6 V   | -6                         | -24 | 45           | 49           |

| 2.8 V   | -2                         | -20 | 48           | 51           |

| 3.0 V   | 0                          | -15 | 49           | 53           |

| 3.3 V   |                            | -9  |              | 56           |

| 1       | 1                          |     |              |              |

### **Table 7: AC Timing Specifications**

Unless otherwise stated, all power supplies = 3.3V, no load on any output, and ambient temperature T<sub>A</sub> = 25°C. Parameters denoted with an asterisk (represent nominal characterization data and are not currently production tested to any specific limits. MIN and MAX characterization data are ± 3σ from typical.

| PARAMETER                    | SYMBOL             | CONDITIONS/DESCRIPTION                                                      | MIN.                      | TYP.          | MAX.   | UNITS |

|------------------------------|--------------------|-----------------------------------------------------------------------------|---------------------------|---------------|--------|-------|

| Overall                      |                    |                                                                             |                           |               |        |       |

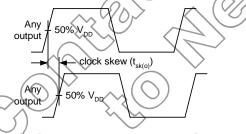

| Skew, Output to Output *     | t <sub>sk(o)</sub> | Measured on the rising edge at 1.65V; $C_L = 15pF$                          |                           |               | 150    | ps    |

| Skew, Tracking *             |                    | Measured using a –0.5% 31.5kHz spread spectrum reference clock at 133.33MHz |                           | 2             | 150    | ps    |

| Static Phase Error *         |                    | From rising edge on CLK to rising edge on FBIN                              | C                         | <i>P-</i> 120 |        | ps    |

| Clock Stabilization Time *   |                    | Time required for the PLL to achieve phase lock                             | $\langle \rangle$         |               | 3      | ms    |

| Loop Bandwidth *             |                    | For calculation of Tracking Skew                                            | $\langle \rangle \rangle$ |               | 1.2    | MHz   |

| Phase Angle *                |                    | For calculation of Tracking Skew                                            |                           |               | -0.031 | 0     |

| Clock Outputs (1Y0:9, FBOUT) | U                  |                                                                             | $\mathcal{D}$             |               |        |       |

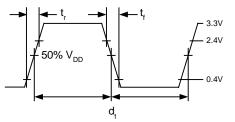

| Duty Cycle *                 | dt                 | Ratio of high pulse width to one clock period, measured at 1.65V            | 45                        |               | 55     | %     |

| Jitter, Cycle-Cycle *        | t <sub>j(CC)</sub> | Adjacent cycles at 1.65V                                                    | -75                       |               | +75    | ps    |

| Jitter, Period (peak-peak) * | t <sub>j(∆P)</sub> | From rising edge to next rising edge at 1.65V                               |                           |               |        |       |

| Rise Time *                  | tr                 | $V_Q = 0.4V$ to 2.0V; $C_L = 15pF$                                          |                           | 1.2           |        | ns    |

| Fall Time *                  | t <sub>f</sub>     | $V_0 = 2.0V$ to 0.4V; $C_L = 15pF$                                          |                           | 1.4           |        | ns    |

| Enable Delay *               | t <sub>DLH</sub>   | via G                                                                       | 1                         |               | 10     | ns    |

| Disable Delay *              | ton                | via G                                                                       | 1                         |               | 10     | ns    |

## Figure 3: Clock Skew Measurement

### Figure 5: Timing Measurement Points

### Figure 4: Phase Error Measurement

### Figure 6: Output Enable Measurement

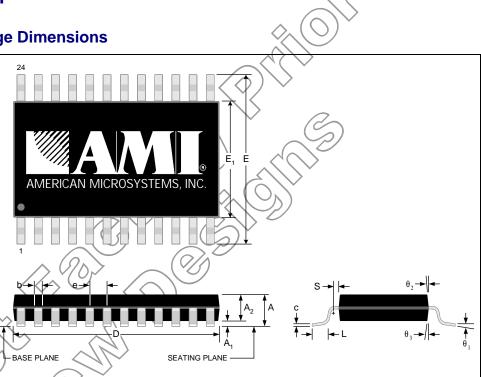

## 6.0 Package Information

### Table 8: 24-pin TSSOP Package Dimensions

|            | DIMENSIONS |        |          |        |  |

|------------|------------|--------|----------|--------|--|

|            | INC        | HES    | MILLIM   | IETERS |  |

|            | MIN.       | MAX.   | MIN.     | MAX.   |  |

| А          | -          | 0.047  | -        | 1.20   |  |

| $A_1$      | 0.002      | 0.006  | 0.05     | 0.15   |  |

| $A_2$      | 0.0315     | 0.0413 | 0.80     | 1.05   |  |

| b          | 0.0075     | 0.0118 | 0.19     | 0.30   |  |

| С          | 0.0035     | 0.0079 | 0.09     | 0.20   |  |

| D          | 0.303      | 0.311  | 7.70     | 7.90   |  |

| E1         | 0.169      | 0.177  | 4.30     | 4.50   |  |

| Е          | 0.2        | 252    | 6.40 BSC |        |  |

| е          | 0.0        | 256    | 0.65 BSC |        |  |

| L          | 0.0177     | 0.0295 | 0.45     | 0.75   |  |

| S          | 0.0079     | -      | 0.20     | - )    |  |

| $\theta_1$ | 0°         | 8°     | 0°       | 8°     |  |

| $\theta_2$ | 12 F       | REF    | 12       | REF    |  |

| $\theta_3$ | 12 F       | REF    | 12       | REF    |  |

## Table 9: 24-pin TSSOP Package Characteristics

| PARAMETER                               | SYMBOL          | CONDITIONS/DESCRIPTION                            | TYP.  | UNITS |

|-----------------------------------------|-----------------|---------------------------------------------------|-------|-------|

| Thermal Impedance, Junction to Free-Air | $\Theta_{JA}$   | Air flow = 0 m/s                                  | 84    | °C/W  |

| Lead Inductance, Self                   | L <sub>11</sub> | Longest lead                                      | 1.7   | nH    |

| Lead Inductance, Mutual                 | L <sub>12</sub> | Longest lead to any 1 <sup>st</sup> adjacent lead | 0.6   | nH    |

| Lead Inductance, Mutual                 | L <sub>13</sub> | Longest lead to any 2 <sup>nd</sup> adjacent lead | 0.24  |       |

| Lead Capacitance, Bulk                  | C <sub>11</sub> | Longest lead to V <sub>ss</sub>                   | 0.3   | pF    |

| Lead Capacitance, Mutual                | C <sub>12</sub> | Longest lead to any 1 <sup>st</sup> adjacent lead | 0.1   | ۶L    |

| Leau Capacitance, Mutual                | C <sub>13</sub> | Longest lead to any 2 <sup>nd</sup> adjacent lead | 0.007 | pF    |

## 7.0 Ordering Information

### Table 10: Device Ordering Codes

| DEVICE<br>NUMBER | ORDERING CODE | PACKAGE TYPE                                        | OPERATING<br>TEMPERATURE RANGE | SHIPPING<br>CONFIGURATION |

|------------------|---------------|-----------------------------------------------------|--------------------------------|---------------------------|

| FS612510-01      | 12055-102     | 24-pin TSSOP<br>(Thin Shrink Small Outline Package) | 0°C to 70°C (Commercial)       | Tape and Reel             |

| FS612510-02      | 12055-103     | 24-pin TSSOP<br>(Thin Shrink Small Outline Package) | 0°C to 70°C (Commercial)       | Tape and Reel             |

|                  |               |                                                     | E CONT                         |                           |

#### Copyright © 2000 American Microsystems, Inc.

Devices sold by AMI are covered by the warranty and patent indemnification provisions appearing in its Terms of Sale only. AMI makes no warranty, express, statutory implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. AMI makes no warranty of merchantability or fitness for any purposes. AMI reserves the right to discontinue production and change specifications and prices at any time and without notice. AMI's products are intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment, are specifically not recommended without additional processing by AMI for such applications.

American Microsystems, Inc., 2300 Buckskin Rd., Pocatello, ID 83201, (208) 233-4690, FAX (208) 234-6796, WWW Address: http://www.amis.com E-mail: tgp@amis.com