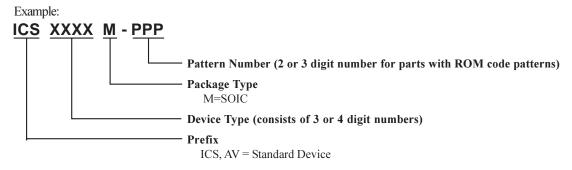

# Pentium/Pro™ System Clock Chip

#### **General Description**

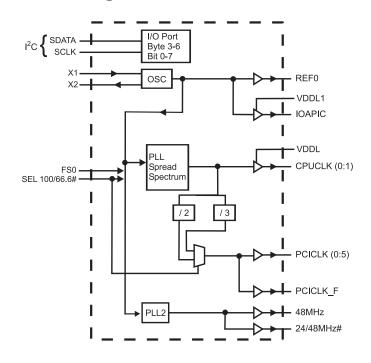

The ICS9148-47 is part of a reduced pin count two-chip clock solution for designs using an Intel BX style chipset. Companion SDRAM buffers are ICS9179-11 and -12.

There are two PLLs, with the first PLL capable of spread spectrum operation. Spread spectrum typically reduces system EMI by 8-10dB. The second PLL provides support for USB (48MHz) and 24MHz requirements. CPU frequencies up to 100MHz are supported.

The I<sup>2</sup>C interface allows stop clock programming, frequency selection, and spread spectrum operation to be programmed. Clock outputs include two CPU (2.5V or 3.3V), seven PCI (3.3V), one REF (3.3V), one IOAPIC (2.5V or 3.3V), one 48MHz, and one selectable 48/24MHz.

#### **Features**

- Generates system clocks for CPU, PCI, IOAPIC, 14.314 MHz, 48 and 24MHz.

- Supports single or dual processor systems

- Skew from CPU (earlier) to PCI clock 1 to 4ns

- Separate 2.5V and 3.3V supply pins

- 2.5V outputs: CPU, IOAPIC

- 3.3V outputs: PCI, REF

- No power supply sequence requirements

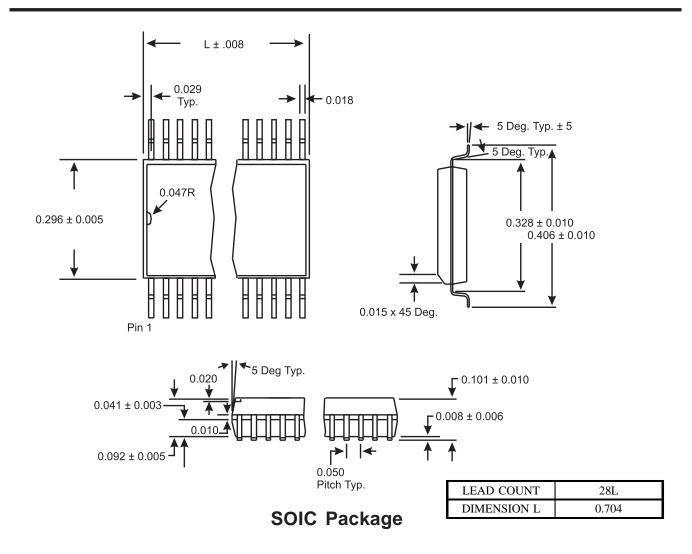

- 28 pin SOIC

- Spread Sectrum operation optional for PLL1

- CPU frequencies to 100MHz are supported.

## **Block Diagram**

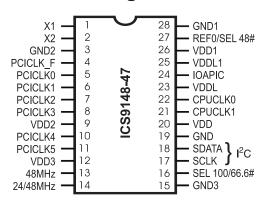

### **Pin Configuration**

28 pin SOIC

### **Power Groups**

VDD = Supply for PLL core VDD1 = REF0, X1, X2 VDD2 = PCICLK\_F, PCICLK (0:5) VDD3 = 48MHz VDDL = CPUCLK (0:1) VDDL1 = IOAPIC

### **Ground Groups**

GND = Ground Source Core GND1 = REF0, X1, X2 GND2 = PCICLK\_F, PCICLK (0:5) GND3=48MHz GNDL=CPUCLK (0:1)

Pentium is a trademark on Intel Corporation.

# ICS9148-47

# **Pin Descriptions**

| PIN NUMBER         | PIN NAME     | TYPE   | DESCRIPTION                                                                                       |

|--------------------|--------------|--------|---------------------------------------------------------------------------------------------------|

| 1                  | X1           | IN     | XTAL_IN 14.318MHz Crystal input, has internal 33pF load cap and feed back resistor from X2        |

| 2                  | X2           | OUT    | XTAL_OUT Crystal output, has internal load cap 33pF                                               |

| 3                  | GND2         | PWR    | Ground for PCI outputs                                                                            |

| 4                  | PCICLK_F     | OUT    | Free Running PCI output                                                                           |

| 5, 6, 7, 8, 10, 11 | PCICLK (0:5) | OUT    | PCI clock outputs. TTL compatible 3.3V                                                            |

| 6, 9               | VDD2         | PWR    | Power for PCICLK outputs, nominally 3.3V                                                          |

| 12                 | VDD3         | PWR    | Poer for 48MHz                                                                                    |

| 13                 | 48MHz        | OUT    | Fixed CLK output @ 48MHz                                                                          |

| 14                 | 24/48MHz     | OUT    | Fixed CLK output; 24MHz if pin 27 =1 at power up, 48MHz if pin 27=0 at power up.                  |

| 15                 | GND3         | PWR    | Ground for 48MHz                                                                                  |

| 16                 | SEL100/66.6# | IN     | Select pin for enabling 100MHz or 66.6MHz<br>H=100MHz, L=66.6MHz (PCI always synchronous 33.3MHz) |

| 17                 | SCLK         | IN     | Clock input for I <sup>2</sup> C input                                                            |

| 18                 | SDATA        | IN     | Data input for I <sup>2</sup> C input                                                             |

| 19                 | GND          | PWR    | Ground for CPUCLK (0:1)                                                                           |

| 20                 | VDD          | PWR    | Power for PLL core                                                                                |

| 21, 22             | CPUCLK (1:0) | OUT    | CPU and Host clock outputs nominally 2.5V                                                         |

| 23                 | VDDL         | PWR    | Power for CPU outputs, nominally 2.5V                                                             |

| 24                 | IOAPIC       | OUT    | IOAPIC clock output 14.318MHz.                                                                    |

| 25                 | VDDL         | PWR    | Power for IOAPIC                                                                                  |

| 26                 | VDD1         | PWR    | Power for REF outputs.                                                                            |

| 27                 | REF0/SEL 48# | OUT/IN | 14.318MHz clock output/Latched input at power up. When low, pin 14 is 48MHz.                      |

| 28                 | GND1         | PWR    | Ground for REF outputs, X1, X2.                                                                   |

## General I<sup>2</sup>C serial interface information

The information in this section assumes familiarity with I<sup>2</sup>C programming. For more information, contact ICS for an I<sup>2</sup>C programming application note.

#### How to Write:

- Send the address D2(H).

- Send two additional dummy bytes, a command code and byte count.

- Send the desired number of data bytes.

#### See the diagram below:

| Clock Generator<br>Address (7 bits)<br>A(6:0) & R/W# | ACK | + 8 bits<br>dummy<br>command code | ACK | + 8 bits<br>dummy Byte<br>count | ACK | Data Byte<br>1 | ACK | Data Byte<br>N | ACK |

|------------------------------------------------------|-----|-----------------------------------|-----|---------------------------------|-----|----------------|-----|----------------|-----|

| D2(H)                                                |     |                                   |     | Count                           |     |                |     |                |     |

Note that the acknowledge bit is sent by the clock chip, and pulls the data line low. There is no minimum of data bytes that must be sent.

#### How to Read:

- Send the address D3<sub>(H)</sub>.

- Send the byte count in binary coded decimal

- Read back the desired number of data bytes

#### See the diagram below:

| Clock Generator<br>Address (7 bits) |     | Byte  |     | Data Byte |     | Data Byte |

|-------------------------------------|-----|-------|-----|-----------|-----|-----------|

| A(6:0) & R/W#                       | ACK | Count | ACK | 1         | ACK | N         |

| D3(H)                               |     |       |     |           |     |           |

The following specifications should be observed:

1. Operating voltage for I<sup>2</sup>C pins is 3.3V

- Maximum data transfer rate (SCLK) is 100K bits/sec.

### ICS9148-47

### **Serial Bitmap**

Byte 3: Functionality & Frequency Select & Spread Slect Register

| Bit |                                                      | Do                                                         | escription                                                      |                                                                                                                              | PWD |

|-----|------------------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| 7   |                                                      | (I                                                         | Reserved)                                                       |                                                                                                                              | 0   |

|     | Bit<br>654                                           | CPU                                                        | PCI                                                             | Spread<br>Percentage                                                                                                         |     |

| 6:4 | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | 68.5<br>75.0<br>83.3<br>66.6<br>103<br>112<br>133.3<br>100 | 34.25<br>37.5<br>41.6<br>33.3<br>34.3<br>37.3<br>44.43<br>33.33 | ±0.5% Center<br>±0.5% Center<br>±0.5% Center<br>±0.5% Center<br>±0.5% Center<br>±0.5% Center<br>±0.5% Center<br>±0.5% Center | 0   |

| 3   | SEL1                                                 | uency is se<br>00/66.6#<br>uency is sel                    | ·                                                               | ardware select<br>:4 above                                                                                                   | 0   |

| 2   |                                                      | (I                                                         | Reserved)                                                       |                                                                                                                              |     |

| 10  | 01 - Tes<br>10 - Spr                                 | rmal operat<br>t mode<br>ead sprectru<br>state all out     | um ON                                                           |                                                                                                                              | 00  |

**Notes:** 1 = Enabled; 0 = Disabled, outputs held low

Byte 5:

| Bit | Pin#  | Pin Name | PWD | Descr           | iption        |

|-----|-------|----------|-----|-----------------|---------------|

| DIL | PIII# | Pin Name | PWD | Bit Value $= 0$ | Bit Value = 1 |

| 7   | 4     | PCICLK_F | 1   | Disabled (low)  | Enabled       |

| 6   | 11    | PCICLK5  | 1   | Disabled (low)  | Enabled       |

| 5   | 10    | PCICLK4  | 1   | Disabled (low)  | Enabled       |

| 4   | -     | -        | 0   | (Reserved)      | (Reserved)    |

| 3   | 8     | PCICLK3  | 1   | Disabled (low)  | Enabled       |

| 2   | 7     | PCICLK2  | 1   | Disabled (low)  | Enabled       |

| 1   | 6     | PCICLK1  | 1   | Disabled (low)  | Enabled       |

| 0   | 5     | PCICLK0  | 1   | Disabled (low)  | Enabled       |

**Notes:** 1 = Enabled; 0 = Disabled, outputs held low

Byte 4:

| Bit | Pin#    | Pin Name    | PWD | Descr               | iption        |

|-----|---------|-------------|-----|---------------------|---------------|

| DIL | F 1111# | riii Naiile | FWD | Bit Value = 0       | Bit Value = 1 |

| 7   | -       | -           | 1   | (Reserved)          | (Reserved)    |

| 6   | -       | -           | 1   | (Reserved)          | (Reserved)    |

| 5   | -       | -           | 1   | (Reserved)          | (Reserved)    |

| 4   | -       | -           | 1   | (Reserved)          | (Reserved)    |

| 3   | -       | -           | -   | (Reserved)          | (Reserved)    |

| 2   | 21      | CPUCLK1     | 1   | Disabled (low)      | Enabled       |

| 1   | -       | _           | 0   | (Reserved)          | (Reserved)    |

| 0   | 22      | CPUCLK0     | 1   | (Disabled)<br>(low) | Enabled       |

**Notes:** 1 = Enabled; 0 = Disabled, outputs held low

Note: PWD = Power-Up Default

Byte 6:

| Bit | Pin#  | Pin Name | PWD | Descr               | iption        |

|-----|-------|----------|-----|---------------------|---------------|

| DIL | PIII# | Pin Name | PWD | Bit Value = 0       | Bit Value = 1 |

| 7   | -     | -        | 0   | (Reserved)          | (Reserved)    |

| 6   | -     | -        | 0   | (Reserved)          | (Reserved)    |

| 5   | 24    | IOAPIC   | 1   | Disabled (low)      | Enabled       |

| 4   | -     | -        | 0   | (Reserved)          | (Reserved)    |

| 3   | -     | -        | 0   | (Reserved)          | (Reserved)    |

| 2   | -     | -        | 0   | (Reserved)          | (Reserved)    |

| 1   | 27    | REF0     | 1   | (Disabled)<br>(low) | Enabled       |

| 0   | 27    | REF0     | 1   | (Disabled)<br>(low) | Enabled       |

Notes:

$1 = \text{Enabled}; \quad 0 = \text{Disabled}, \text{ outputs held low}$

For pin 27, there are 2 output stages together for 1 pin. These 2 latches must be both 0 or 1 simultaneously or there will be a short to ground if one is disabled  $\,$  and the other is running.

### **Absolute Maximum Ratings**

Supply Voltage . . . . . . . . . . . . . . . . . 7.0 V

Logic Inputs ...... GND-0.5 V to V<sub>DD</sub>+0.5 V

Ambient Operating Temperature ...... 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . .  $-65^{\circ}$ C to  $+150^{\circ}$ C

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

### **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0$  - 70C; Supply Voltage  $V_{DD} = V_{DDL} = 3.3 \text{ V} + /-5\%$  (unless otherwise stated)

| PARAMETER                      | SYMBOL                  | CONDITIONS                                              | MIN           | TYP    | MAX            | UNITS |

|--------------------------------|-------------------------|---------------------------------------------------------|---------------|--------|----------------|-------|

| Input High Voltage             | $V_{\mathrm{IH}}$       |                                                         | 2             |        | $V_{DD} + 0.3$ | V     |

| Input Low Voltage              | $V_{\rm IL}$            |                                                         | $V_{SS}$ -0.3 |        | 0.8            | V     |

| Input High Current             | $I_{IH}$                | $V_{IN} = V_{DD}$                                       |               | 0.1    | 5              | μΑ    |

| Input Low Current              | $I_{\rm IL1}$           | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors | -5            | 2.0    |                | μΑ    |

| Input Low Current              | $I_{IL2}$               | V <sub>IN</sub> = 0 V; Inputs with pull-up resistors    | -200          | -100   |                | μΑ    |

| Operating                      | I <sub>DD3.3OP66</sub>  | C <sub>L</sub> = 0 pF; Select @ 66MHz                   |               | 60     | 170            | mA    |

| Supply Current                 | I <sub>DD3.3OP100</sub> | C <sub>L</sub> = 0 pF; Select @ 100MHz                  |               | 66     | 170            |       |

| Power Down                     | I <sub>DD3.3PD</sub>    | $C_L = 0$ pF; With input address to Vdd or GND          | )             | 3      | 650            | μΑ    |

| Supply Current                 |                         |                                                         |               |        |                |       |

| Input frequency                | $F_{i}$                 | $V_{DD} = 3.3 \text{ V};$                               |               | 14.318 |                | MHz   |

| Input Capacitance <sup>1</sup> | $C_{IN}$                | Logic Inputs                                            |               |        | 5              | pF    |

|                                | $C_{INX}$               | X1 & X2 pins                                            | 27            | 36     | 45             | pF    |

| Transition Time <sup>1</sup>   | T <sub>trans</sub>      | To 1st crossing of target Freq.                         |               |        | 3              | ms    |

| Settling Time <sup>1</sup>     | $T_{s}$                 | From 1st crossing to 1% target Freq.                    |               | 5      |                | ms    |

| Clk Stabilization <sup>1</sup> | $T_{STAB}$              | From $V_{DD} = 3.3 \text{ V}$ to 1% target Freq.        |               |        | 3              | ms    |

| Skew <sup>1</sup>              | T <sub>AGP-PCI1</sub>   | $V_T = 1.5 \text{ V};$                                  | 1             | 3.5    | 4              | ns    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

## **Electrical Characteristics - Input/Supply/Common Output Parameters**

$T_A = 0 - 70C$ ; Supply Voltage  $V_{DD} = 3.3 \text{ V} + /-5\%$ ,  $V_{DDL} = 2.5 \text{ V} + /-5\%$  (unless otherwise stated)

| PARAMETER                    | SYMBOL                  | CONDITIONS                                     | MIN | TYP | MAX | UNITS |

|------------------------------|-------------------------|------------------------------------------------|-----|-----|-----|-------|

| Operating                    | IDD2.50P66              | $C_L = 0 \text{ pF}$ ; Select @ 66.8 MHz       |     | 16  | 72  | mA    |

| Supply Current               | I <sub>DD2.5OP100</sub> | $C_L = 0 \text{ pF}$ ; Select @ 100 MHz        |     | 23  | 100 | mA    |

| Power Down Supply<br>Current | I <sub>DD2.5PD</sub>    | $C_L = 0$ pF; With input address to Vdd or GND |     | 10  | 100 | μΑ    |

| gr 1                         | tcpu-agp                |                                                | 0   | 0.5 | 1   | ns    |

| Skew                         | tcpu-pci2               | $V_T = 1.5 \text{ V}; V_{TL} = 1.25 \text{ V}$ | 1   | 2.6 | 4   | ns    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

#### **Electrical Characteristics - CPUCLK**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3 \text{ V} + / -5\%$ ,  $V_{DDL} = 2.5 \text{ V} + / -5\%$ ;  $C_L = 20 \text{ pF}$  (unless otherwise stated)

|                        |                                  | 1 2 1                                            |      |      |      |       |

|------------------------|----------------------------------|--------------------------------------------------|------|------|------|-------|

| PARAMETER              | SYMBOL                           | CONDITIONS                                       | MIN  | TYP  | MAX  | UNITS |

| Output High Voltage    | $V_{\mathrm{OH2B}}$              | $I_{OH} = -12.0 \text{ mA}$                      | 2    | 2.3  |      | V     |

| Output Low Voltage     | $V_{OL2B}$                       | $I_{OL} = 12 \text{ mA}$                         |      | 0.2  | 0.4  | V     |

| Output High Current    | $I_{OH2B}$                       | $V_{OH} = 1.7 \text{ V}$                         |      | -41  | -19  | mA    |

| Output Low Current     | $I_{OL2B}$                       | $V_{OL} = 0.7 \text{ V}$                         | 19   | 37   |      | mA    |

| Rise Time              | $t_{r2B}^{1}$                    | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.0 \text{ V}$ |      | 1.25 | 1.6  | ns    |

| Fall Time              | $t_{f2B}^{1}$                    | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.4 \text{ V}$ |      | 1    | 1.6  | ns    |

| Duty Cycle             | $d_{t2B}^{1}$                    | $V_{\rm T} = 1.25 \text{ V}$                     | 45   | 48   | 55   | %     |

| Skew                   | $t_{sk2B}^{1}$                   | $V_T = 1.25 \text{ V}$                           |      | 30   | 175  | ps    |

| Jitter, Cycle-to-cycle | t <sub>jcyc-cyc2B</sub> 1        | $V_T = 1.25 \text{ V}$                           |      | 150  | 250  | ps    |

| Jitter, One Sigma      | $t_{j1s2B}^{1}$                  | $V_T = 1.25 \text{ V}$                           |      | 40   | 150  | ps    |

| Jitter, Absolute       | t <sub>jabs2B</sub> <sup>1</sup> | $V_T = 1.25 \text{ V}$                           | -250 | 140  | +250 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - PCICLK**

$T_{A} = 0 \text{ - } 70C; \; V_{DD} = V_{DDL} = 3.3 \; V \text{ +/-5\%} \, ; \; C_{L} = 30 \; pF$

|                                |                  | *                                                |      |     |     |       |

|--------------------------------|------------------|--------------------------------------------------|------|-----|-----|-------|

| PARAMETER                      | SYMBOL           | CONDITIONS                                       | MIN  | TYP | MAX | UNITS |

| Output High Voltage            | V <sub>OH1</sub> | $I_{OH} = -11 \text{ mA}$                        | 2.4  | 3.1 |     | V     |

| Output Low Voltage             | V <sub>OL1</sub> | $I_{OL} = 9.4 \text{ mA}$                        |      | 0.1 | 0.4 | V     |

| Output High Current            | Іон1             | $V_{OH} = 2.0 \text{ V}$                         |      | -62 | -22 | mA    |

| Output Low Current             | I <sub>OL1</sub> | $V_{OL} = 0.8 \text{ V}$                         | 16   | 57  |     | mA    |

| Rise Time <sup>1</sup>         | $t_{r1}$         | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |      | 1.5 | 2   | ns    |

| Fall Time <sup>1</sup>         | tfi              | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |      | 1.1 | 2   | ns    |

| Duty Cycle <sup>1</sup>        | $d_{t1}$         | $V_T = 1.5 \text{ V}$                            | 45   | 50  | 55  | %     |

| Skew <sup>1</sup>              | $t_{sk1}$        | $V_T = 1.5 \text{ V}$                            |      | 140 | 500 | ps    |

| Jitter, One Sigma <sup>1</sup> | tj1s1            | $V_T = 1.5 \text{ V}$                            |      | 17  | 150 | ps    |

| Jitter, Absolute <sup>1</sup>  | tjabs1           | $V_T = 1.5 \text{ V}$                            | -500 | 70  | 500 | ps    |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - IOAPIC**

$T_A = 0 - 70C$ ;  $V_{DD} = 3.3 \text{ V} + /-5\%$ ,  $V_{DDL} = 2.5 \text{ V} + /-5\%$ ;  $C_L = 20 \text{ pF}$

| PARAMETER                      | SYMBOL            | CONDITIONS                                       | MIN | TYP  | MAX | UNITS |

|--------------------------------|-------------------|--------------------------------------------------|-----|------|-----|-------|

| Output High Voltage            | V <sub>OH4B</sub> | $I_{OH} = -18 \text{ mA}$                        | 2   | 2.2  |     | V     |

| Output Low Voltage             | V <sub>OL4B</sub> | $I_{OL} = 18 \text{ mA}$                         |     | 0.33 | 0.4 | V     |

| Output High Current            | Іон4в             | V <sub>OH</sub> = 1.7 V                          |     | -41  | -28 | mA    |

| Output Low Current             | I <sub>OL4B</sub> | $V_{OL} = 0.7 \text{ V}$                         | 29  | 37   |     | mA    |

| Rise Time <sup>1</sup>         | $T_{r4B}$         | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.0 \text{ V}$ |     | 1.3  | 1.6 | ns    |

| Fall Time <sup>1</sup>         | $T_{f4B}$         | $V_{OH} = 2.0 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1.1  | 1.6 | ns    |

| Duty Cycle <sup>1</sup>        | D <sub>t4B</sub>  | $V_T = 1.25 \text{ V}$                           | 45  | 54   | 55  | %     |

| Skew <sup>1</sup>              | $t_{sk4B}^{1}$    | $V_T = 1.25 \text{ V}$                           |     | 60   | 250 | ps    |

| Jitter, One Sigma <sup>1</sup> | Tj1s4B            | $V_T = 1.25 \text{ V}$                           |     | 1    | 3   | %     |

| Jitter, Absolute <sup>1</sup>  | Tjabs4B           | $V_T = 1.25 \text{ V}$                           | -5  |      | 5   | %     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

### **Electrical Characteristics - 48, 24 MHz**

$T_A = 0$  - 70C;  $V_{DD} = V_{DDL} = 3.3 \text{ V} + /-5\%$ ;  $C_L = 20 \text{ pF}$  (unless otherwise stated)

| PARAMETER                      | SYMBOL           | CONDITIONS                                       | MIN | TYP  | MAX | UNITS |

|--------------------------------|------------------|--------------------------------------------------|-----|------|-----|-------|

| Output High Voltage            | V <sub>OH5</sub> | $I_{OH} = -12 \text{ mA}$                        | 2.6 | 3    |     | V     |

| Output Low Voltage             | V <sub>OL5</sub> | $I_{OL} = 9 \text{ mA}$                          |     | 0.14 | 0.4 | V     |

| Output High Current            | Іон5             | V <sub>OH</sub> = 2.0 V                          |     | -44  | -22 | mA    |

| Output Low Current             | I <sub>OL5</sub> | $V_{OL} = 0.8 \text{ V}$                         | 16  | 42   |     | mA    |

| Rise Time <sup>1</sup>         | t <sub>r</sub> 5 | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |     | 1.2  | 4   | ns    |

| Fall Time <sup>1</sup>         | t <sub>5</sub>   | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1.2  | 4   | ns    |

| Duty Cycle <sup>1</sup>        | d <sub>t5</sub>  | $V_T = 1.5 \text{ V}$                            | 45  | 52   | 55  | %     |

| Jitter, One Sigma <sup>1</sup> | tj1s5            | $V_T = 1.5 \text{ V}$                            |     | 1    | 3   | %     |

| Jitter, Absolute <sup>1</sup>  | tjabs5           | $V_T = 1.5 \text{ V}$                            |     | 3    | 5   | %     |

<sup>&</sup>lt;sup>1</sup>Guaranteed by design, not 100% tested in production.

#### **Electrical Characteristics - REF**

$T_A = 0 - 70C$ ;  $V_{DD} = V_{DDL} = 3.3 \text{ V} + /-5\%$ ;  $C_L = 20 \text{ pF}$  (unless otherwise stated)

| PARAMETER                      | SYMBOL            | CONDITIONS                                       | MIN | TYP  | MAX | UNITS |

|--------------------------------|-------------------|--------------------------------------------------|-----|------|-----|-------|

| Output High Voltage            | V <sub>OH5</sub>  | $I_{OH} = -12 \text{ mA}$                        | 2.6 | 3.1  |     | V     |

| Output Low Voltage             | V <sub>OL5</sub>  | $I_{OL} = 9 \text{ mA}$                          |     | 0.17 | 0.4 | V     |

| Output High Current            | I <sub>OH5</sub>  | $V_{OH} = 2.0 \text{ V}$                         |     | -44  | -22 | mA    |

| Output Low Current             | I <sub>OL5</sub>  | $V_{OL} = 0.8 \text{ V}$                         | 29  | 42   |     | mA    |

| Rise Time <sup>1</sup>         | $t_{r5}$          | $V_{OL} = 0.4 \text{ V}, V_{OH} = 2.4 \text{ V}$ |     | 1.4  | 2   | ns    |

| Fall Time <sup>1</sup>         | ts                | $V_{OH} = 2.4 \text{ V}, V_{OL} = 0.4 \text{ V}$ |     | 1.1  | 2   | ns    |

| Duty Cycle <sup>1</sup>        | dt5               | $V_{T} = 1.5 \text{ V}$                          | 47  | 54   | 57  | %     |

| Jitter, One Sigma <sup>1</sup> | t <sub>j1s5</sub> | $V_T = 1.5 \text{ V}$                            |     | 1    | 3   | %     |

| Jitter, Absolute <sup>1</sup>  | tjabs5            | $V_T = 1.5 \text{ V}$                            |     | 3    | 5   | %     |

Guaranteed by design, not 100% tested in production.

## **Ordering Information**

#### ICS9148M-47