# CMOS PARALLEL FIFO 64 x 4-BIT AND 64 x 5-BIT

IDT72401 IDT72402 IDT72403 IDT72404

# **FEATURES:**

- First-In/First-Out Dual-Port memory

- 64 x 4 organization (IDT72401/03)

- 64 x 5 organization (IDT72402/04)

- IDT72401/02 pin and functionally compatible with MMI67401/02

- · RAM-based FIFO with low fall-through time

- Low-power consumption

- Active: 175mW (typ.)

- Maximum shift rate 45MHz

- · High data output drive capability

- · Asynchronous and simultaneous read and write

- · Fully expandable by bit width

- · Fully expandable by word depth

- IDT72403/04 have Output Enable pin to enable output data

- High-speed data communications applications

- High-performance CMOS technology

- · Available in CERDIP, plastic DIP and SOIC

- · Military product compliant to MIL-STD-883, Class B

- Standard Military Drawing #5962-86846 and 5962-89523 is listed on this function.

- Industrial temperature range (-40°C to +85°C) is available, tested to military electrical specifications

# **DESCRIPTION:**

The IDT72401 and IDT72403 are asynchronous high-performance First-In/First-Out memories organized 64 words by 4 bits. The IDT72402 and IDT72404 are asynchronous high-performance First-In/First-Out memories organized as 64 words by 5 bits. The IDT72403 and IDT72404 also have an

Output Enable  $(\overline{OE})$  pin. The FIFOs accept 4-bit or 5-bit data at the data input (D<sub>0-D3</sub>, 4). The stored data stack up on a first-in/first-out basis.

A Shift Out (SO) signal causes the data at the next to last word to be shifted to the output while all other data shifts down one location in the stack. The Input Ready (IR) signal acts like a flag to indicate when the input is ready for new data (IR = HIGH) or to signal when the FIFO is full (IR = LOW). The Input Ready signal can also be used to cascade multiple devices together. The Output Ready (OR) signal is a flag to indicate that the output remains valid data (OR = HIGH) or to indicate that the FIFO is empty (OR = LOW). The Output Ready can also be used to cascade multiple devices together.

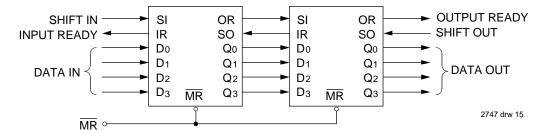

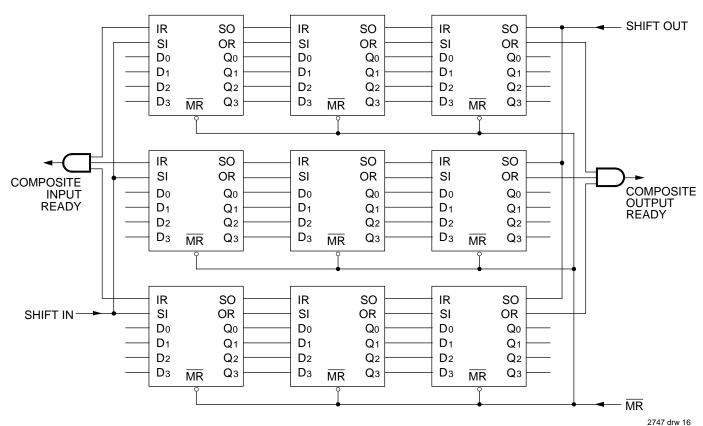

Width expansion is accomplished by logically ANDing the Input Ready (IR) and Output Ready (OR) signals to form composite signals.

Depth expansion is accomplished by tying the data inputs of one device to the data outputs of the previous device. The Input Ready pin of the receiving device is connected to the Shift Out pin of the sending device and the Output Ready pin of the sending device is connected to the Shift In pin of the receiving device.

Reading and writing operations are completely asynchronous allowing the FIFO to be used as a buffer between two digital machines of widely varying operating frequencies. The 45MHz speed makes these FIFOs ideal for high-speed communication and controller applications.

Military grade product is manufactured in compliance with the latest revision of MIL-STD-883, Class B.

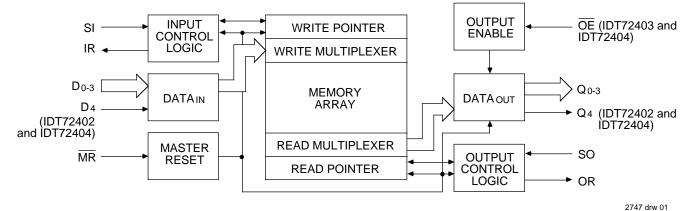

# **FUNCTIONAL BLOCK DIAGRAM**

The IDT logo is a registered trademark of Integrated Device Technology, Inc. FAST is a trademark of National Semiconductor. Inc.

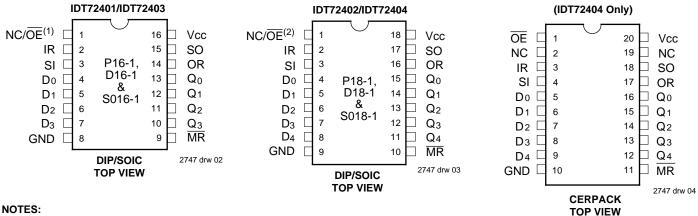

# **PIN CONFIGURATIONS**

1. Pin 1: NC - No Connection IDT72401, OE - IDT72403 2. Pin 1: NC - No Connection IDT72402, OE - IDT72404

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                               | Commercial   | Military     | Unit |

|--------|--------------------------------------|--------------|--------------|------|

| VTERM  | Terminal Voltage with Respect to GND | -0.5 to +7.0 | -0.5 to +7.0 | V    |

| ТА     | Operating Temp.                      | 0 to +70     | -55 to +125  | °C   |

| TBIAS  | Temperature<br>Under Bias            | -55 to +125  | -65 to +135  | °C   |

| Tstg   | Storage Temp.                        | -55 to +125  | -65 to +150  | °C   |

| Іоит   | DC Output<br>Current                 | 50           | 50           | mA   |

#### NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# RECOMMENDED OPERATING CONDITIONS

| Symbol             | Parameter             | Min. | Тур. | Max. | Unit |

|--------------------|-----------------------|------|------|------|------|

| Vcc                | Mil. Supply Voltage   | 4.5  | 5.0  | 5.5  | V    |

| Vcc                | Com'l. Supply Voltage | 4.5  | 5.0  | 5.5  | V    |

| GND                | Supply Voltage        | 0    | 0    | 0    | V    |

| ViH                | Input High Voltage    | 2.0  | _    | _    | V    |

| VIL <sup>(1)</sup> | Input High Voltage    |      |      | 0.8  | V    |

2747 tbl 02

# CAPACITANCE (TA = +25°C, f = 1.0MHz)

1. 1.5V undershoots are allowed for 10ns once per cycle.

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| CIN    | Input Capacitance        | VIN = 0V   | 5    | pF   |

| Соит   | Output Capacitance       | Vout = 0V  | 7    | pF   |

NOTE:

2747 tbl 03

# DC ELECTRICAL CHARACTERISTICS

(Commercial:  $Vcc = 5.0V \pm 10\%$ , TA = 0°C to +70°C; Military:  $Vcc = 5.0V \pm 10\%$ , TA = -55°C to +125°C)

| Symbol               | Parameter                    | Test Conditions                                | Min. | Max. | Unit |

|----------------------|------------------------------|------------------------------------------------|------|------|------|

| lıL                  | Low-Level Input Current      | Vcc = Max., GND ≤ Vı ≤ Vcc                     | -10  | _    | μΑ   |

| lін                  | High-Level Input Current     | Level Input Current Vcc = Max., GND ≤ Vi ≤ Vcc |      | 10   | μΑ   |

| Vol                  | Low-Level Output Voltage     | Vcc = Min., IoL = 8mA                          | _    | 0.4  | V    |

| Vон                  | High-Level Output Voltage    | VCC = Min., IOH = -4mA                         | 2.4  | _    | V    |

| los <sup>(1)</sup>   | Output Short-Circuit Current | Vcc = Max., Vo = GND                           | -20  | -110 | mA   |

| lHZ                  | Off-State Output Current     | Vcc = Max., Vo = 2.4V                          | _    | 20   | μΑ   |

| lLZ                  | (IDT72403 and IDT72404)      | Vcc = Max., Vo = 0.4V                          | -20  | _    | μΑ   |

| Icc <sup>(2,3)</sup> | Supply Current               | Vcc = Max., f = 10MHz Com'l.                   | _    | 35   | mA   |

|                      |                              | Military                                       | _    | 45   | mA   |

NOTES:

2747 tbl 04

- 1. Not more than one output should be shorted at a time and duration of the short-circuit should not exceed one second. Guaranteed but not tested.

- 2. Icc measurements are made with outputs open. OE is HIGH for IDT72403/72404.

- For frequencies greater than 10MHZ, Icc = 35mA + (1.5mA x [f 10MHz]) commercial, and Icc = 45mA + (1.5mA x [f 10MHz]) military.

2 5.01

<sup>1.</sup> This parameter is sampled and not 100% tested.

# **OPERATING CONDITIONS**

(Commercial:  $Vcc = 5.0V \pm 10\%$ , TA = 0°C to +70°C; Military:  $Vcc = 5.0V \pm 10\%$ , TA = -55°C to +125°C)

|                     |                          |        |                                                          |      |                                                                                                          |                         |                            |      |                                                          |      | •    |      |      |

|---------------------|--------------------------|--------|----------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|------|----------------------------------------------------------|------|------|------|------|

|                     |                          |        | Commercial                                               |      |                                                                                                          | Military and Commercial |                            |      |                                                          |      |      |      |      |

|                     |                          |        | IDT72401L45<br>IDT72402L45<br>IDT72403L45<br>IDT72404L45 |      | IDT72401L35 IDT72401L25<br>IDT72402L35 IDT72402L25<br>IDT72403L35 IDT72403L25<br>IDT72404L35 IDT72404L25 |                         | IDT72402L15<br>IDT72403L15 |      | IDT72401L10<br>IDT72402L10<br>IDT72403L10<br>IDT72404L10 |      |      |      |      |

| Symbol              | Parameters               | Figure | Min.                                                     | Max. | Min.                                                                                                     | Max.                    | Min.                       | Max. | Min.                                                     | Max. | Min. | Max. | Unit |

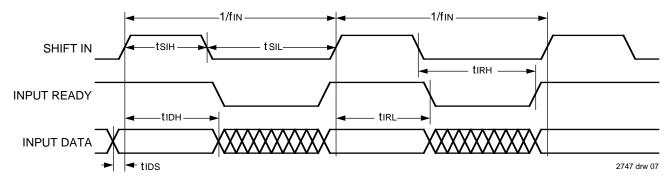

| tsıн <sup>(1)</sup> | Shift in HIGH Time       | 2      | 9                                                        | _    | 9                                                                                                        |                         | 11                         | _    | 11                                                       | _    | 11   | _    | ns   |

| tsıL                | Shift in LOW TIme        | 2      | 11                                                       | _    | 17                                                                                                       | _                       | 24                         | _    | 25                                                       | _    | 30   | _    | ns   |

| tids                | Input Data Set-up        | 2      | 0                                                        | _    | 0                                                                                                        | _                       | 0                          | _    | 0                                                        | _    | 0    | _    | ns   |

| tidh                | Input Data Hold Time     | 2      | 13                                                       | _    | 15                                                                                                       | _                       | 20                         | _    | 30                                                       | _    | 40   | _    | ns   |

| tson <sup>(1)</sup> | Shift Out HIGH Time      | 5      | 9                                                        | _    | 9                                                                                                        | _                       | 11                         | _    | 11                                                       | _    | 11   | _    | ns   |

| tsol                | Shift Out LOW Time       | 5      | 11                                                       | _    | 17                                                                                                       | _                       | 24                         |      | 25                                                       | _    | 25   | _    | ns   |

| tmrw                | Master Reset Pulse       | 8      | 20                                                       | _    | 25                                                                                                       | _                       | 25                         | _    | 25                                                       | _    | 30   | _    | ns   |

| tmrs                | Master Reset Pulse to SI | 8      | 10                                                       | _    | 10                                                                                                       | _                       | 10                         | _    | 25                                                       | _    | 35   | _    | ns   |

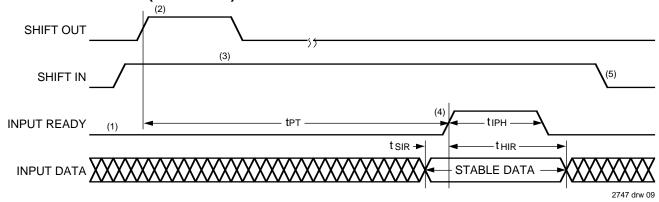

| tsir                | Data Set-up to IR        | 4      | 3                                                        | _    | 3                                                                                                        | _                       | 5                          | _    | 5                                                        |      | 5    |      | ns   |

| thir                | Data Hold from IR        | 4      | 13                                                       | _    | 15                                                                                                       | _                       | 20                         | _    | 30                                                       | _    | 30   | _    | ns   |

| tsor <sup>(4)</sup> | Data Set-up to OR HIGH   | 7      | 0                                                        | _    | 0                                                                                                        | _                       | 0                          | _    | 0                                                        | _    | 0    | _    | ns   |

2747 tbl 05

# **AC ELECTRICAL CHARACTERISTICS**

(Commercial:  $VCC = 5.0V \pm 10\%$ ,  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ; Military:  $VCC = 5.0V \pm 10\%$ ,  $TA = -55^{\circ}C$  to  $+125^{\circ}C$ )

|                        | Commercial                        |        | nercial | Military and Commercial              |       |                                      |       |                                      |                |                                      |       |                                      |      |

|------------------------|-----------------------------------|--------|---------|--------------------------------------|-------|--------------------------------------|-------|--------------------------------------|----------------|--------------------------------------|-------|--------------------------------------|------|

|                        |                                   |        | IDT72   | 401L45<br>402L45<br>403L45<br>404L45 | IDT72 | 401L35<br>402L35<br>403L35<br>404L35 | IDT72 | 401L25<br>402L25<br>403L25<br>404L25 | IDT72<br>IDT72 | 401L15<br>402L15<br>403L15<br>404L15 | IDT72 | 401L10<br>402L10<br>403L10<br>404L10 |      |

| Symbol                 | Parameters                        | Flgure | Min.    | Max.                                 | Min.  | Max.                                 | Min.  | Max.                                 | Min.           | Max.                                 | Min.  | Max.                                 | Unit |

| tın                    | Shift In Rate                     | 2      | _       | 45                                   | _     | 35                                   | _     | 25                                   | _              | 15                                   | _     | 10                                   | MHz  |

| tirl <sup>(1)</sup>    | Shift In to Input Ready LOW       | 2      | _       | 18                                   | _     | 18                                   | _     | 21                                   | _              | 35                                   | _     | 40                                   | ns   |

| tirh <sup>(1)</sup>    | Shift In to Input Ready HIGH      | 2      | _       | 18                                   | l     | 20                                   | _     | 28                                   | _              | 40                                   | _     | 45                                   | ns   |

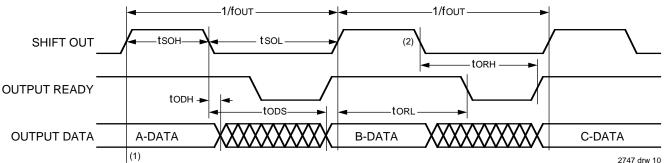

| tout                   | Shift Out Rate                    | 5      | _       | 45                                   | 1     | 35                                   | _     | 25                                   | _              | 15                                   | _     | 10                                   | MHz  |

| torl <sup>(1)</sup>    | Shift Out to Output Ready LOW     | 5      | _       | 18                                   | _     | 18                                   | _     | 19                                   | _              | 35                                   | _     | 40                                   | ns   |

| torh <sup>(1)</sup>    | Shift Out to Output Ready HIGH    | 5      | _       | 19                                   |       | 20                                   | _     | 34                                   | _              | 40                                   | _     | 55                                   | ns   |

| todh                   | Output Data Hold (Previous Word)  | 5      | 5       | _                                    | 5     | _                                    | 5     | _                                    | 5              | _                                    | 5     | _                                    | ns   |

| tods                   | Output Data Shift (Next Word)     | 5      | _       | 19                                   | _     | 20                                   | _     | 34                                   | _              | 40                                   | _     | 55                                   | ns   |

| tpT                    | Data Throughput or "Fall-Through" | 4, 7   | _       | 30                                   | ı     | 34                                   | _     | 40                                   | _              | 65                                   | _     | 65                                   | ns   |

| tmrorl                 | Master Reset to OR LOW            | 8      | _       | 25                                   |       | 28                                   | _     | 35                                   | _              | 35                                   | _     | 40                                   | ns   |

| tmrirh                 | Master Reset to IR HIGH           | 8      | _       | 25                                   | 1     | 28                                   | _     | 35                                   | _              | 35                                   | _     | 40                                   | ns   |

| tmrQ                   | Master Reset to Data Output LOW   | 8      | _       | 20                                   | _     | 20                                   | _     | 25                                   | _              | 35                                   | _     | 40                                   | ns   |

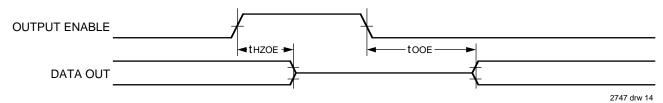

| t00E <sup>(3)</sup>    | Output Valid from <u>OE</u> LOW   | 9      | _       | 12                                   |       | 15                                   | _     | 20                                   | _              | 30                                   | _     | 35                                   | ns   |

| tHZOE <sup>(3,4)</sup> | Output High-Z from OE HIGH        | 9      | _       | 12                                   |       | 12                                   | _     | 15                                   | _              | 25                                   | _     | 30                                   | ns   |

| tiPH <sup>(2,4)</sup>  | Input Ready Pulse HIGH            | 4      | 9       | _                                    | 9     | _                                    | 11    | _                                    | 11             | _                                    | 11    | _                                    | ns   |

| toph <sup>(2,4)</sup>  | Ouput Ready Pulse HIGH            | 7      | 9       | _                                    | 9     | _                                    | 11    | _                                    | 11             | _                                    | 11    | _                                    | ns   |

### NOTES:

2747 tbl 06

<sup>1.</sup> Since the FIFO is a very high-speed device, care must be excercised in the design of the hardware and timing utilized within the design. Device grounding and decoupling are crucial to correct operation as the FIFO will respond to very small glitches due to long reflective lines, high capacitances and/or poor supply decoupling and grounding. A monolithic ceramic capacitor of 0.1μF directly between Vcc and GND with very short lead length is recommended.

<sup>2.</sup> This parameter applies to FIFOs communicating with each other in a cascaded mode. IDT FIFOs are guaranteed to cascade with other IDT FIFOs of like speed grades.

<sup>3.</sup> IDT72403 and IDT72404 only.

<sup>4.</sup> Guaranteed by design but not currently tested.

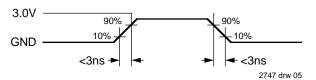

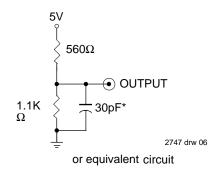

# **AC TEST CONDITIONS**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise/Fall Times         | 3ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 1 |

2747 tbl 07

#### **ALL INPUT PULSES:**

Figure 1. AC Test Load

\*Including scope and jig

# SIGNAL DESCRIPTIONS

### **INPUTS:**

# DATA INPUT (D0-3, 4)

Data input lines. The IDT72401 and IDT72403 have a 4-bit data input. The IDT72402 and IDT72404 have a 5-bit data input.

# **CONTROLS:**

### SHIFT IN (SI)

Shift In controls the input of the data into the FIFO. When SI is HIGH, data can be written to the FIFO via the Do-3,4 lines.

# SHIFT OUT (SO)

Shift Out controls the output of data of the FIFO. When SO is HIGH, data can be read from the FIFO via the Data Output (Q0-3, 4) lines.

# MASTER RESET (MR)

Master Reset clears the FIFO of any data stored within. Upon power up, the FIFO should be cleared with a Master Reset. Master Reset is active LOW.

### **INPUT READY (IR)**

When Input Ready is HIGH, the FIFO is ready for new input data to be written to it. When IR is LOW the FIFO is unavailable for new input data. Input Ready is also used to cascade many FIFOs together, as shown in Figures 10 and 11 in the Applications section.

### **OUTPUT READY (OR)**

When Output Ready is HIGH, the output (Q0-3, 4) contains valid data. When OR is LOW, the FIFO is unavailable for new output data. Output Ready is also used to cascade many FIFOs together, as shown in Figures 10 and 11.

# OUTPUT ENABLE (OE) (IDT72403 AND IDT72404 ONLY)

Output enable is used to read FIFO data onto a bus. Output Enable is active LOW.

# **OUTPUTS:**

# DATA OUTPUT (Q0-3, 4)

Data Output lines. The IDT72401 and IDT72403 have a 4-bit data output. The IDT72402 and IDT72404 have a 5-bit data output.

### **FUNCTIONAL DESCRIPTION**

These 64 x 4 and 64 x 5 FIFOs are designed using a dual port RAM architecture as opposed to the traditional shift register approach. This FIFO architecture has a write pointer, a read pointer and control logic, which allow simultaneous read and write operations. The write pointer is incremented by the falling edge of the Shift In (SI) control; the read pointer is incremented by the falling edge of the Shift Out (SO). The Input Ready (IR) signals when the FIFO has an available memory location; Output Ready (OR) signals when there is valid data on the output. Output Enable ( $\underline{OE}$ ) provides the capability of three-stating the FIFO outputs.

### **FIFO Reset**

The FIFO must be reset upon power up using the Master Reset (MR) signal. This causes the FIFO to enter an empty state, signified by Output Ready (OR) being LOW and Input Ready (IR) being HIGH. In this state, the data outputs (Q0-3, 4) will be LOW.

#### **Data Input**

Data is shifted in on the LOW-to-HIGH transition of Shift In (SI). This loads input data into the first word location of the FIFO and causes Input Ready to go LOW. On the HIGH-to-LOW transition of Shift In, the write pointer is moved to the next word position and Input Ready (IR) goes HIGH, indicating the readiness to accept new data. If the FIFO is full, Input Ready will remain LOW until a word of data is shifted out.

### **Data Output**

Data is shifted out on the HIGH-to-LOW transition of Shift Out (SO). This causes the internal read pointer to be advanced to the next word location. If data is present, valid data will appear on the outputs and Output Ready (OR) will go HIGH. If data is not present, Output Ready will stay LOW indicating the FIFO is empty. The last valid word read from the FIFO will remain at the FIFOs output when it is empty. When the FIFO is not empty, Output Ready (OR) goes LOW on the LOW-to-HIGH transition of Shift Out. Previous data remains on the output until the HIGH-to-LOW transition of Shift Out (SO).

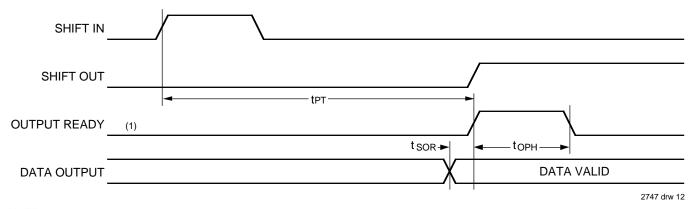

### **Fall-Through Mode**

The FIFO operates in a fall-through mode when data gets shifted into an empty FIFO. After a fall-through delay the data propagates to the output. When the data reaches the output, the Output Ready (OR) goes HIGH. Fall-through mode also occurs when the FIFO is completely full. When data is shifted out of the full FIFO, a location is available for new data. After a fall-through delay, the Input Ready goes HIGH. If Shift In is HIGH, the new data can be written to the FIFO.

Since these FIFOs are based on an internal dual-port RAM architecture with separate read and write pointers, the fall-through time (tPT) is one cycle long. A word may be written into the FIFO on a clock cycle and can be accessed on the next clock cycle.

## **TIMING DIAGRAMS**

Figure 2. Input Timing

# NOTES:

- 1. Input Ready HIGH indicates space is available and a Shift In pulse may be applied.

- 2. Input Data is loaded into the first word.

- 3. Input Ready goes LOW indicating the first word is full.

- 4. The write pointer is incremented.

- 5. The FIFO is ready for the next word.

- 6. If the FIFO is full then the Input Ready remains LOW.

- 7. Shift In pulses applied while Input Ready is LOW will be ignored (see Figure 4).

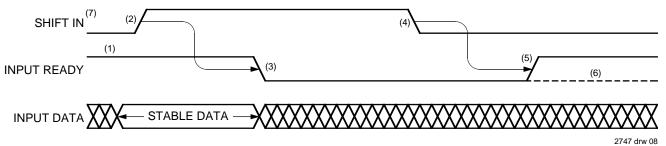

Figure 3. The Mechanism of Shifting Data Into the FIFO

# **TIMING DIAGRAMS (Continued)**

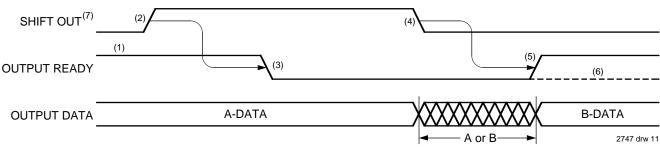

### NOTES:

- 1. FIFO is initially full.

- 2. Shift Out pulse is applied.

- 3. Shift In is held HIGH.

- 4. As soon as Input Ready becomes HIGH the Input Data is loaded into the FIFO.

- 5. The write pointer is incremented. Shift In should not go LOW until (tpt + tiph).

Figure 4. Data is Shifted In Whenever Shift In and Input Ready are Both HIGH

# NOTES:

- 1. This data is loaded consecutively A, B, C.

- 2. Data is shifted out when Shift Out makes a HIGH to LOW transition.

Figure 5. Output TIming

#### NOTES:

- 1. Output Ready HIGH indicates that data is available and a Shift Out pulse may be applied.

- 2. Shift Out goes HIGH causing the next step.

- 3. Output Ready goes LOW.

- 4. The read pointer is incremented.

- 5. Output Ready goes HIGH indicating that new data (B) is now available at the FIFO outputs.

- 6. If the FIFO has only one word loaded (A DATA) then Output Ready stays LOW and the A DATA remains unchanged at the outputs.

- 7. Shift Out pulses applied when Output Ready is LOW will be ignored.

Figure 6. The Mechanism of Shifting Data Out of the FIFO

# **TIMING DIAGRAMS (Continued)**

# NOTE:

1. FIFO initially empty.

Figure 7. tpt and toph Specification

MASTER RESET

INPUT READY

(1)

(1)

(1)

(1)

TMRORL

TMRORL

TMRORL

2747 dnw 13

NOTE:

1. Worst case, FIFO initially full..

Figure 8. Master Reset Timing

NOTE:

1. High-Z transitions are referenced to the steady-state VoH -500mV and VoL +500mV levels on the output. thzoE is tested with 5pF load capacitance instead of 30pF as shown in Figure 1.

Figure 9. Output Enable Timing, IDT72403 and IDT72404 Only

# **APPLICATIONS**

#### NOTE:

1. FIFOs can be easily cascaded to any desired path. The handshaking and associated timing between the FIFOs are handled by the inherent timing of the devices.

Figure 10. 128 x 4 Depth Expansion

#### NOTES:

- 1. When the memory is empty, the last word will remain on the outputs until the Master Reset is strobed or a new data word falls through to the output. However, OR will remain LOW, indicating data at the output is not valid.

- 2. When the output data changes as a result of a pulse on SO, the OR signal always goes LOW before there is any change in output data and stays LOW until the new data has appeared on the outputs. Anytime OR is HIGH, there is valid stable data on the outputs.

- 3. If SO is held HIGH while the memory is empty and a word is written into the input, that word will appear at the output after a fall-through time. OR will go HIGH for one internal cycle (at least torl) and then go back LOW again. The stored word will remain on the outputs. If more words are written into the FIFO, they will line up behind the first word and will not appear on the outputs until SO has been brought LOW.

- 4. When the Master Reset is brought Low, the outputs are cleared to LOW, IR goes HIGH and OR goes LOW. If SI is HIGH when the Master Reset goes HIGH, the data on the inputs will be written into the memory and IR will return to the LOW state until SI is brought LOW. If SI is LOW when the Master Reset is ended. IR will go HIGH, but the data in the inputs will not enter the memory until SI goes HIGH.

- 5. FIFOs are expandable on depth and width. However, in forming wider words, two external gates are required to generate composite Input and Output Ready flags. This is due to the variation of delays of the FIFOs.

Figure 11. 192 x 12 Depth and Width Expansion

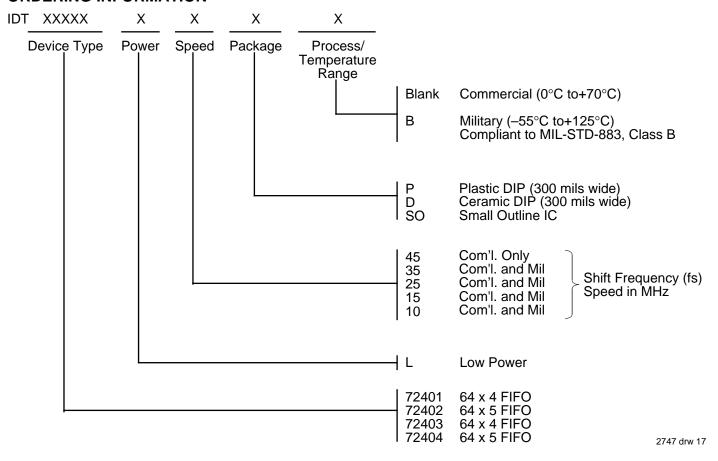

# **ORDERING INFORMATION**