# M16C/30P Group

## Hardware Manual

### RENESAS 16-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY / M16C/30 SERIES

Before using this material, please visit our website to verify that this is the most updated document available.

Rev.1.22 Revision Date:Mar 29, 2007

RenesasTechnology www.renesas.com

Hardware Manue

16

#### Notes regarding these materials

- This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of Renesas or any third party with respect to the information in this document.

- Renesas shall have no liability for damages or infringement of any intellectual property or other rights arising out of the use of any information in this document, including, but not limited to, product data, diagrams, charts, programs, algorithms, and application circuit examples.

You should not use the products or the technology described in this document for the purpose of military

- 3. You should not use the products or the technology described in this document for the purpose of military applications such as the development of weapons of mass destruction or for the purpose of any other military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations.

- 4. All information included in this document such as product data, diagrams, charts, programs, algorithms, and application circuit examples, is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas products listed in this document, please confirm the latest product information with a Renesas sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas such as that disclosed through our website. (http://www.renesas.com)

- 5. Renesas has used reasonable care in compiling the information included in this document, but Renesas assumes no liability whatsoever for any damages incurred as a result of errors or omissions in the information included in this document.

- 6. When using or otherwise relying on the information in this document, you should evaluate the information in light of the total system before deciding about the applicability of such information to the intended application. Renesas makes no representations, warranties or guaranties regarding the suitability of its products for any particular application and specifically disclaims any liability arising out of the application and use of the information in this document or Renesas products.

- 7. With the exception of products specified by Renesas as suitable for automobile applications, Renesas products are not designed, manufactured or tested for applications or otherwise in systems the failure or malfunction of which may cause a direct threat to human life or create a risk of human injury or which require especially high quality and reliability such as safety systems, or equipment or systems for transportation and traffic, healthcare, combustion control, aerospace and aeronautics, nuclear power, or undersea communication transmission. If you are considering the use of our products for such purposes, please contact a Renesas sales office beforehand. Renesas shall have no liability for damages arising out of the uses set forth above.

- 8. Notwithstanding the preceding paragraph, you should not use Renesas products for the purposes listed below: (1) artificial life support devices or systems

- (2) surgical implantations

- (3) healthcare intervention (e.g., excision, administration of medication, etc.)

- (4) any other purposes that pose a direct threat to human life

Renesas shall have no liability for damages arising out of the uses set forth in the above and purchasers who elect to use Renesas products in any of the foregoing applications shall indemnify and hold harmless Renesas Technology Corp., its affiliated companies and their officers, directors, and employees against any and all damages arising out of such applications.

- 9. You should use the products described herein within the range specified by Renesas, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas shall have no liability for malfunctions or damages arising out of the use of Renesas products beyond such specified ranges.

- 10. Although Renesas endeavors to improve the quality and reliability of its products, IC products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Please be sure to implement safety measures to guard against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other applicable measures. Among others, since the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 11. In case Renesas products listed in this document are detached from the products to which the Renesas products are attached or affixed, the risk of accident such as swallowing by infants and small children is very high. You should implement safety measures so that Renesas products may not be easily detached from your products. Renesas shall have no liability for damages arising out of such detachment.

- 12. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written approval from Renesas.

- 13. Please contact a Renesas sales office if you have any questions regarding the information contained in this document, Renesas semiconductor products, or if you have any other inquiries.

#### General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this manual, refer to the relevant sections of the manual. If the descriptions under General Precautions in the Handling of MPU/MCU Products and in the body of the manual differ from each other, the description in the body of the manual takes precedence.

#### 1. Handling of Unused Pins

Handle unused pins in accord with the directions given under Handling of Unused Pins in the manual.

- The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

- 2. Processing at Power-on

- The state of the product is undefined at the moment when power is supplied.

- The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed. In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

— When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

#### 5. Differences between Products

Before changing from one product to another, i.e. to one with a different type number, confirm that the change will not lead to problems.

— The characteristics of MPU/MCU in the same group but having different type numbers may differ because of the differences in internal memory capacity and layout pattern. When changing to products of different type numbers, implement a system-evaluation test for each of the products.

## How to Use This Manual

#### 1. Purpose and Target Readers

This manual is designed to provide the user with an understanding of the hardware functions and electrical characteristics of the MCU. It is intended for users designing application systems incorporating the MCU. A basic knowledge of electric circuits, logical circuits, and MCUs is necessary in order to use this manual. The manual comprises an overview of the product; descriptions of the CPU, system control functions, peripheral functions, and electrical characteristics; and usage notes.

Particular attention should be paid to the precautionary notes when using the manual. These notes occur within the body of the text, at the end of each section, and in the Usage Notes section.

The revision history summarizes the locations of revisions and additions. It does not list all revisions. Refer to the text of the manual for details.

The following documents apply to the M16C/30P Group. Make sure to refer to the latest versions of these documents. The newest versions of the documents listed may be obtained from the Renesas Technology Web site.

| Document Type    | Description                                         | Document Title     | Document No.  |

|------------------|-----------------------------------------------------|--------------------|---------------|

| Datasheet        | Hardware overview and electrical characteristics    | M16C/30P Group     | REJ03B0088    |

|                  |                                                     | Datasheet          |               |

| Hardware manual  | Hardware specifications (pin assignments,           | M16C/30P Group     | This hardware |

|                  | memory maps, peripheral function                    | Hardware Manual    | manual        |

|                  | specifications, electrical characteristics, timing  |                    |               |

|                  | charts) and operation description                   |                    |               |

|                  | Note: Refer to the application notes for details on |                    |               |

|                  | using peripheral functions.                         |                    |               |

| Application note | Information on using peripheral functions and       | Available from Ren | esas          |

|                  | application examples                                | Technology Web si  | te.           |

|                  | Sample programs                                     |                    |               |

|                  | Information on writing programs in assembly         |                    |               |

|                  | language and C                                      |                    |               |

| Renesas          | Product specifications, updates on documents,       |                    |               |

| technical update | etc.                                                |                    |               |

### 2. Notation of Numbers and Symbols

The notation conventions for register names, bit names, numbers, and symbols used in this manual are described below.

- (1) Register Names, Bit Names, and Pin Names Registers, bits, and pins are referred to in the text by symbols. The symbol is accompanied by the word "register," "bit," or "pin" to distinguish the three categories. Examples the PM03 bit in the PM0 register P3\_5 pin, VCC pin

- (2) Notation of Numbers

The indication "b" is appended to numeric values given in binary format. However, nothing is appended to the values of single bits. The indication "h" is appended to numeric values given in hexadecimal format. Nothing is appended to numeric values given in decimal format.

Examples Binary: 11b

Hexadecimal: EFA0h Decimal: 1234

### 3. Register Notation

The symbols and terms used in register diagrams are described below.

| XXX Register            | /            | *1                                            |                                                     |    |     |

|-------------------------|--------------|-----------------------------------------------|-----------------------------------------------------|----|-----|

| b7 b6 b5 b4 b3 b2 b1 b0 | Symbo<br>XXX | Address<br>XXX                                | After Reset *5                                      |    |     |

|                         | Bit Symbol   | Bit Name                                      | Function                                            | RW | .*2 |

|                         | XXX0         | XXX Bit                                       | b1 b0<br>1 0: XXX<br>0 1: XXX                       | RW |     |

|                         | XXX1         |                                               | 1 0: Avoid this setting<br>1 1: XXX                 | RW |     |

|                         | (b2)         | Nothing is assigned.<br>When write, should se | et to "0". When read, its content is indeterminate. | _  | *3  |

|                         | (b3)         | Reserved Bit                                  | Must set to "0"                                     | RW | *4  |

|                         | XXX4         | XXX Bit                                       | Function varies depending on each operation mode    | RW |     |

|                         | XXX5         |                                               |                                                     | wo |     |

|                         | XXX6         |                                               |                                                     | RW |     |

| L                       | XXX7         | XXX Bit                                       | 0: XXX<br>1: XXX                                    | RO |     |

\*1

Blank: Set to 0 or 1 according to the application.0: Set to 0.1: Set to 1.

X: Nothing is assigned.

\*2

RW: Read and write. RO: Read only. WO: Write only. -: Nothing is assigned.

\*3

• Reserved bit

Reserved bit. Set to specified value.

\*4

• Nothing is assigned

Nothing is assigned to the bit. As the bit may be used for future functions, if necessary, set to 0.

• Do not set to a value

Operation is not guaranteed when a value is set.

• Function varies according to the operating mode.

The function of the bit varies with the peripheral function mode. Refer to the register diagram for information on the individual modes.

## 4. List of Abbreviations and Acronyms

| Abbreviation | Full Form                                    |

|--------------|----------------------------------------------|

| ACIA         | Asynchronous Communication Interface Adapter |

| bps          | bits per second                              |

| CRC          | Cyclic Redundancy Check                      |

| DMA          | Direct Memory Access                         |

| DMAC         | Direct Memory Access Controller              |

| GSM          | Global System for Mobile Communications      |

| Hi-Z         | High Impedance                               |

| IEBus        | Inter Equipment bus                          |

| I/O          | Input/Output                                 |

| IrDA         | Infrared Data Association                    |

| LSB          | Least Significant Bit                        |

| MSB          | Most Significant Bit                         |

| NC           | Non-Connection                               |

| PLL          | Phase Locked Loop                            |

| PWM          | Pulse Width Modulation                       |

| SFR          | Special Function Registers                   |

| SIM          | Subscriber Identity Module                   |

| UART         | Universal Asynchronous Receiver/Transmitter  |

| VCO          | Voltage Controlled Oscillator                |

All trademarks and registered trademarks are the property of their respective owners. IEBus is a registered trademark of NEC Electronics Corporation.

## Table of Contents

| SFR Pag | e Reference B                                              | - 1 |

|---------|------------------------------------------------------------|-----|

| 1. Ov   | erview                                                     | . 1 |

| 1.1     | Applications                                               | 1   |

| 1.2     | Performance Outline                                        |     |

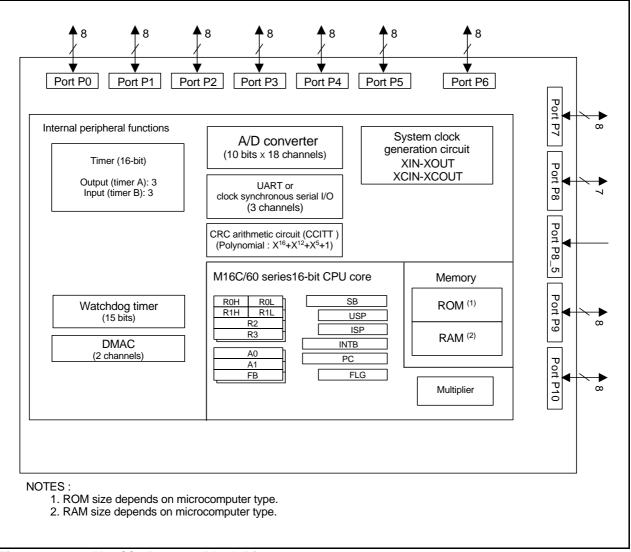

| 1.3     | Block Diagram                                              | 3   |

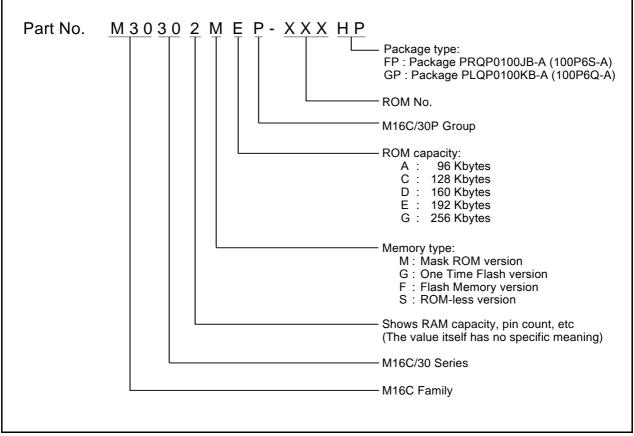

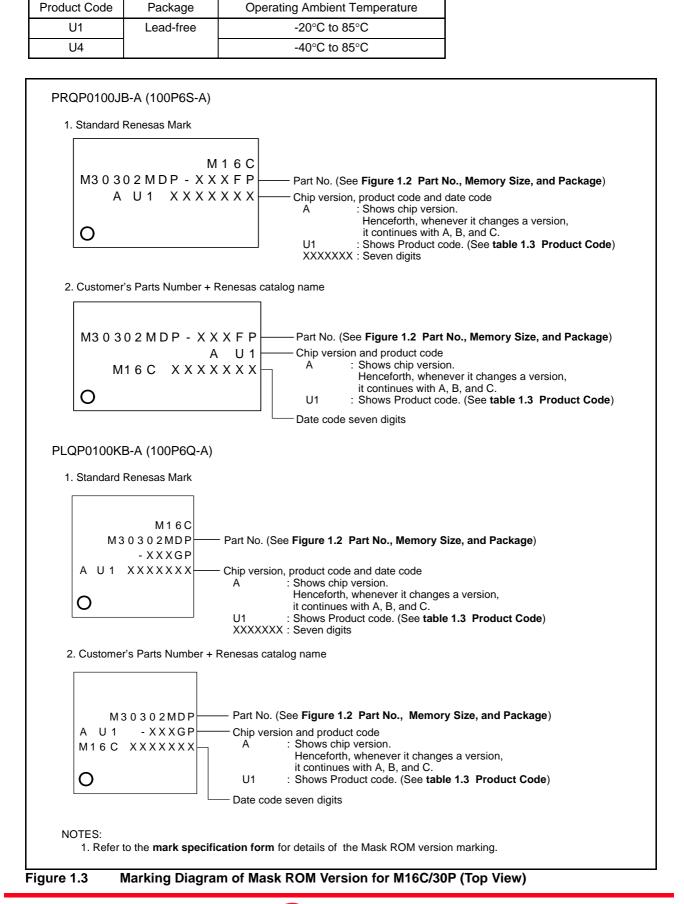

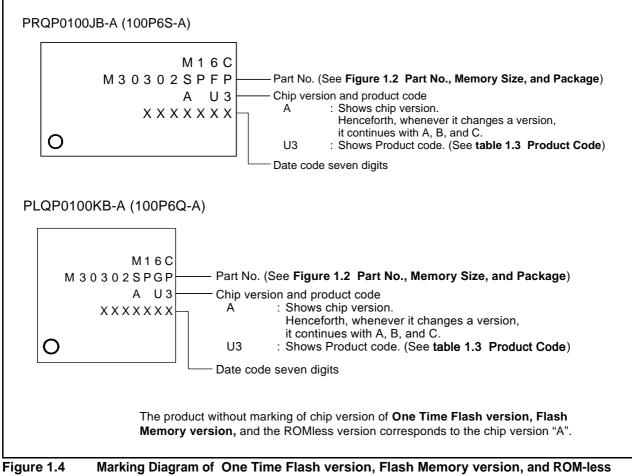

| 1.4     | Product List                                               |     |

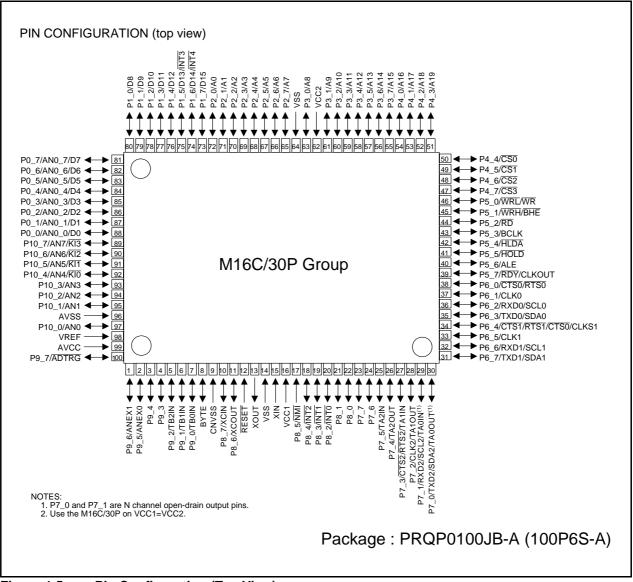

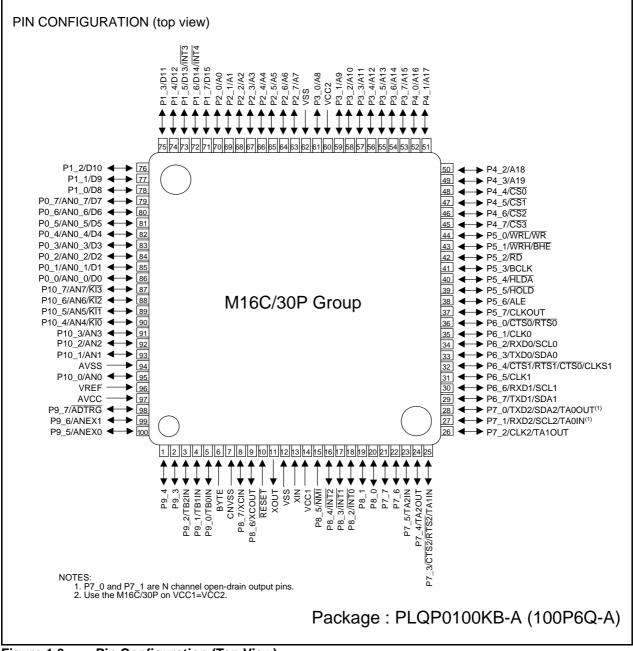

| 1.5     | Pin Configuration                                          |     |

| 1.6     | Pin Description                                            |     |

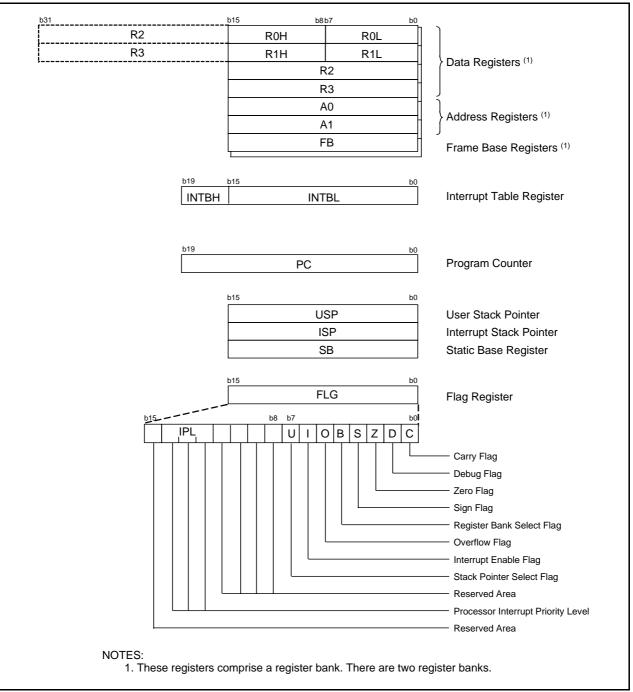

| 2. Ce   | ntral Processing Unit (CPU)                                | 14  |

| 2.1     | Data Registers (R0, R1, R2 and R3)                         |     |

| 2.2     | Address Registers (A0 and A1)                              |     |

| 2.2     | Frame Base Register (FB)                                   |     |

| 2.3     | Interrupt Table Register (INTB)                            |     |

| 2.5     | Program Counter (PC)                                       |     |

| 2.6     | User Stack Pointer (USP) and Interrupt Stack Pointer (ISP) |     |

| 2.0     | Static Base Register (SB)                                  |     |

| 2.8     | Flag Register (FLG)                                        |     |

| 2.8.1   | Carry Flag (C Flag)                                        |     |

| 2.8.2   | Debug Flag (D Flag)                                        |     |

| 2.8.3   | Zero Flag (Z Flag)                                         |     |

| 2.8.4   | Sign Flag (S Flag)                                         |     |

| 2.8.5   | Register Bank Select Flag (B Flag)                         |     |

| 2.8.6   | Overflow Flag (O Flag)                                     |     |

| 2.8.7   | Interrupt Enable Flag (I Flag)                             |     |

| 2.8.8   | Stack Pointer Select Flag (U Flag)                         |     |

| 2.8.9   | Processor Interrupt Priority Level (IPL)                   |     |

| 2.8.10  |                                                            |     |

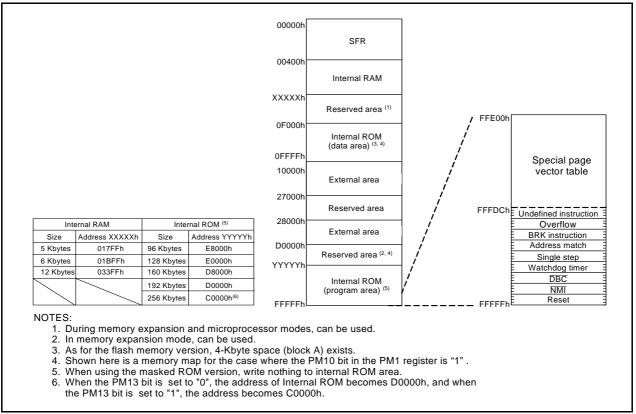

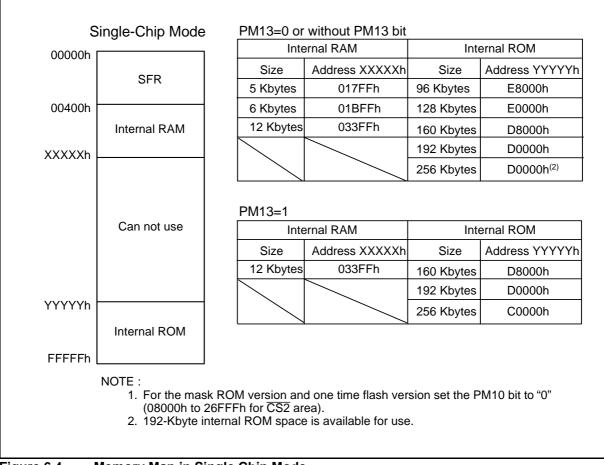

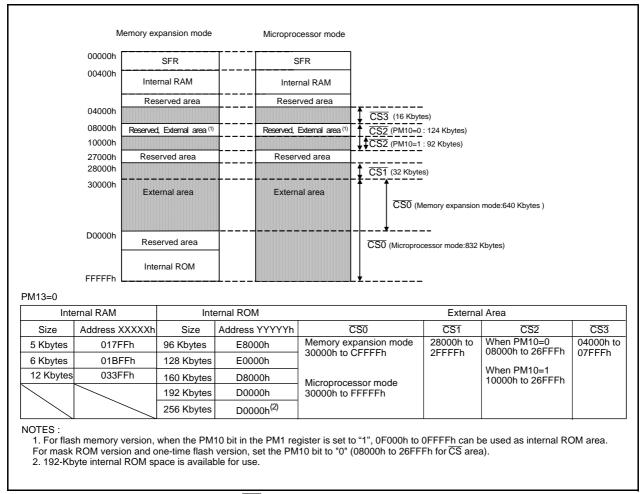

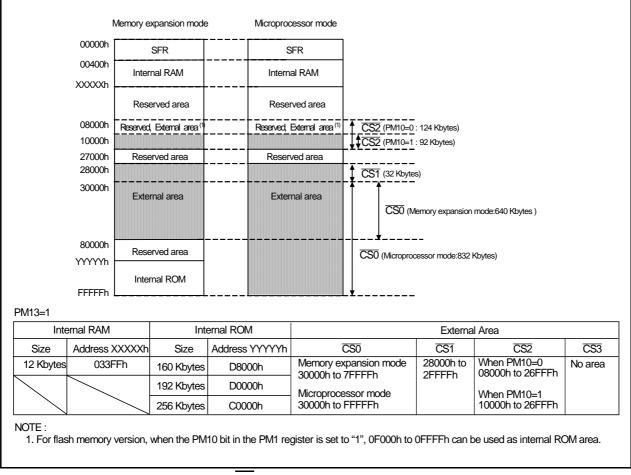

| 3. Me   | mory                                                       | 17  |

|         |                                                            |     |

| 4. Sp   | ecial Function Register (SFR)                              | 18  |

| 5. Re   | set                                                        | 23  |

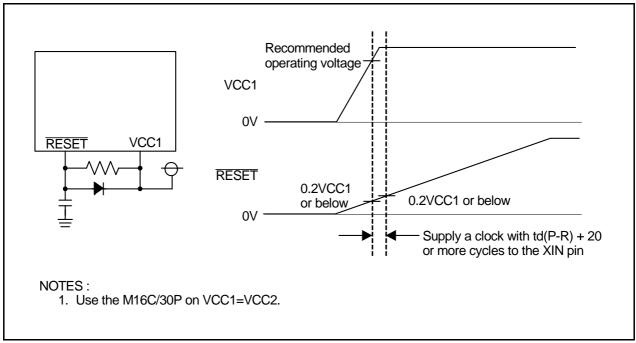

| 5.1     | Hardware Reset                                             | 23  |

| 5.1.1   | Reset on a Stable Supply Voltage                           | 23  |

| 5.1.2   | Power-on Reset                                             | 23  |

| 5.2     | Software Reset                                             | 25  |

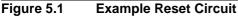

| 5.3     | Internal Space                                             | 26  |

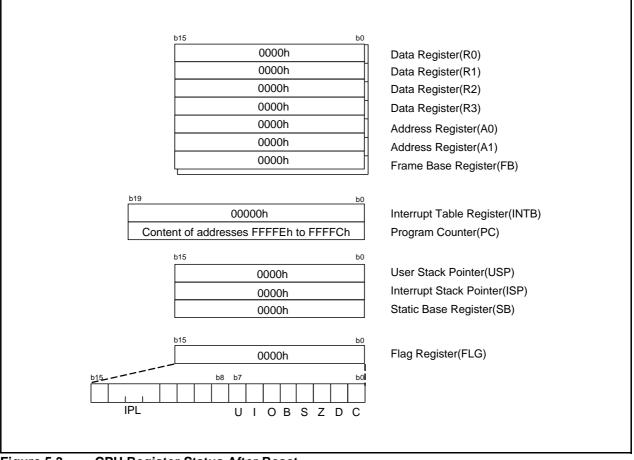

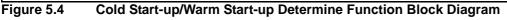

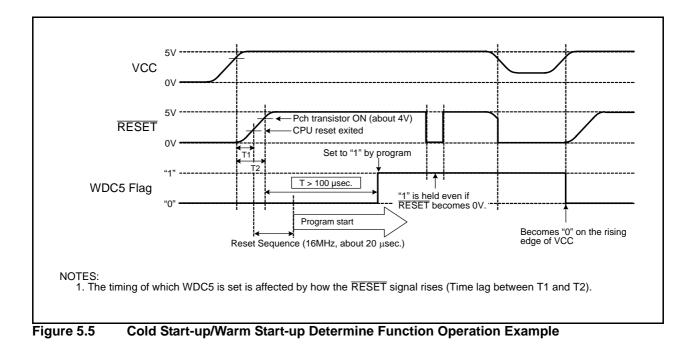

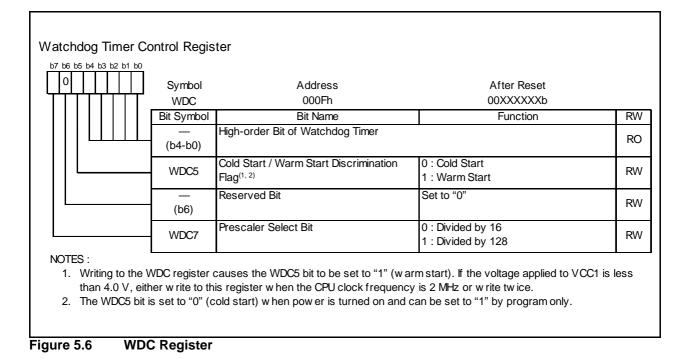

| 5.4     | Cold Start-up / Warm Start-up Determine Function           | 27  |

| 6. Pro  | ocessor Mode                                               | 29  |

| 6.1     | Types of Processor Mode                                    | 29  |

| 6.2     | Setting Processor Modes                                    |     |

| 7. Bu          | S                                                                                                            | 34 |

|----------------|--------------------------------------------------------------------------------------------------------------|----|

| 7.1            | Bus Mode                                                                                                     |    |

| 7.2            | Bus Control                                                                                                  | 34 |

| 7.2.1          | Address Bus                                                                                                  |    |

| 7.2.2          | Data Bus                                                                                                     | 34 |

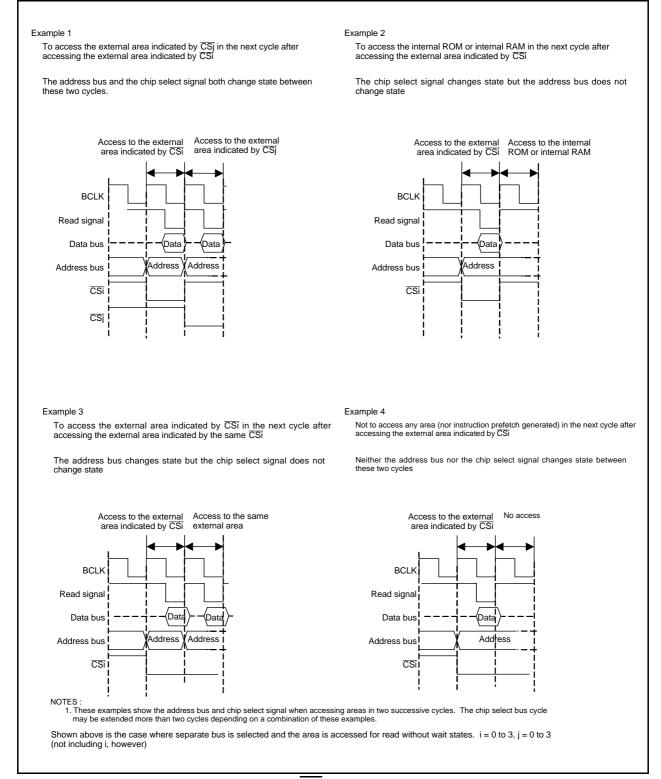

| 7.2.3          | Chip Select Signal                                                                                           | 35 |

| 7.2.4          | Read and Write Signals                                                                                       | 37 |

| 7.2.5          | ALE Signal                                                                                                   | 37 |

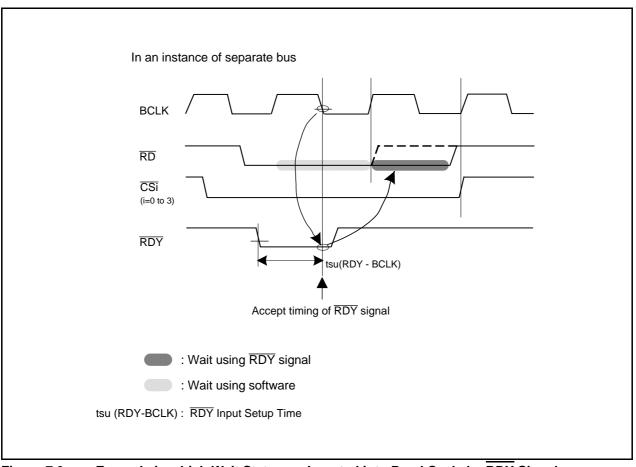

| 7.2.6          | RDY Signal                                                                                                   | 38 |

| 7.2.7          | HOLD Signal                                                                                                  | 39 |

| 7.2.8          | BCLK Output                                                                                                  | 39 |

| 7.2.9          | External Bus Status When Internal Area Accessed                                                              | 41 |

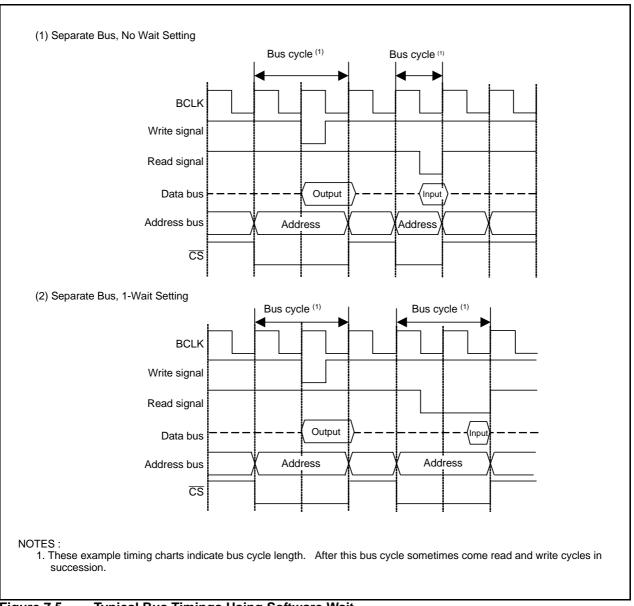

| 7.2.10         | Software Wait                                                                                                | 41 |

|                |                                                                                                              |    |

| 8. Me          | mory Space Expansion Function                                                                                |    |

| 8.1            | 1-Mbyte Mode                                                                                                 | 43 |

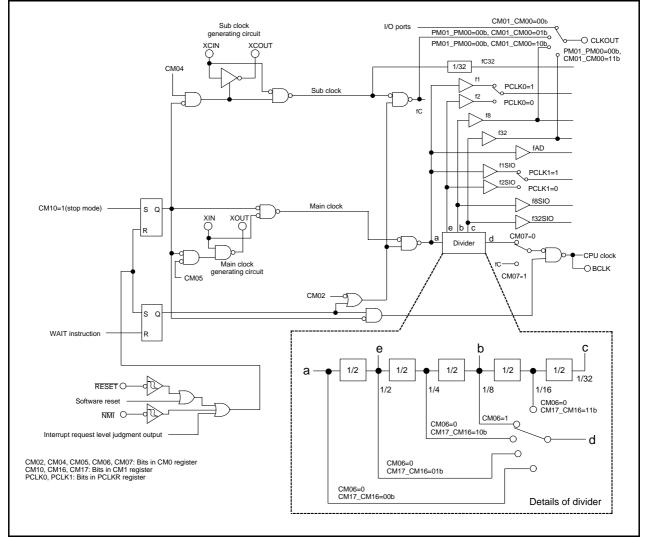

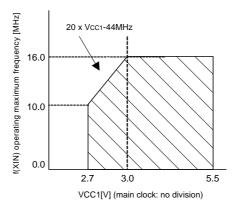

| 9. Clo         | ock Generating Circuit                                                                                       | 15 |

|                | -                                                                                                            |    |

| 9.1<br>9.1.1   | Types of the Clock Generating Circuit<br>Main Clock                                                          |    |

| ,              |                                                                                                              |    |

| 9.1.2          | Sub Clock                                                                                                    |    |

| 9.2            | CPU Clock and Peripheral Function Clock                                                                      |    |

| 9.2.1          | CPU Clock and BCLK                                                                                           |    |

| 9.2.2<br>9.3   | Peripheral Function Clock (f1, f2, f8, f32, f1SIO, f2SIO, f8SIO, f32SIO, fAD, fC32)<br>Clock Output Function |    |

|                |                                                                                                              |    |

| 9.4<br>9.4.1   | Power Control<br>Normal Operation Mode                                                                       |    |

| 9.4.1<br>9.4.2 | Wait Mode                                                                                                    |    |

| 9.4.2<br>9.4.3 | Stop Mode                                                                                                    |    |

| 9.4.5          | Stop Mode                                                                                                    |    |

| 10. Pro        | otection                                                                                                     | 60 |

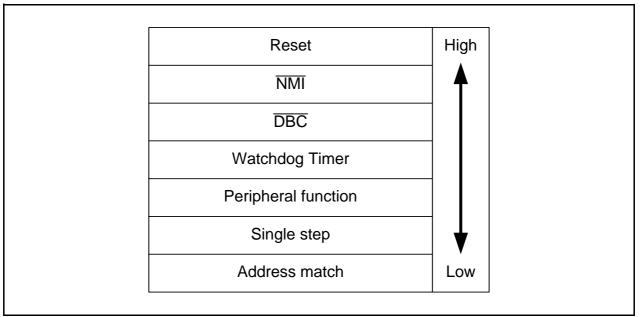

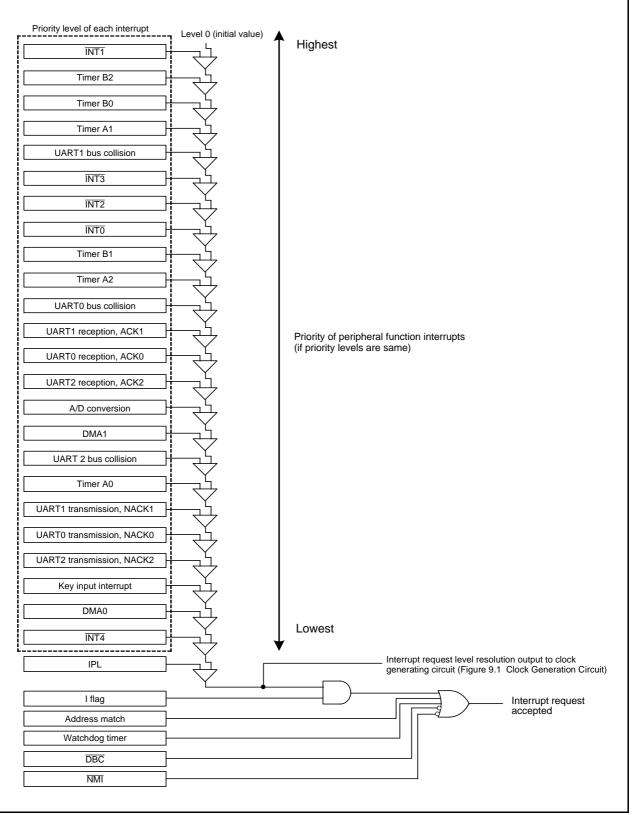

| 11. Inte       | errupt                                                                                                       |    |

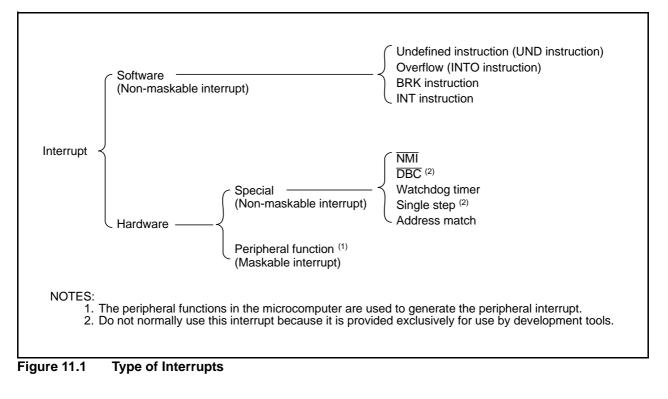

| 11.1           | Type of Interrupts                                                                                           |    |

| 11.2           | Software Interrupts                                                                                          |    |

| 11.2.1         | •                                                                                                            |    |

| 11.2.2         | •                                                                                                            |    |

| 11.2.3         |                                                                                                              |    |

| 11.2.4         |                                                                                                              |    |

| 11.3           | Hardware Interrupts                                                                                          |    |

| 11.3.1         | -                                                                                                            |    |

| 11.3.2         |                                                                                                              |    |

| 11.4           | Interrupts and Interrupt Vector                                                                              |    |

| 11.4.1         |                                                                                                              |    |

| 11.4.2         |                                                                                                              |    |

|                |                                                                                                              |    |

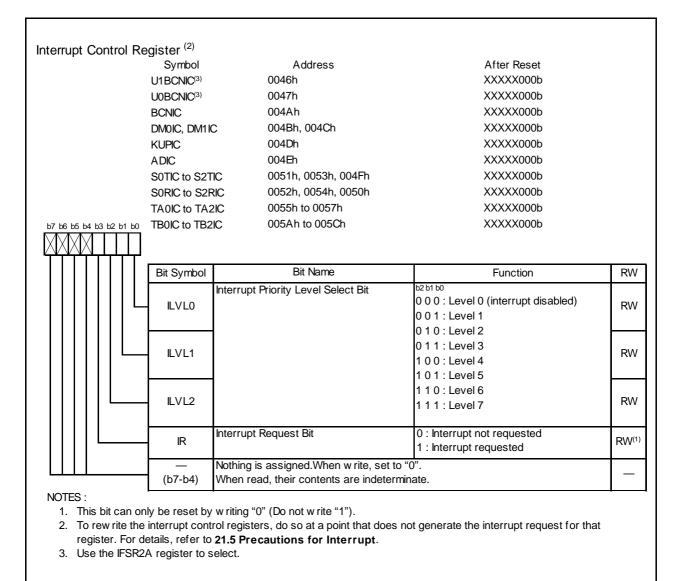

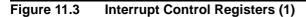

| 11.5 |       | Interrupt Control                                   | . 66  |

|------|-------|-----------------------------------------------------|-------|

| 11.  | .5.1  | I Flag                                              | . 68  |

| 11.  | .5.2  | IR Bit                                              | . 68  |

| 11.  | .5.3  | ILVL2 to ILVL0 Bits and IPL                         | . 68  |

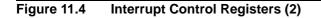

| 11.  | .5.4  | Interrupt Sequence                                  | . 69  |

| 11.  | .5.5  | Interrupt Response Time                             |       |

| 11.  | .5.6  | Variation of IPL when Interrupt Request is Accepted | . 70  |

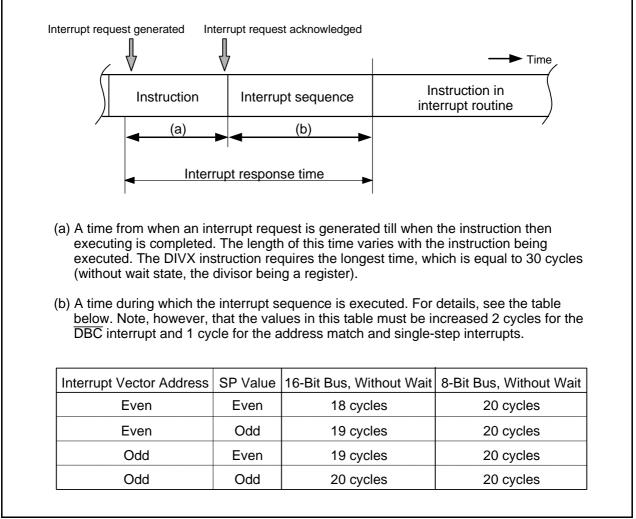

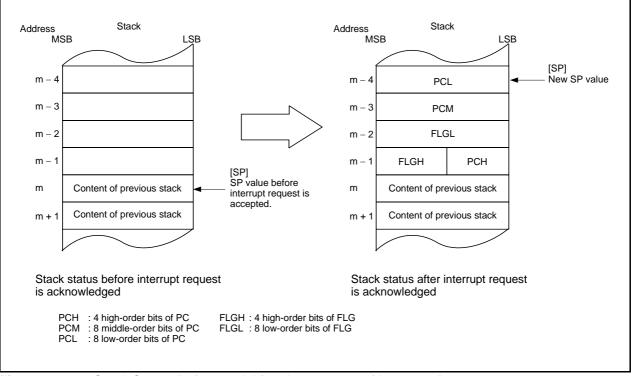

| 11.  | .5.7  | Saving Registers                                    |       |

| 11.  | .5.8  | Returning from an Interrupt Routine                 |       |

| 11.  | .5.9  | Interrupt Priority                                  |       |

| 11.  | .5.10 |                                                     |       |

| 11.6 |       | INT Interrupt                                       |       |

| 11.7 |       | MI Interrupt                                        |       |

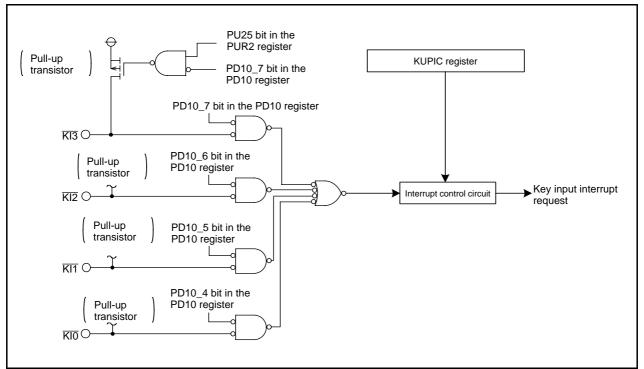

| 11.8 |       | Key Input Interrupt                                 |       |

| 11.9 |       | Address Match Interrupt                             |       |

| 11.7 |       |                                                     | • • • |

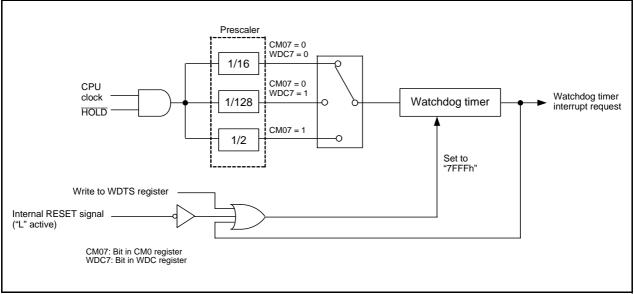

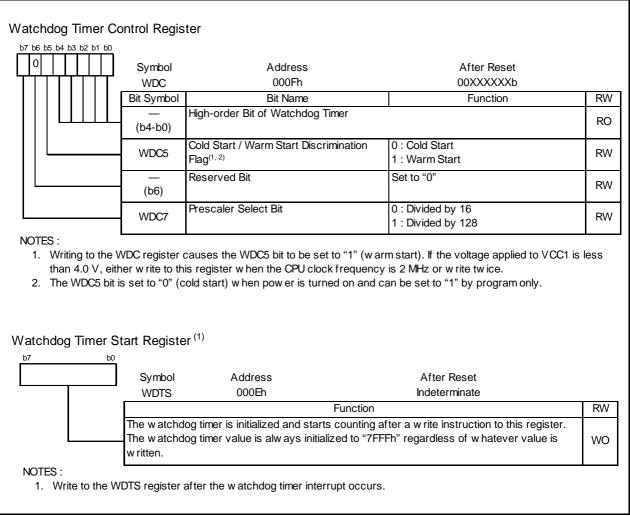

| 12.  | Wat   | tchdog Timer                                        | 79    |

|      |       |                                                     |       |

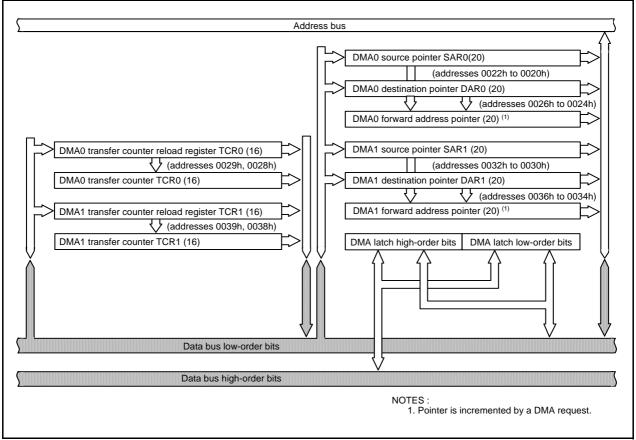

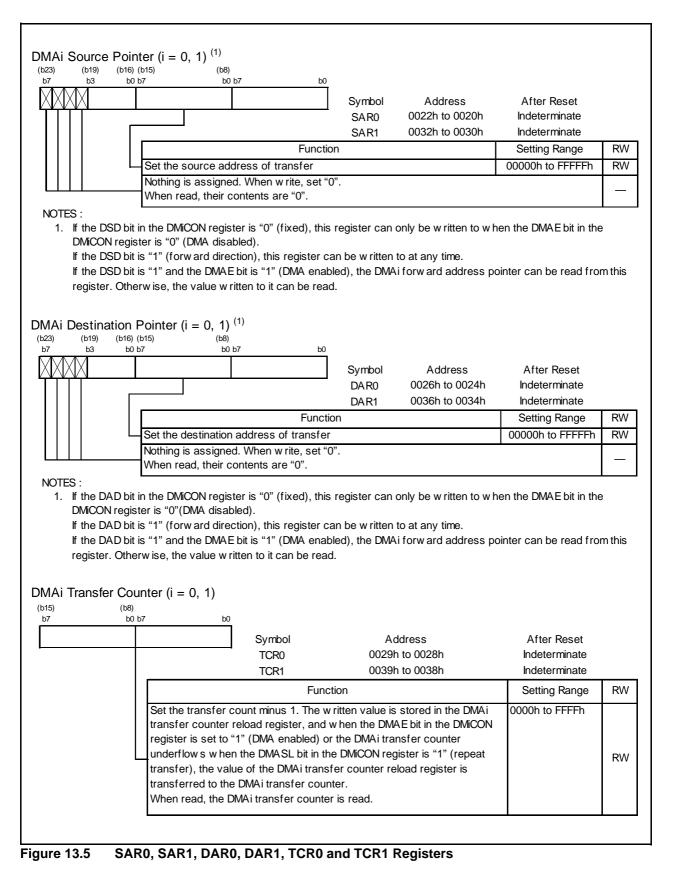

| 13.  | DM    | AC                                                  | 81    |

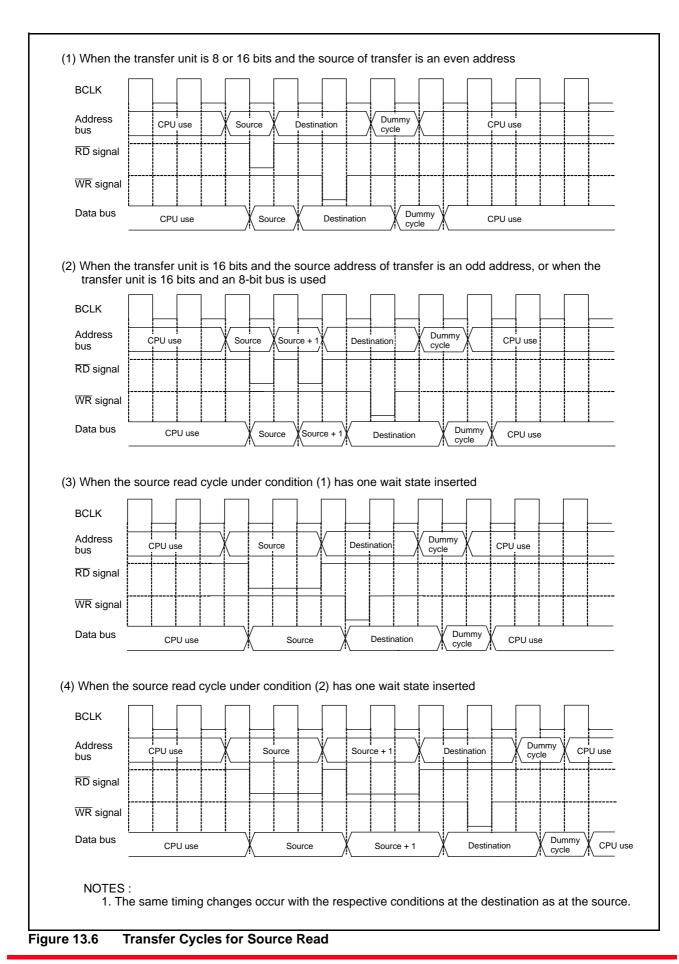

| 13.1 |       | Transfer Cycles                                     | . 87  |

| 13.  | .1.1  | Effect of Source and Destination Addresses          | . 87  |

| 13.  | .1.2  | Effect of BYTE Pin Level                            | . 87  |

| 13.  | .1.3  | Effect of Software Wait                             | . 87  |

| 13.  | .1.4  | Effect of RDY Signal                                | . 87  |

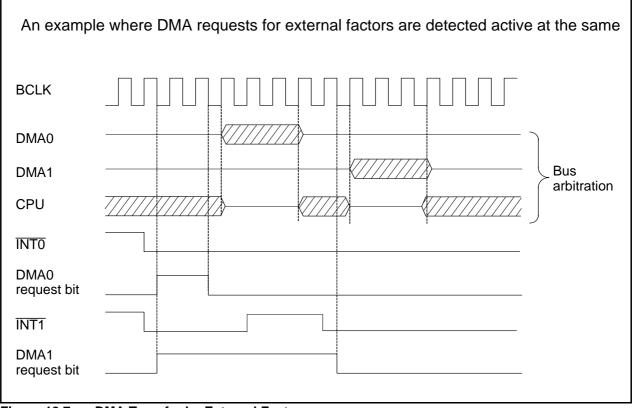

| 13.2 |       | DMA Transfer Cycles                                 | . 89  |

| 13.3 |       | DMA Enable                                          | . 90  |

| 13.4 |       | DMA Request                                         | . 90  |

| 13.5 |       | Channel Priority and DMA Transfer Timing            |       |

|      |       |                                                     |       |

| 14.  | Tim   | ers                                                 | 92    |

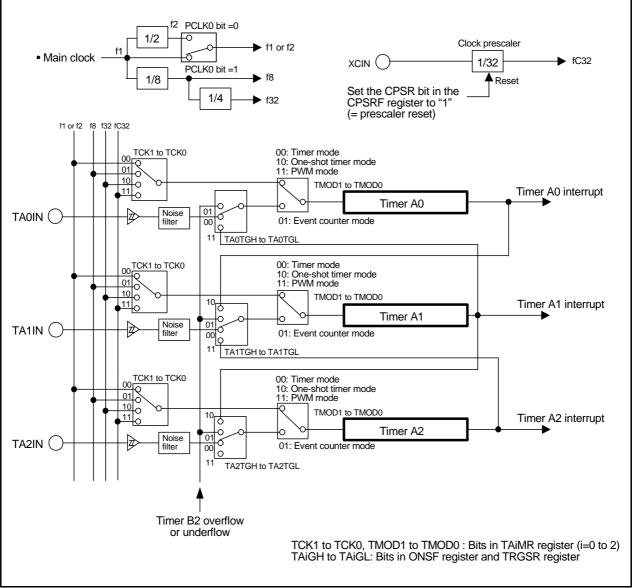

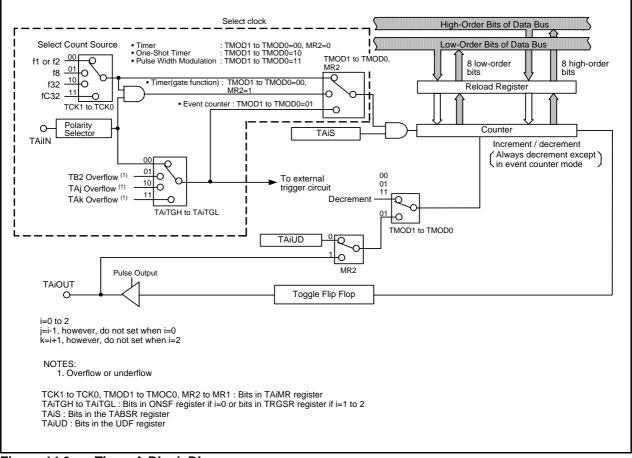

| 14.1 |       | Timer A                                             | . 94  |

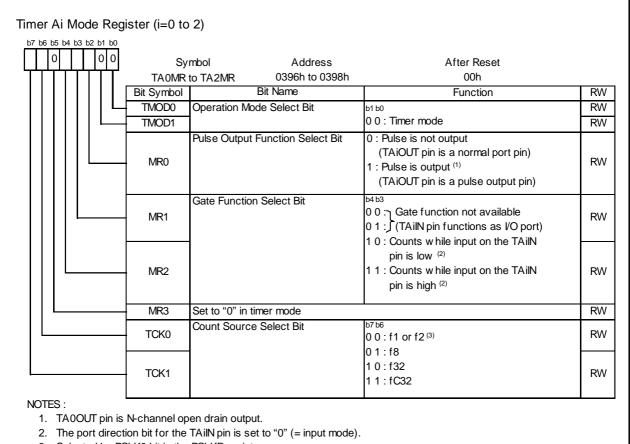

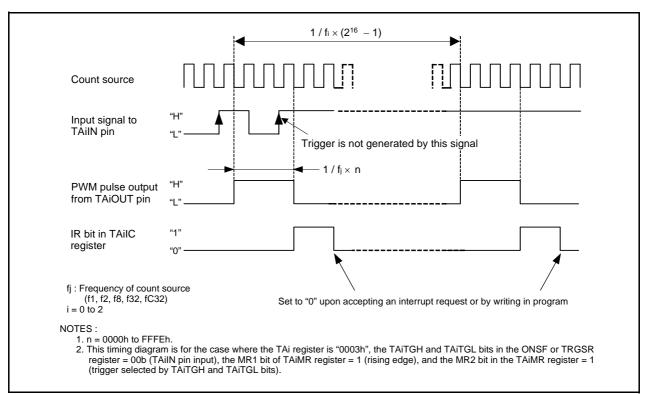

| 14.  | .1.1  | Timer Mode                                          | . 99  |

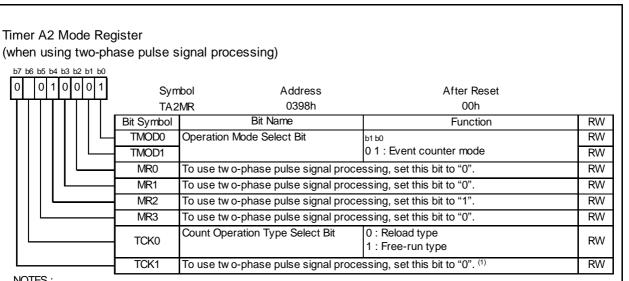

| 14.  | .1.2  | Event Counter Mode                                  | 101   |

| 14.  | .1.3  | One-shot Timer Mode                                 | 105   |

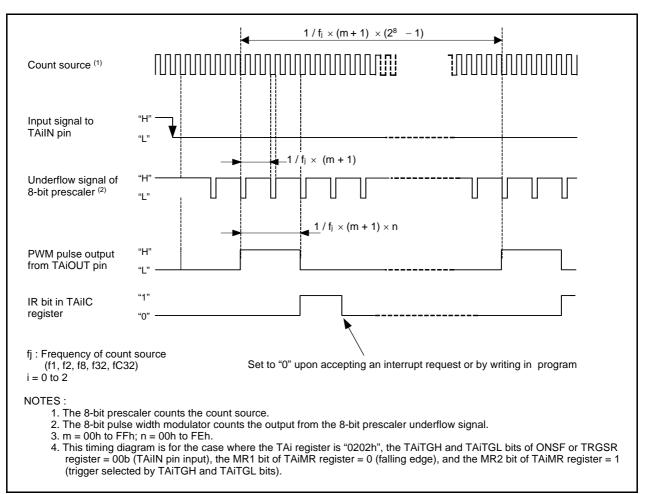

| 14.  | .1.4  | Pulse Width Modulation (PWM) Mode                   | 107   |

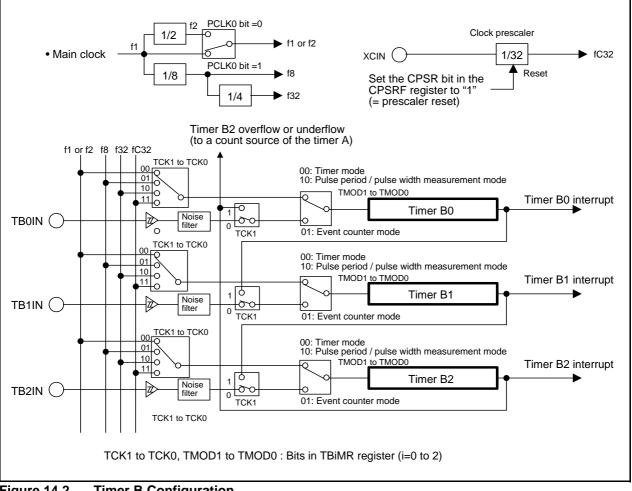

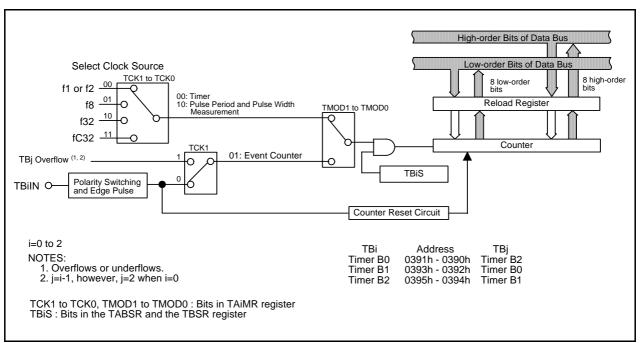

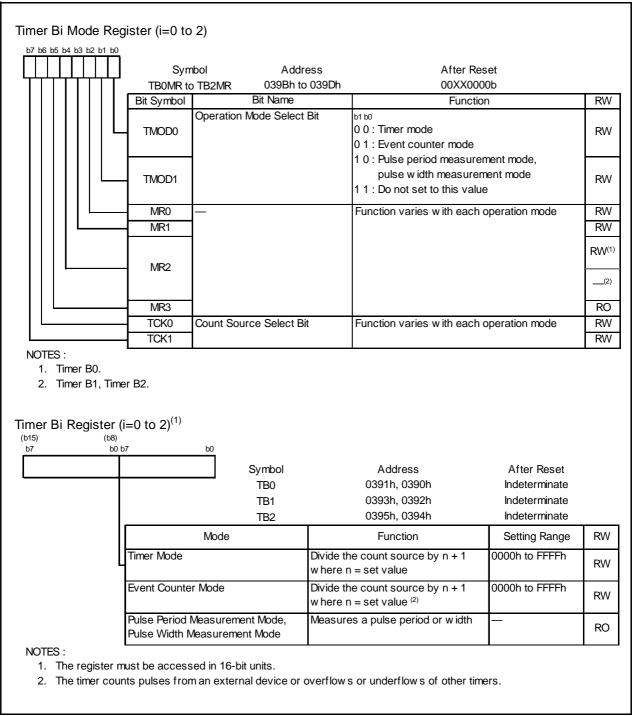

| 14.2 |       | Timer B                                             | 110   |

| 14.  | .2.1  | Timer Mode                                          |       |

| 14.  | .2.2  | Event Counter Mode                                  | 114   |

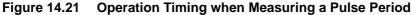

| 14.  | .2.3  | Pulse Period and Pulse Width Measurement Mode       | 116   |

|      |       |                                                     |       |

| 15.  | Ser   | ial Interface                                       | 119   |

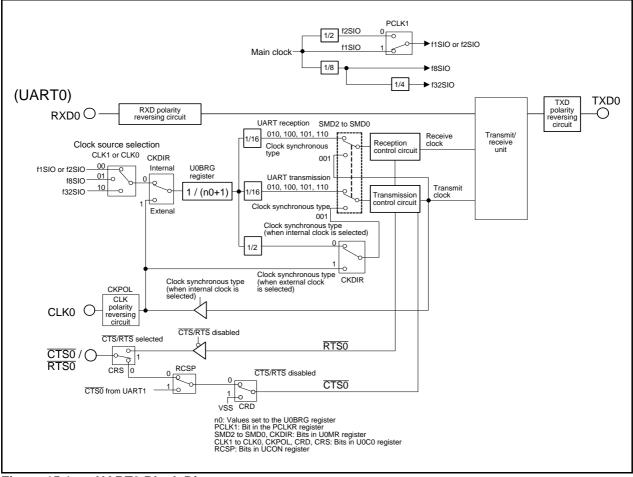

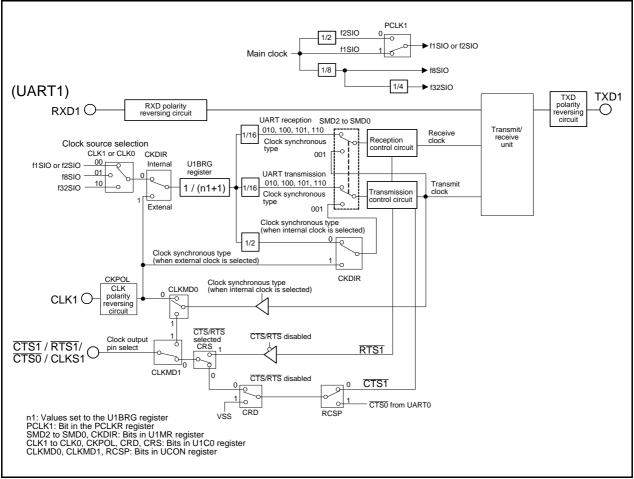

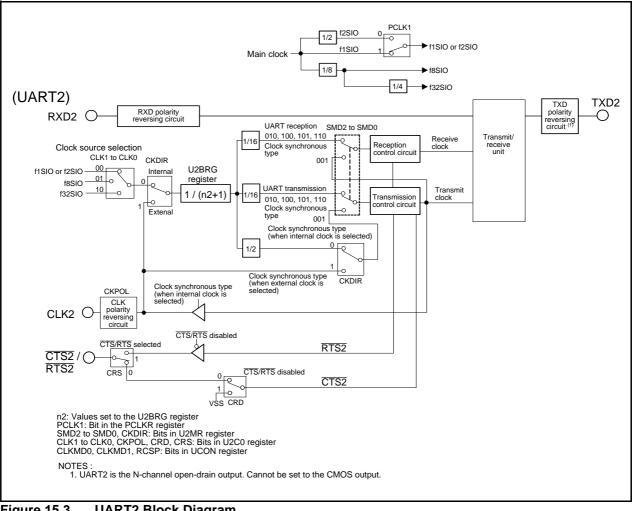

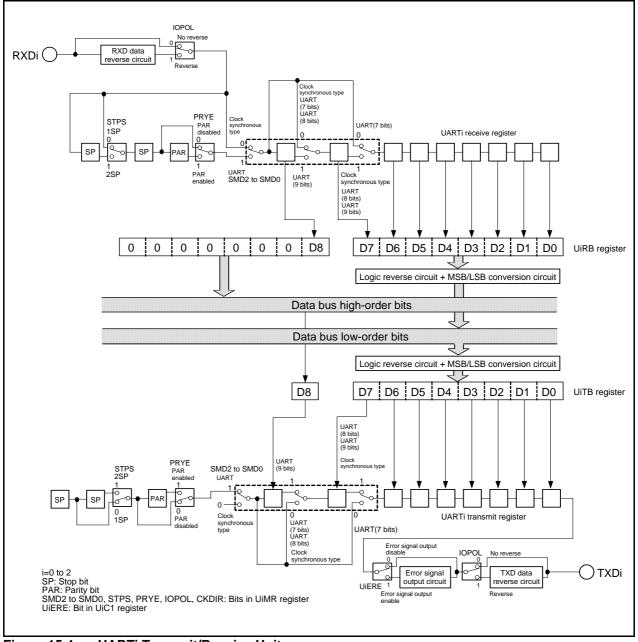

| 15.1 |       | UARTi (i=0 to 2)                                    | 119   |

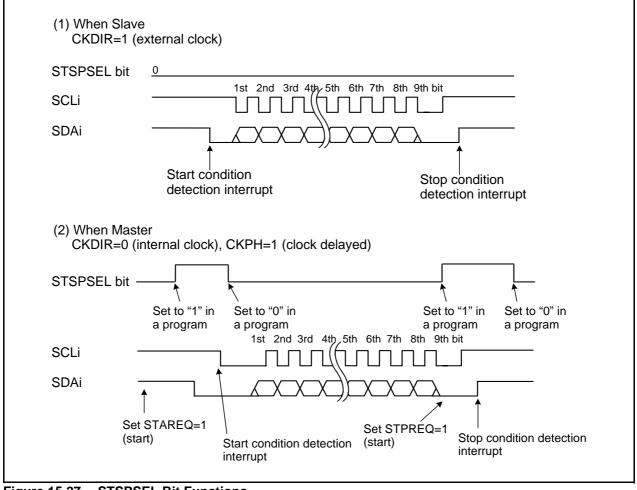

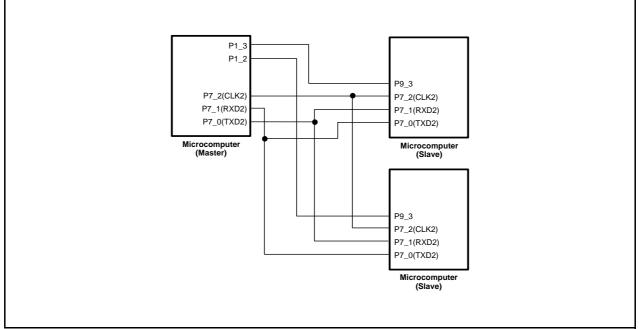

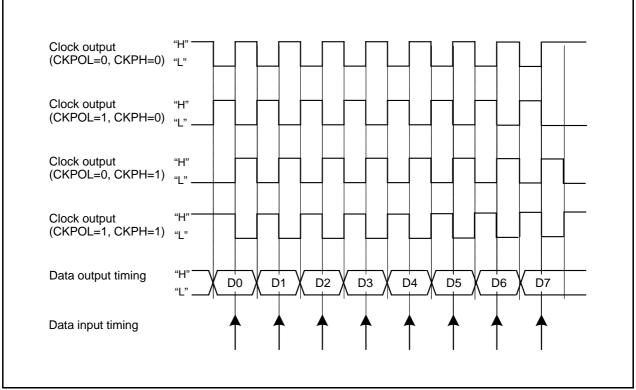

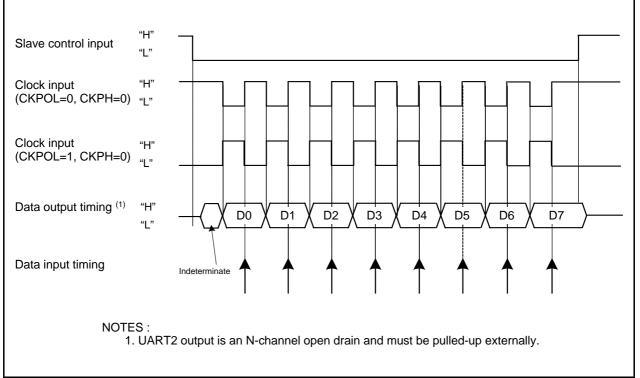

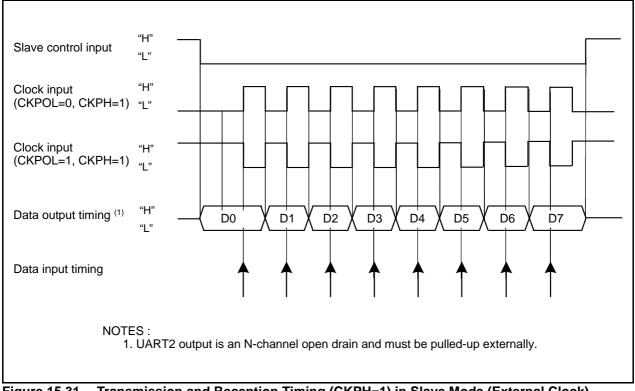

| 15.  | .1.1  | Clock Synchronous Serial I/O Mode                   |       |

| 15.  | .1.2  | Clock Asynchronous Serial I/O (UART) Mode           | 138   |

| 15.  | .1.3  | Special Mode 1 (I <sup>2</sup> C mode)              | 146   |

| 15.  | .1.4  | Special Mode 2                                      | 156   |

| 15.  | .1.5  | Special Mode 3 (IE mode)(UART2)                     | 161   |

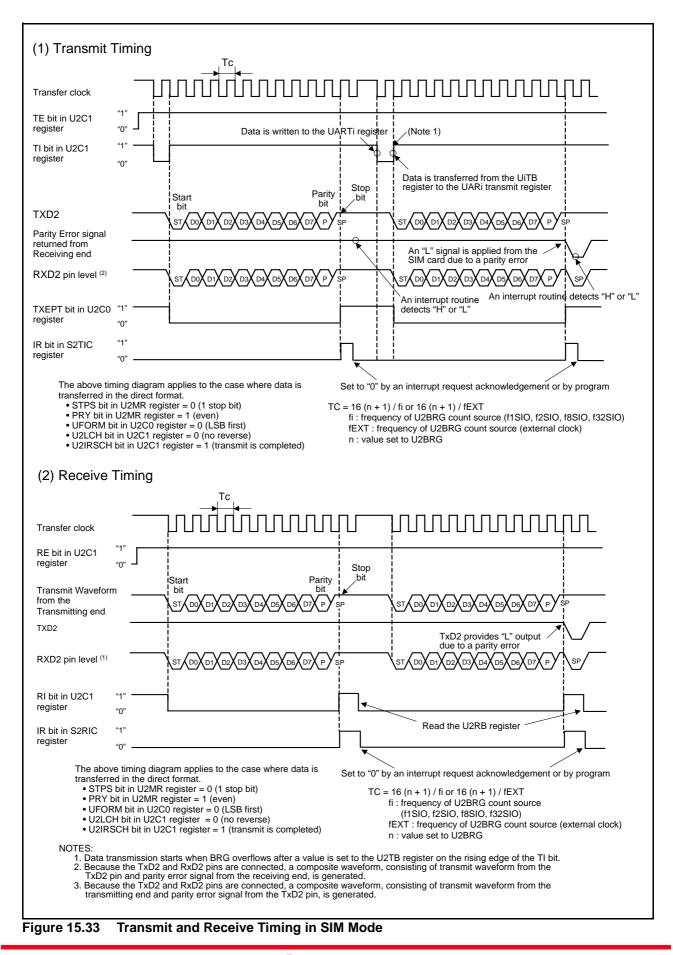

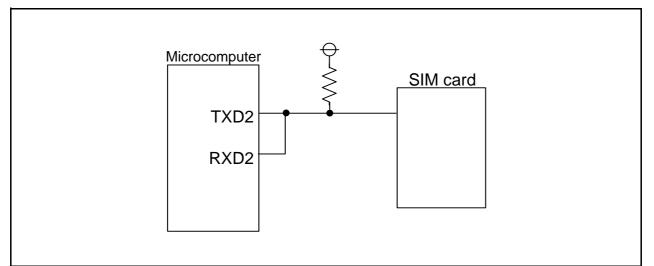

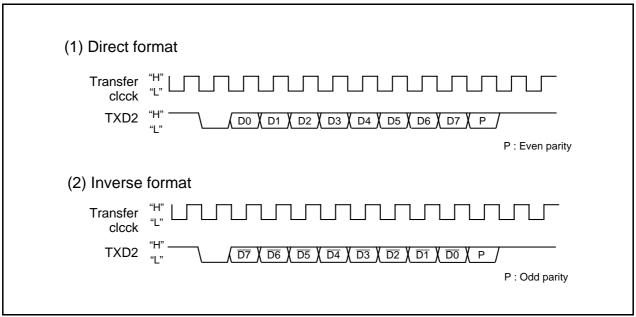

| 15.  | .1.6  | Special Mode 4 (SIM Mode) (UART2)                   | 163   |

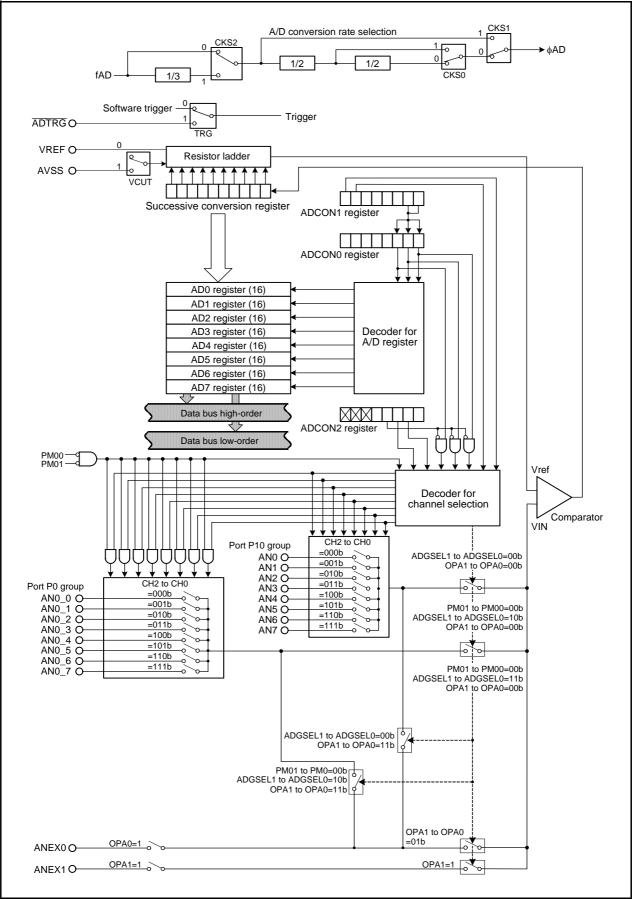

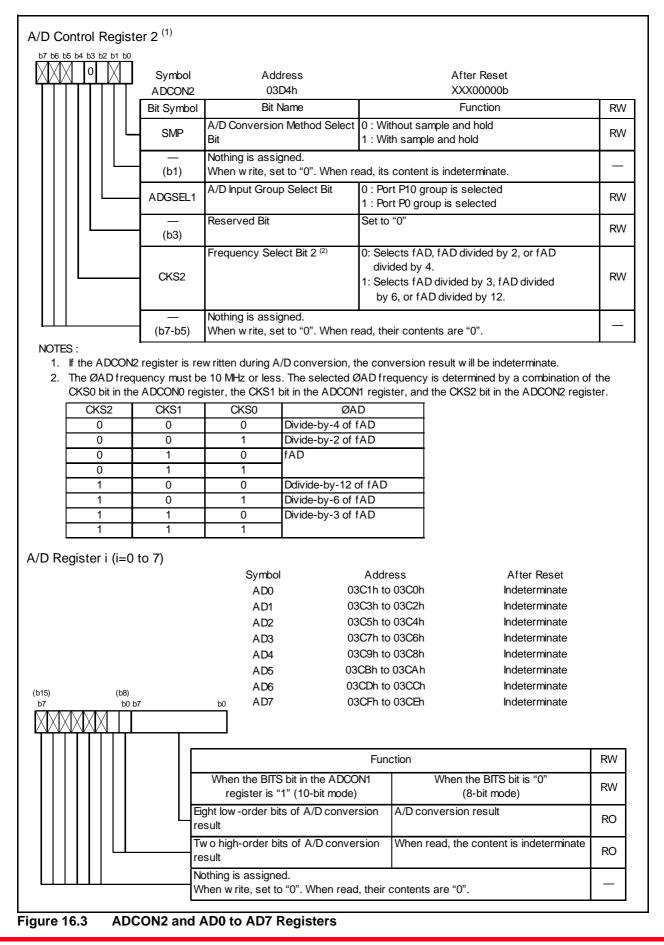

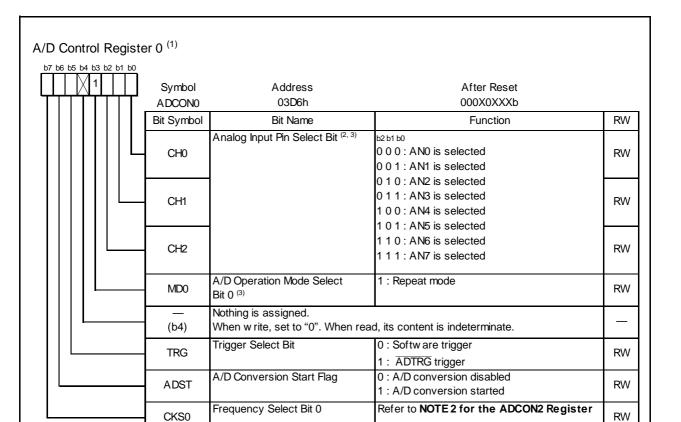

| 16. A/D  | Converter                                                                         | 168 |

|----------|-----------------------------------------------------------------------------------|-----|

| 16.1     | Mode Description                                                                  |     |

| 16.1.1   | One-Shot Mode                                                                     |     |

| 16.1.2   | Repeat Mode                                                                       |     |

| 16.2     | Function                                                                          |     |

| 16.2.1   | Resolution Select Function                                                        | 178 |

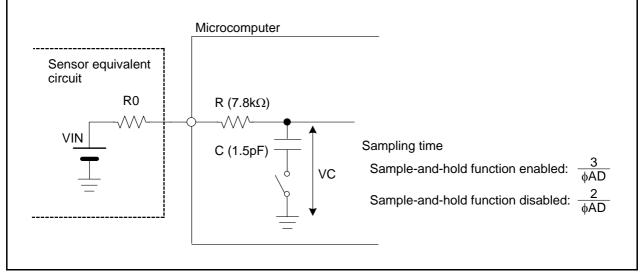

| 16.2.2   | Sample and Hold                                                                   | 178 |

| 16.2.3   | Extended Analog Input Pins                                                        | 178 |

| 16.2.4   | Current Consumption Reducing Function                                             | 178 |

| 16.2.5   | Output Impedance of Sensor under A/D Conversion                                   | 179 |

|          |                                                                                   |     |

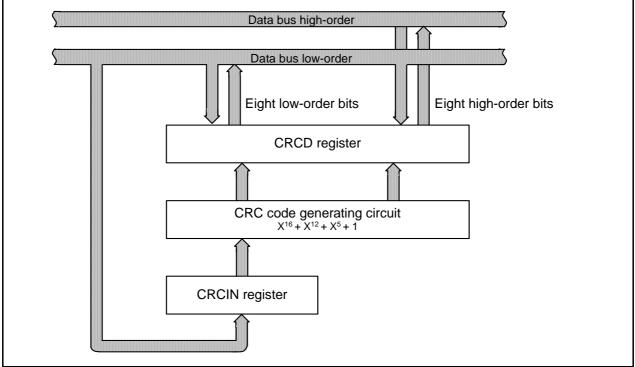

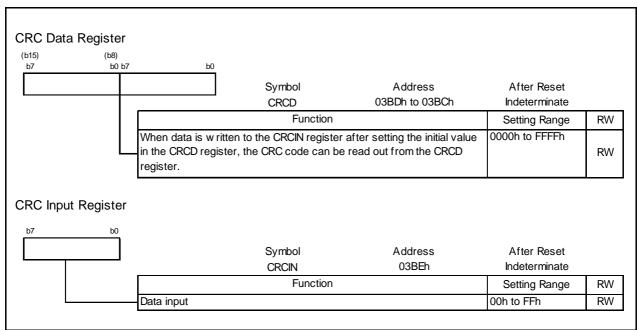

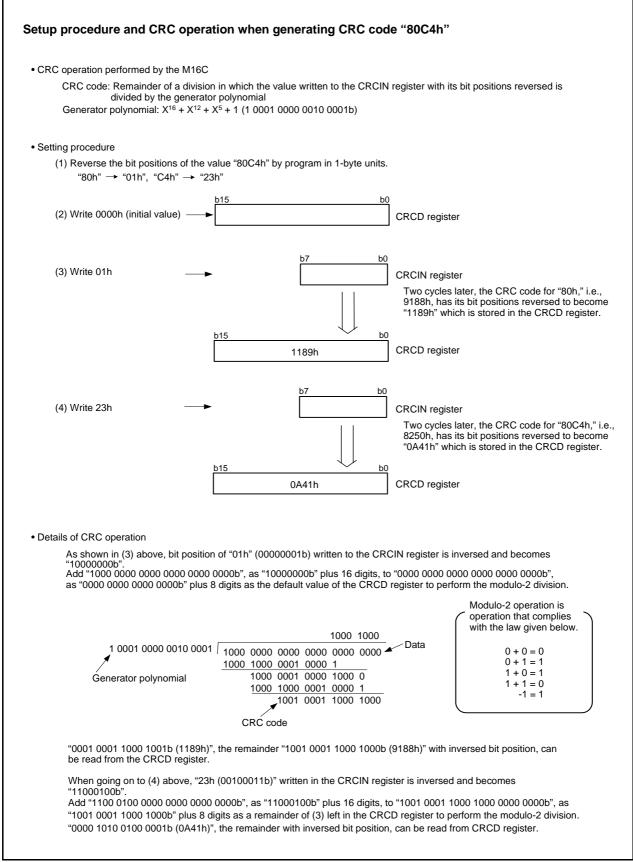

| 17. CR   | C Calculation                                                                     | 180 |

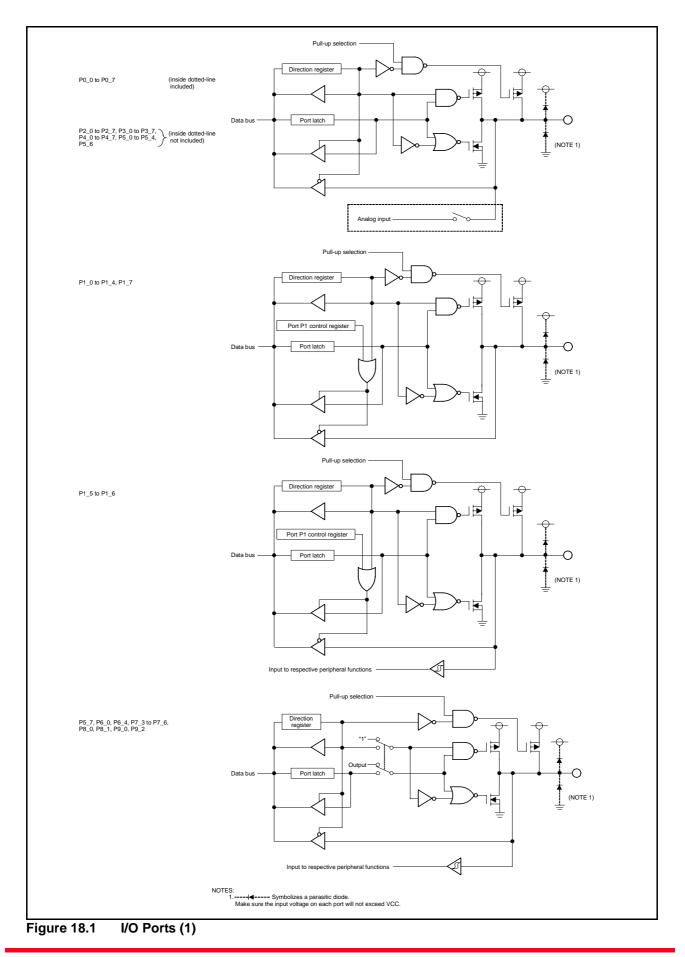

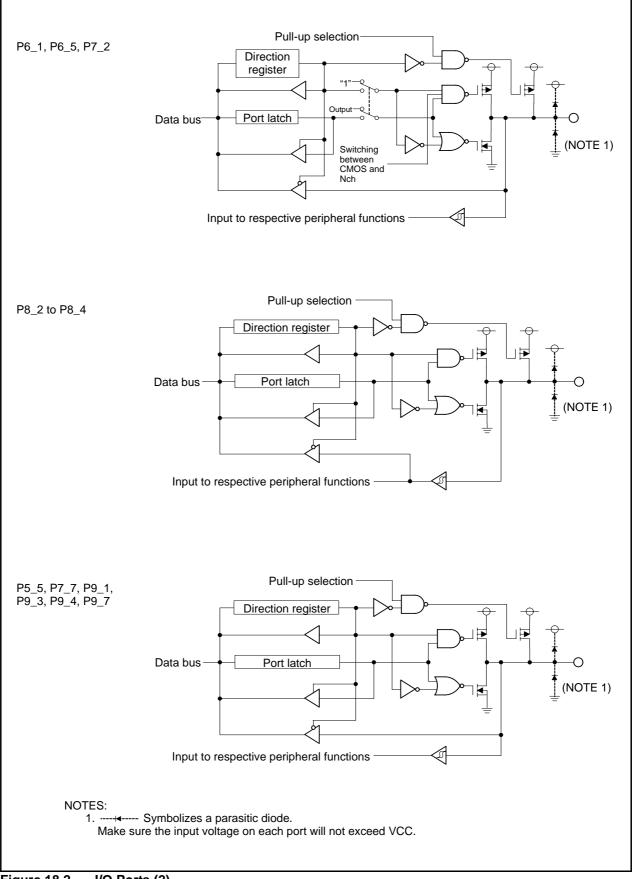

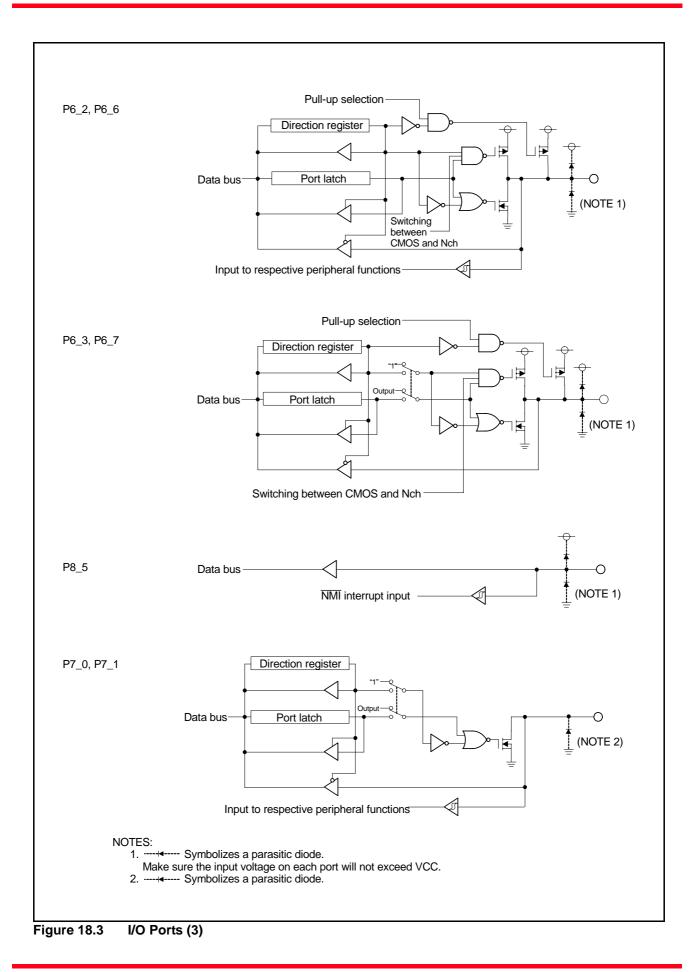

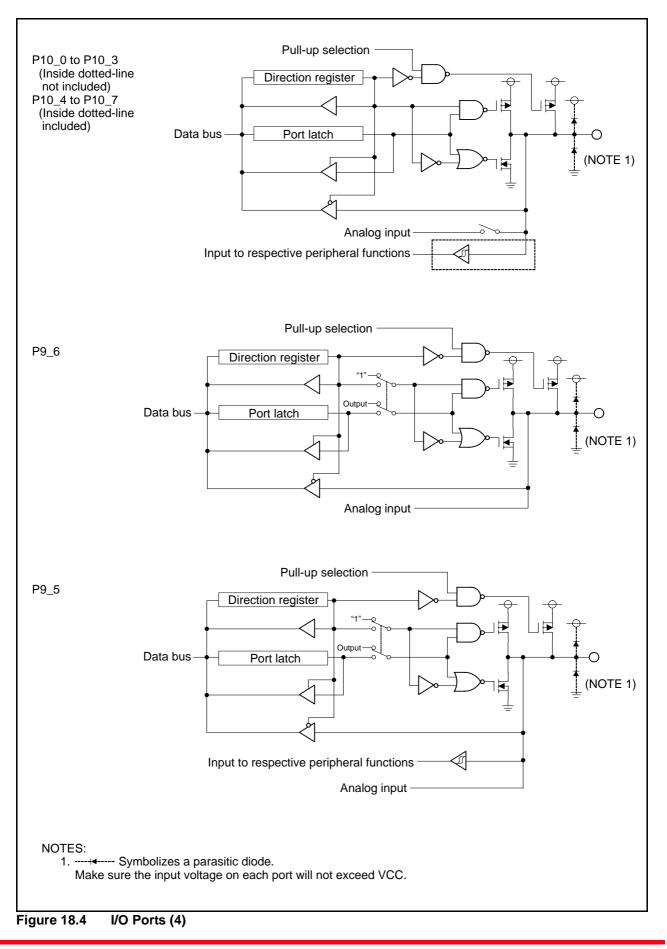

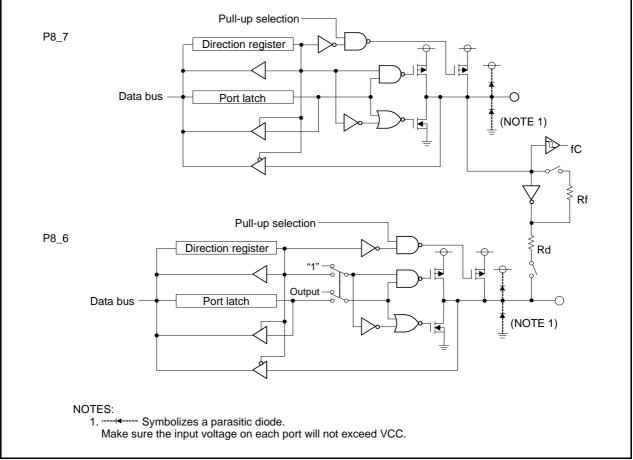

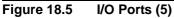

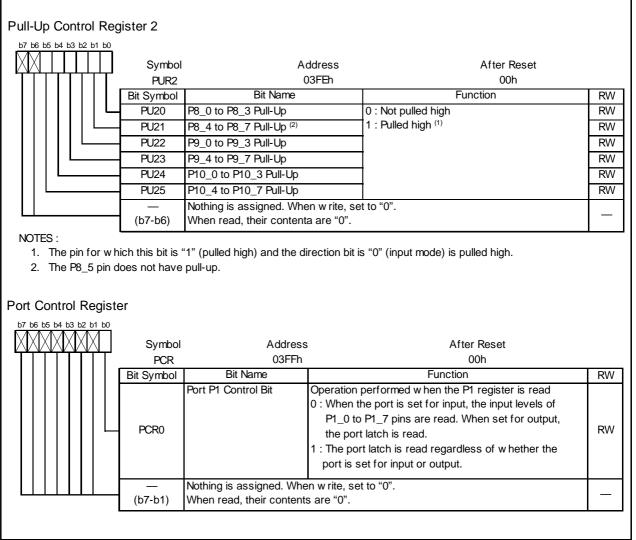

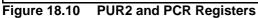

| 18. Pro  | grammable I/O Ports                                                               | 182 |

| 18.1     | Port Pi Direction Register (PDi Register, i = 0 to 10)                            |     |

|          | Port Pi Register (Pi Register, $i = 0$ to 10)                                     |     |

|          | Pull-up Control Register 0 to Pull-up Control Register 2 (PUR0 to PUR2 Registers) |     |

| 18.4     | Port Control Register (PCR Register)                                              |     |

|          |                                                                                   |     |

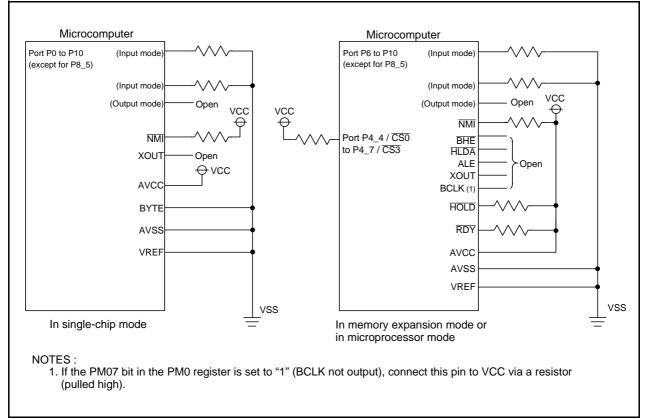

| 19. Flas | sh Memory Version                                                                 | 195 |

| 19.1     | Memory Map                                                                        | 196 |

| 19.1.1   | Boot Mode                                                                         | 197 |

| 19.2     | Functions To Prevent Flash Memory from Rewriting                                  | 197 |

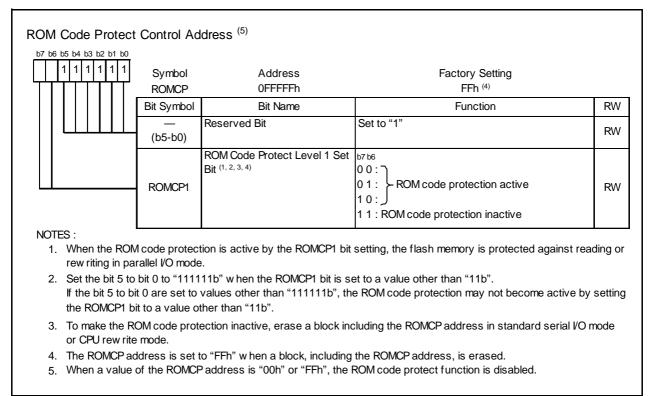

| 19.2.1   | ROM Code Protect Function                                                         | 197 |

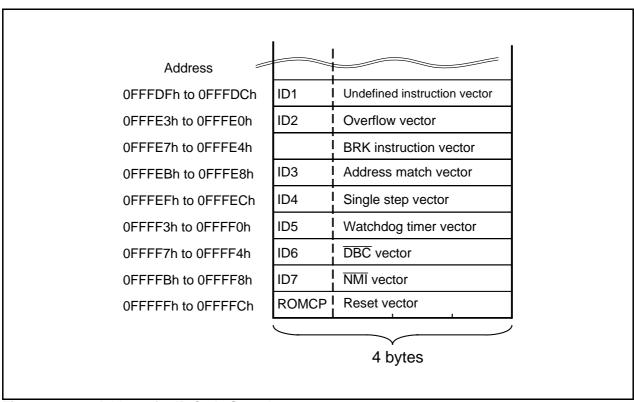

| 19.2.2   | ID Code Check Function                                                            | 198 |

| 19.2.3   | Forced Erase Function                                                             | 199 |

| 19.3     | CPU Rewrite Mode                                                                  |     |

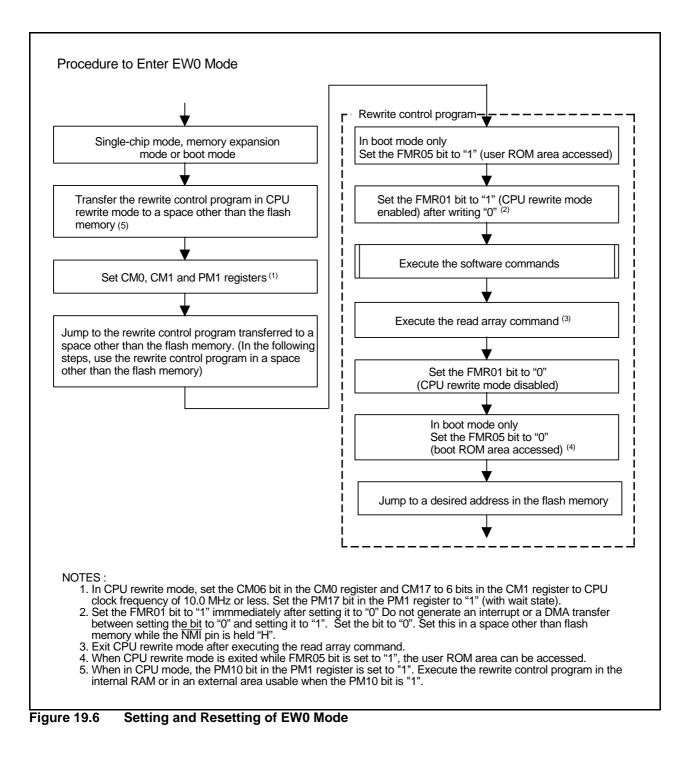

| 19.3.1   | EW0 Mode                                                                          |     |

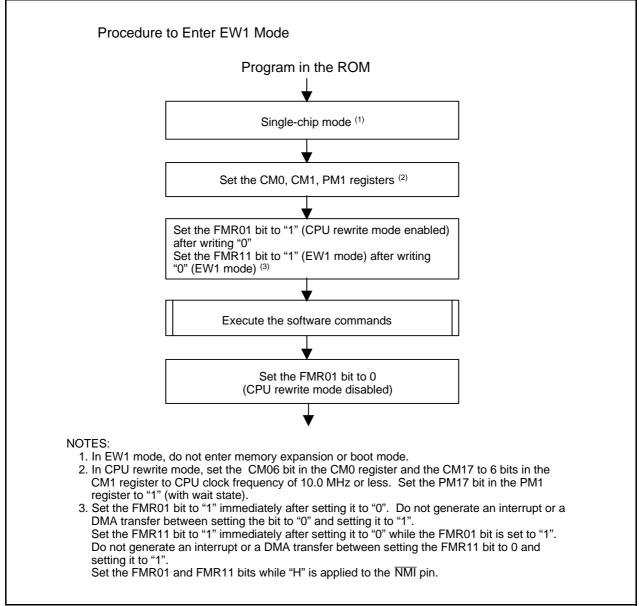

| 19.3.2   | EW1 Mode                                                                          |     |

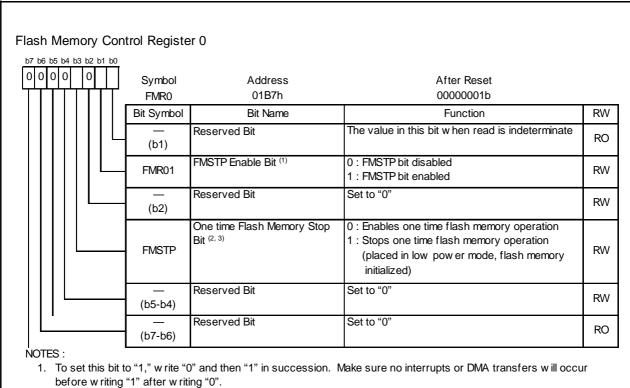

| 19.3.3   | Flash Memory Control Register (FMR0 and FMR1 registers)                           |     |

| 19.3.4   | Precautions on CPU Rewrite Mode                                                   |     |

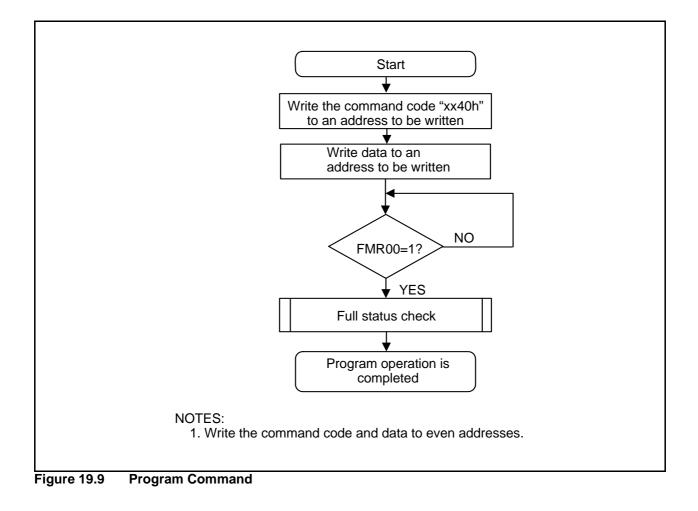

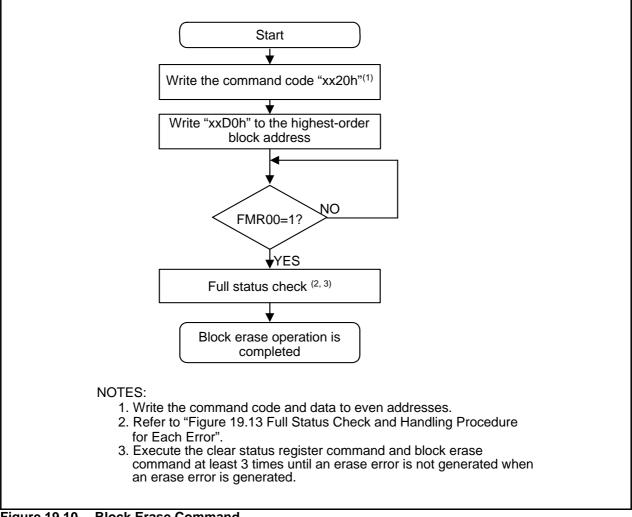

| 19.3.5   | Software Commands                                                                 |     |

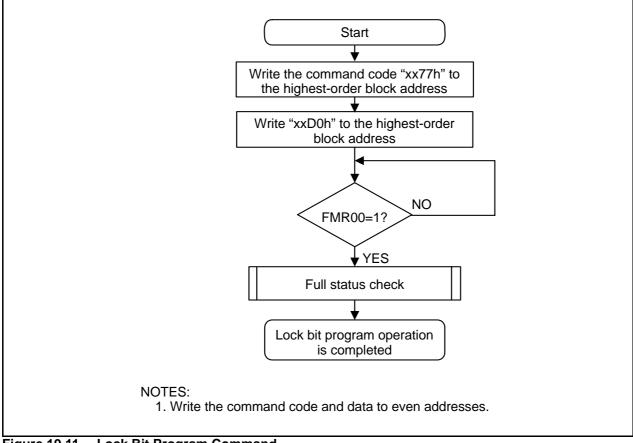

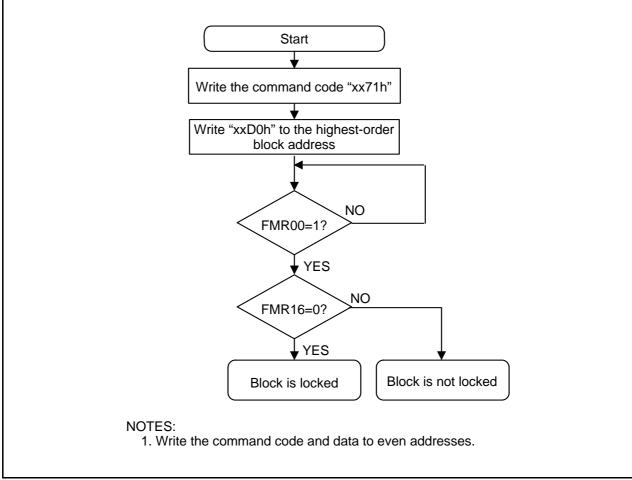

| 19.3.6   | Data Protect Function                                                             |     |

| 19.3.7   | Status Register                                                                   |     |

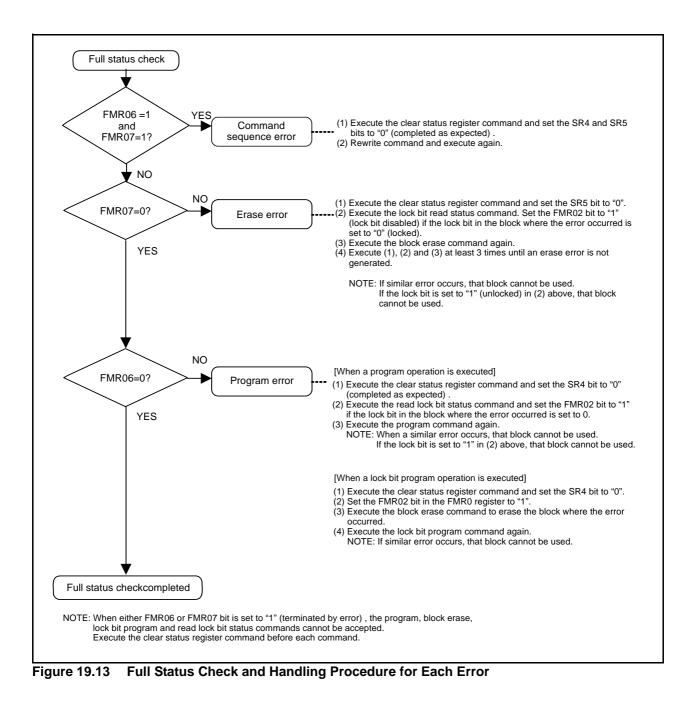

| 19.3.8   | Full Status Check                                                                 |     |

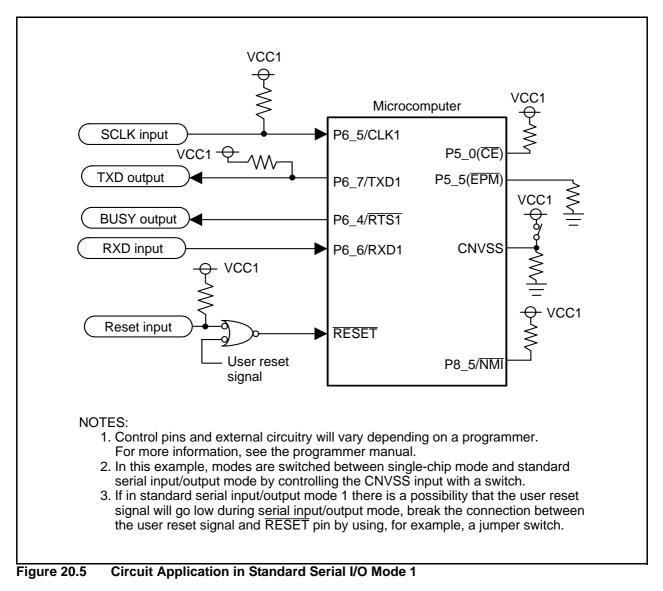

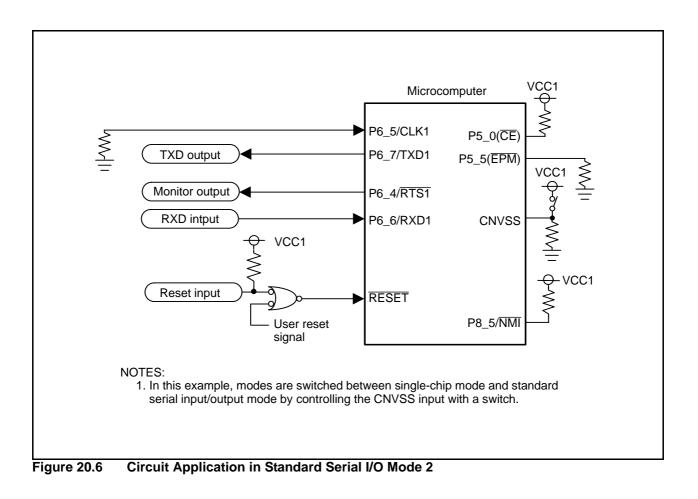

|          | Standard Serial I/O Mode                                                          |     |

| 19.4.1   | ID Code Check Function                                                            |     |

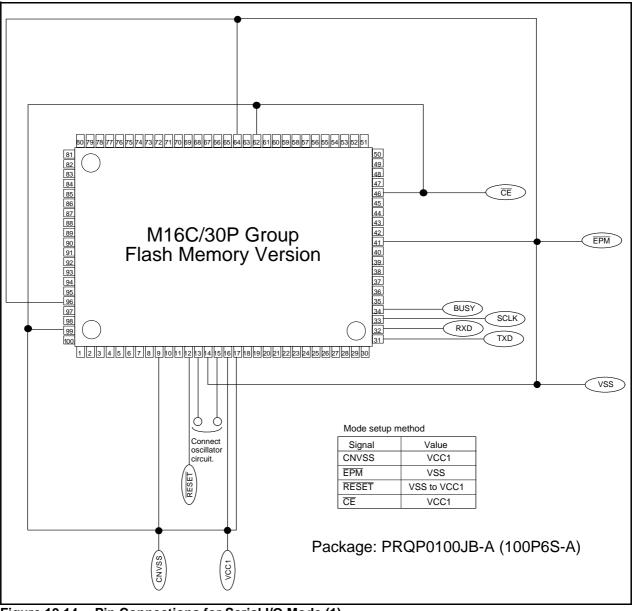

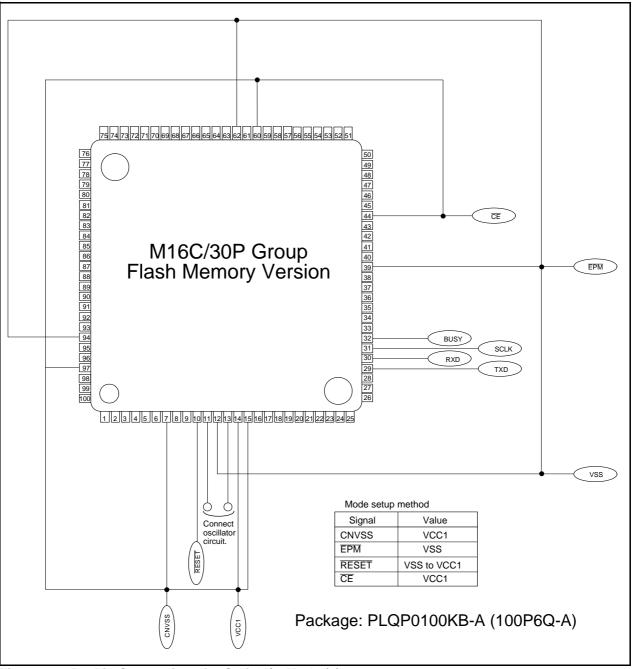

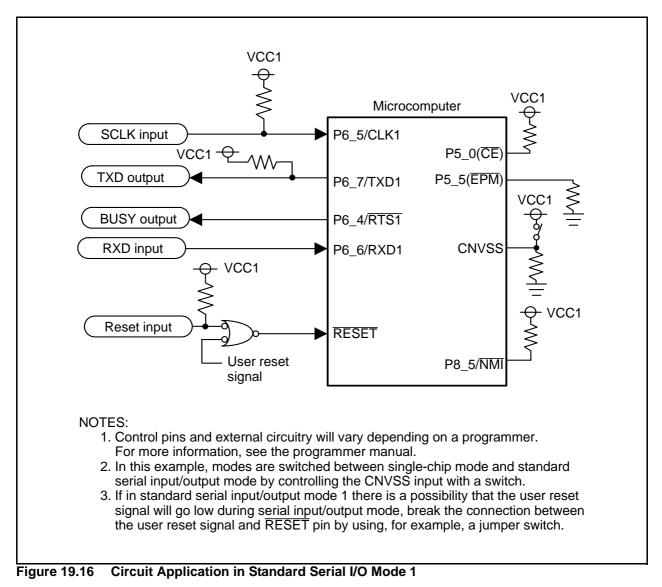

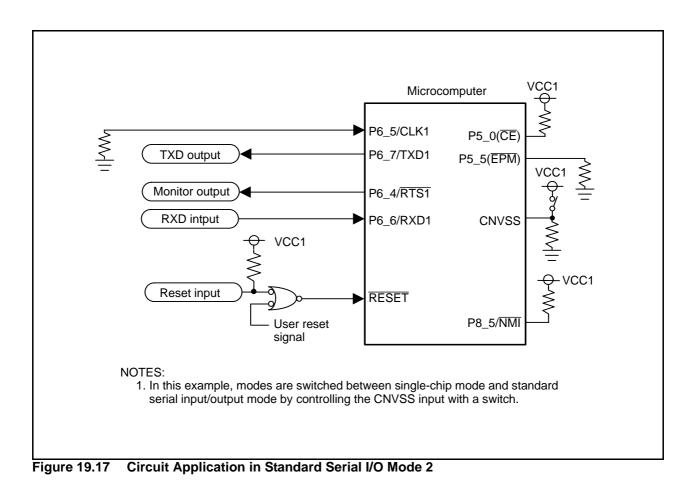

| 19.4.2   | Example of Circuit Application in the Standard Serial I/O Mode                    |     |

|          | Parallel I/O Mode<br>User ROM and Boot ROM Areas                                  |     |

| 19.5.1   |                                                                                   |     |

| 19.5.2   | ROM Code Protect Function                                                         | 221 |

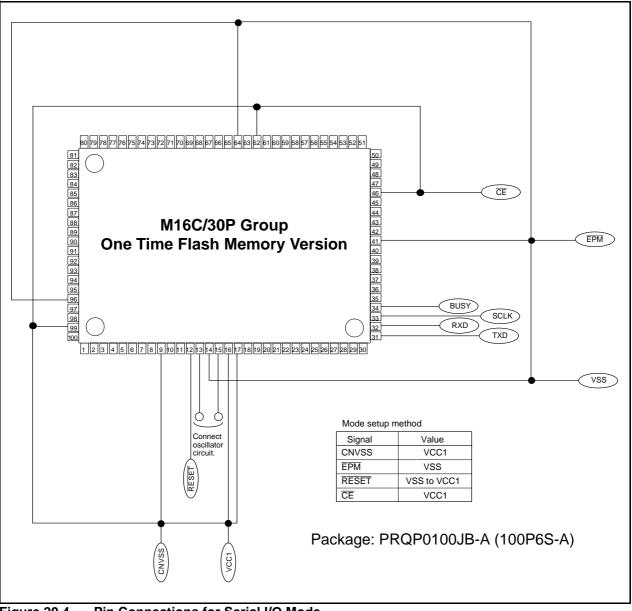

| 20. One  | Time Flash Version                                                                | 228 |

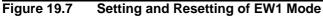

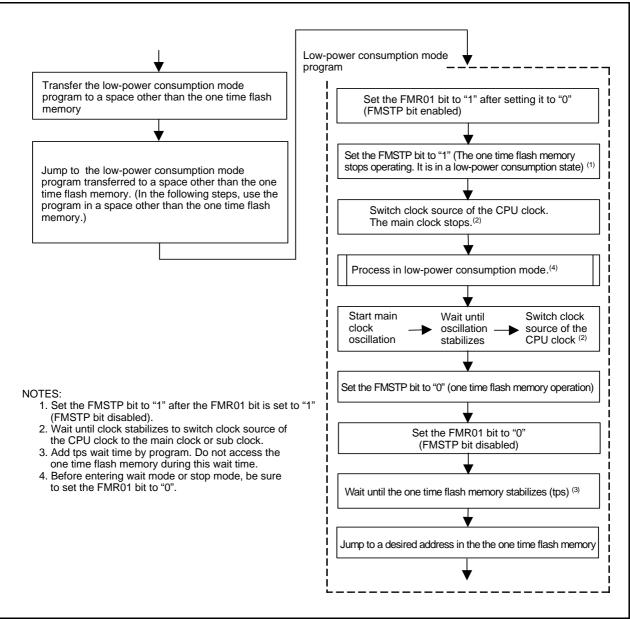

| 20.1     | Low Consumption Mode                                                              |     |

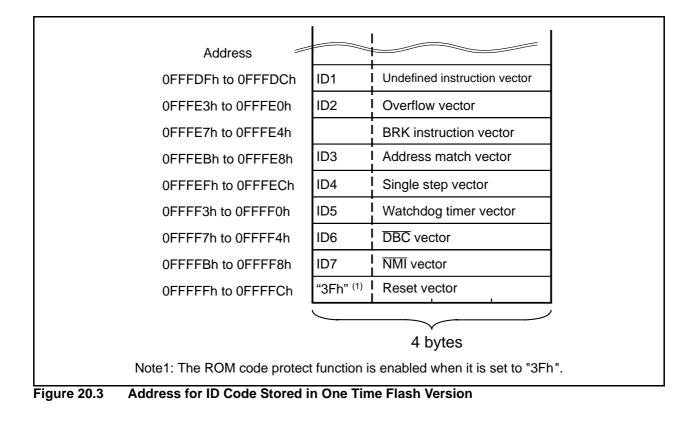

| 20.2     | Functions to Prevent One Time Flash Version from Being Read                       | 231 |

| 20.2.1   | ROM Code Protect Function                                                         | 231 |

| 20.2.2   | ID Code Check Function                                                            |     |

| 20. | .3               | Standard Serial I/O Mode                                                                     | 232 |

|-----|------------------|----------------------------------------------------------------------------------------------|-----|

| 2   | 20.3.1           | ID Code Check Function                                                                       | 232 |

| 2   | 20.3.2           | Example of Circuit Application in the Standard Serial I/O Mode                               | 235 |

|     |                  |                                                                                              |     |

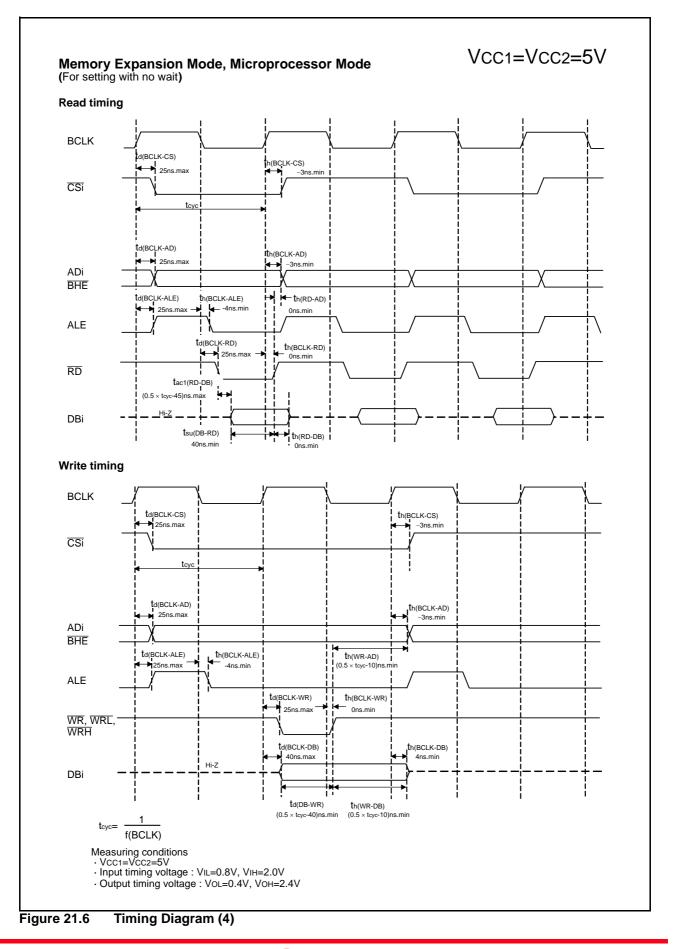

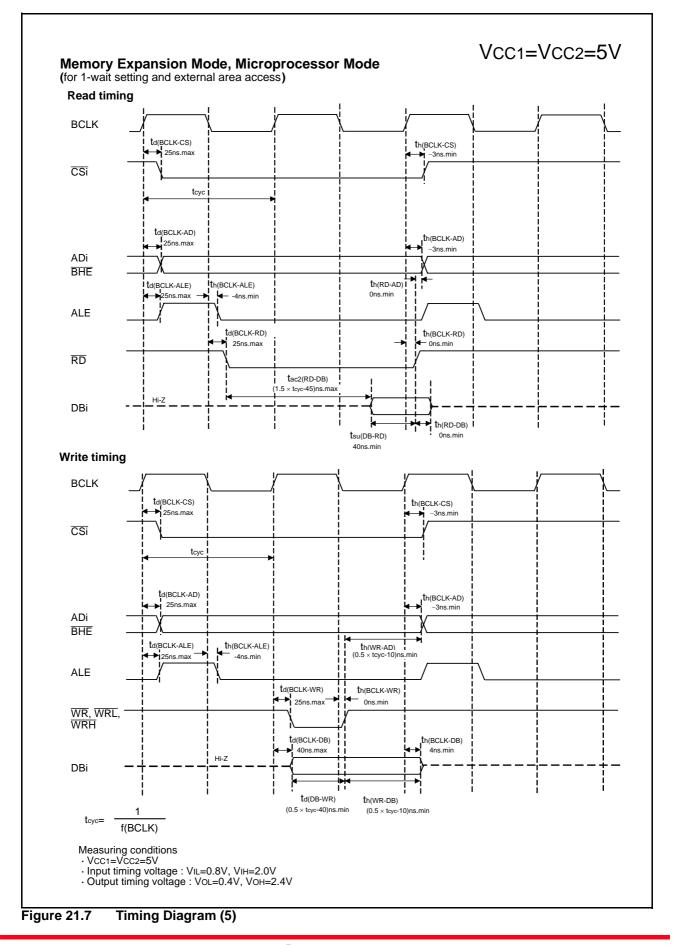

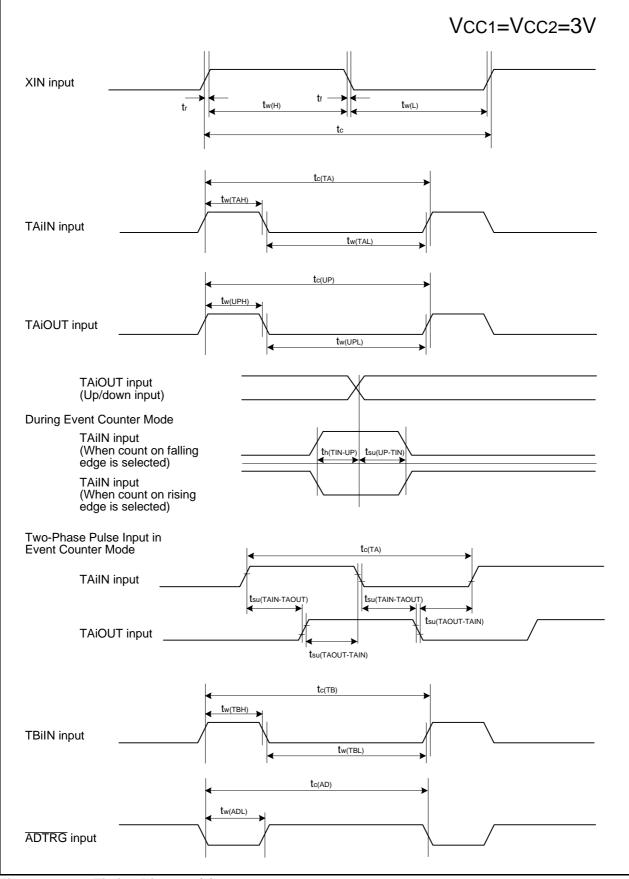

| 21. | Ele              | ctrical Characteristics                                                                      | 237 |

|     |                  |                                                                                              |     |

| 22. | Usa              | age Precaution                                                                               | 267 |

| 22. | . –              | SFR                                                                                          | 267 |

| 2   | 22.1.1           |                                                                                              |     |

| 22. | .2               | Reset                                                                                        |     |

| 22. |                  | Bus                                                                                          |     |

| 22. |                  | Precautions for Power Control                                                                |     |

| 22. |                  | Precautions for Protect                                                                      |     |

| 22. |                  | Precautions for Interrupt                                                                    |     |

|     | 22.6.1           | Reading address 00000h                                                                       |     |

|     | 22.6.2           | Setting the SP                                                                               |     |

|     | 22.6.3           | The NMI Interrupt                                                                            |     |

|     | 22.6.4           | Changing the Interrupt Generate Factor                                                       |     |

|     | 22.6.5           | INT Interrupt                                                                                |     |

|     | 22.6.6           | Rewrite the Interrupt Control Register                                                       |     |

|     | 22.6.7           | Watchdog Timer Interrupt                                                                     |     |

| 22. |                  | Precautions for DMAC                                                                         |     |

|     | 22.7.1           | Write to DMAE Bit in DMiCON Register<br>Precautions for Timers                               |     |

| 22. | .8<br>22.8.1     | Timer A                                                                                      |     |

| _   | 22.8.1<br>22.8.2 |                                                                                              |     |

| 22. |                  | Precautions for Serial interface                                                             |     |

|     | .9<br>22.9.1     | Clock Synchronous Serial I/O                                                                 |     |

|     | 22.9.1<br>22.9.2 | •                                                                                            |     |

| 22. |                  | A/D Converter                                                                                |     |

| 22. |                  | Precautions for Programmable I/O Ports                                                       |     |

| 22. |                  | Electric Characteristic Differences Between Mask ROM and Flash Memory Version Microcomputers |     |

| 22. |                  | Mask ROM                                                                                     |     |

| 22. |                  | Flash Memory Version                                                                         |     |

|     |                  | •                                                                                            |     |

|     | 22.14.           |                                                                                              |     |

|     | 22.14.           |                                                                                              |     |

|     | 22.14.           |                                                                                              |     |

|     | 22.14.           |                                                                                              |     |

| 2   | 22.14.           | -                                                                                            |     |

|     | 22.14.           | -                                                                                            |     |

| 2   | 22.14.           | -                                                                                            |     |

|     |                  | 9 Prohibited instructions                                                                    |     |

|     |                  | 10 Interrupts                                                                                |     |

|     |                  | 11 How to access                                                                             |     |

|     |                  | 12 Writing in the user ROM area                                                              |     |

| 2   | 22.14.           | 13 DMA transfer                                                                              | 285 |

|     |                  |                                                                                              |     |

| 22.15 O      | ne Time Flash Version                    | 286 |

|--------------|------------------------------------------|-----|

| 22.15.1      | Stop mode                                | 286 |

| 22.15.2      | Wait mode                                | 286 |

| 22.15.3      | Operation speed                          | 286 |

| 22.15.4      | Prohibited Instructions                  | 286 |

| 22.15.5      | Interrupts                               | 286 |

| 22.15.6      | How to access                            | 286 |

| 22.16 P      | recautions for Noise                     | 287 |

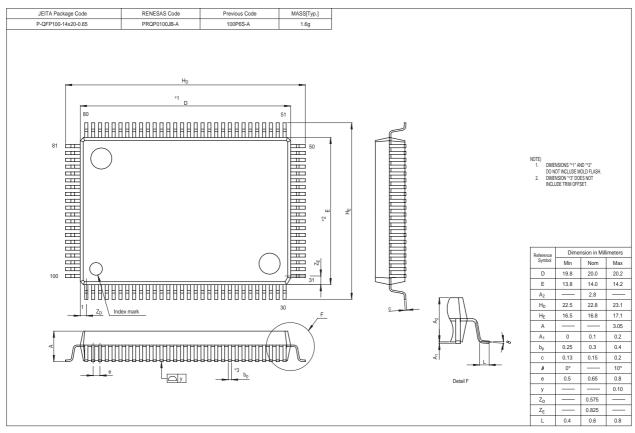

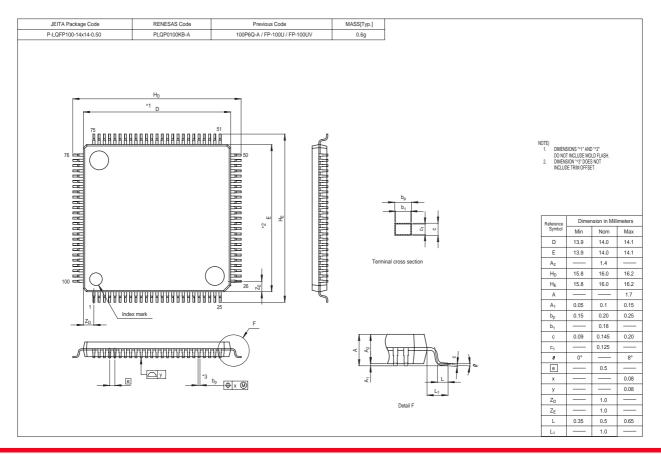

| Appendix 1.  | Package Dimensions                       | 288 |

| Appendix 2.  | Difference between M16C/62P and M16C/30P | 289 |

| Register Inc | lex                                      | 291 |

## SFR Page Reference

| 0001h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Address | Register                                | Symbol          | Page   | Address | Register                                                 | Symbol  | Page     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|-----------------|--------|---------|----------------------------------------------------------|---------|----------|

| 00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         000200         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         00020         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200         000200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0000h   |                                         |                 |        | 0040h   |                                                          |         |          |

| 0000h         Processor Mode Register 1         PMI         310         00441         NT3 Interrupt Control Register         PT           0000h         Processor Mode Register 1         PMI         311         00441         NT3 Interrupt Control Register         PT           0000h         Check Control Register 1         CMI         48         00471         UART BUS Collision Detection Interrupt Control Register         UBCNIC         68           0000h         Check Control Register         CRC         00441         NT4 Interrupt Control Register         DRC/CC         60           0000h         Check Control Register         PRC         00441         NT4 Interrupt Control Register         DRC/CC         60           0000h         Check Register         PRC         60         00441         NT4 Interrupt Control Register         DMIC/C         60           0000h         Check Register         PRC         78         00441         NT4 Interrupt Control Register         DMIC/C         60           0000h         Match Register         PRC         78         00441         NT4 Interrupt Control Register         DMIC/C         60           0000h         The Control Register         PRC         78         00441         NT4 Interrupt Control Register         SRIC         6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0001h   |                                         |                 |        | 0041h   |                                                          |         |          |

| 00004h         Piconson Mode Register         PND         014         NTAIC         67           00050h         Picosson Mode Register         PND         014         0045h         UNEXPICE         PICONSON System Cock Cotted Register         CMD         47           00050h         System Cock Cotted Register         CMD         47         0045h         UNEXPICE         0045h         UNEXPICE         PICONSON Register         NTAIC         67           00050h         Cock Cotted Register         CSR         35         0045h         UNEXPICE         PICONSON Register         NTAIC         67           00050h         Protect Register         PICON         60         0045h         UNEXPICE         PICON         60           00050h         Protect Register         PICON         60         0045h         UNEXPICE         PICON         60           00050h         Madres Match Interrupt Register         WTC         28, 80         0045h         UNEXPICE         PICON         Fill                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0002h   |                                         |                 |        | 0042h   |                                                          |         |          |

| 0000h         Processor Mode Register 1         PMI         31         0045h         Common System Cock Corrul Register 0         CMI         44           0000h         System Cock Corrul Register 1         CMI         44         0045h         Common System Cock Corrul Register 1         CMI         44           0000h         Protects Corrul Register 1         CMI         44         0045h         Common System Cock Corrul Register 1         CMI         47           0000h         Protects Register 1         CMI         48         0048h         CMI Control Register 1         CMI         67           0000h         Protects Register 1         CMI         48         0048h         CMI Control Register 1         CMI Control Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0003h   |                                         |                 |        | 0043h   |                                                          |         |          |

| 00009h         System Conck Corten Register         CMI         44           0007b         System Conck Corten Register         CSR         35           0007b         Chip Selec Control Register         CSR         35           0007b         System Control Register         PRCR         60           0007b         March Interrupt Control Register         PTCL         60           0007b         March Interrupt Control Register         PTCL         60           0007b         March Interrupt Control Register         DMIC 16         60           0007b         March Interrupt Control Register         DMIC 16         60           0007b         March Interrupt Control Register         DMIC 26         60           0007b         March Interrupt Control Register         DMIC 26         60           0007b         Address Match Interrupt Register         WDT 2         80           0007b         Address Match Interrupt Register         RMAD 7         76           0007b         Address Match Interrupt Register         RMAD 7         76           0007b         Address Match Interrupt Register         RMAD 7         76           007b         Address Match Interrupt Register         RMAD 7         76           007b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0004h   | Processor Mode Register 0               | PM0             | 30     | 0044h   | INT3 Interrupt Control Register                          | INT3IC  | 67       |

| 0007h         System Clock Control Register 1         CM1         46           0008h         Chys Barthan Stream Control Register Control Regi                                                                                     | 0005h   | Processor Mode Register 1               | PM1             | 31     | 0045h   |                                                          |         |          |

| 0008h         Chip Saleri Cortrol Register         CSR         36         0.048h         Chip Saleri Cortrol Register         HC4C         67           0008h         Address Mutch Interrupt Enable Register         PRCR         80         0.048h         LMT2 Eac Oldinon Description Register         DMAC         66           0008h         Address Match Interrupt Control Register         DMAC         66         0.048h         DMAD Interrupt Control Register         DMAC         66           0007bh         Control Register         WDTS         80         0.048h         DMAD Interrupt Control Register         DMAC         66           0007bh         Matchong Time Start Register         WDTS         80         0.055h         UART2 Taxamit Interrupt Control Register         S2/TC         66           0017bh         Address Match Interrupt Register 1         RMADD         78         0.055h         UART2 Taxamit Interrupt Control Register         S2/TC         66           0017bh         Address Match Interrupt Register 1         RMADD         78         0.055h         UART3 Taxamit Interrupt Control Register         S1/TC         66           0017bh         Address Match Interrupt Register         S1/RC         66         0.055h         UART3 Taxamit Interrupt Control Register         TAILC         66         0.055                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0006h   | System Clock Control Register 0         | CM0             | 47     | 0046h   | UART1 BUS Collision Detection Interrupt Control Register | U1BCNIC | 66       |

| Address Match Iterrupt Enable Register         AIER         76         004.         Privat Register         NT-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0007h   | System Clock Control Register 1         | CM1             | 48     | 0047h   | UART0 BUS Collision Detection Interrupt Control Register | U0BCNIC | 66       |

| DOUGH         Protect Register         PRCR         600           0000B         0004A         UAN1 Timery Control Register         DMIC 6         60           0000Ch         0004A         UAN1 Timery Control Register         DMIC 6         60           0004B         Viewhong Timer Sent Register         WDIT 6         60         004B         MAI Timery Control Register         DMIC 6         60           0004B         Viewhong Timer Sent Register         WDIT 6         60         004B         MAI Timery Control Register         AUG 6         60           0004B         Address Match Interrupt Register 0         RMAD 0         78         004B         AUG 7 Timer An Interrupt Control Register         SVIIC 66         0055         004B         AUG 7 Timer An Interrupt Control Register         SVIIC 66         0055         0055         UART Timerant Register         TAIC 66         0055         0055         UART Timerant Register         TAIC 66         0055         0056         Timer PD Interrupt Control Register <t< td=""><td>0008h</td><td>Chip Select Control Register</td><td>CSR</td><td>35</td><td>0048h</td><td></td><td></td><td></td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0008h   | Chip Select Control Register            | CSR             | 35     | 0048h   |                                                          |         |          |

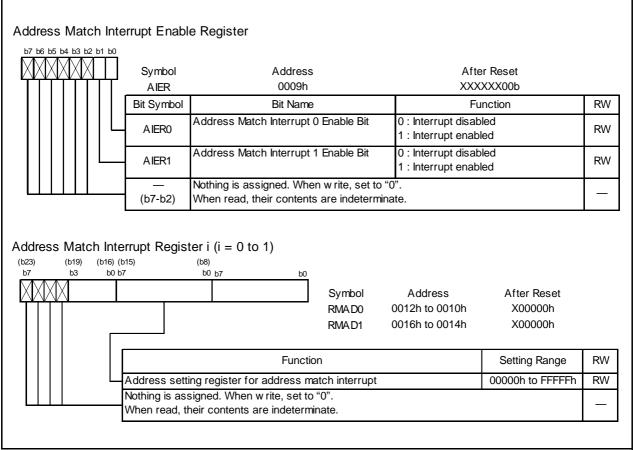

| Docken         Dock         Dock         Dock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0009h   | Address Match Interrupt Enable Register | AIER            | 78     | 0049h   | INT4 Interrupt Control Register                          | INT4IC  | 67       |

| 000Ch         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>000Ah</td> <td>Protect Register</td> <td>PRCR</td> <td>60</td> <td>004Ah</td> <td>UART2 Bus Collision Detection Interrupt Control Register</td> <td>BCNIC</td> <td>66</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 000Ah   | Protect Register                        | PRCR            | 60     | 004Ah   | UART2 Bus Collision Detection Interrupt Control Register | BCNIC   | 66       |

| DODD         Levince Itterrug Control Register         KUPIC         66           DODE         Watchdog Timer Staft Register         WDTS         90         044h         ADIC conversion Register         ADIC         66           DODE         Watchdog Timer Staft Register         WDTS         80         044h         ADIC conversion Register         ADIC         66           DODE         Watchdog Timer Staft Register         WDTS         80         044h         ADIC conversion Register         ADIC         66           DOTA         JART2 Receive Huergy Control Register         SCRUC         66         0055h         JART2 Receive Huergy Control Register         TAILC         66         0055h         Timer A1 Interrupt Control Register         TAILC         66         0055h         Timer A1 Interrupt Control Register         TAILC         66         0055h         JART2 Receive Huergy Control Register         TAILC         66         0055h         JART2 Receive Huergy Control Register         TAILC         66         0055h         JART2 Receive Huergy Control Register         TAILC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 000Bh   |                                         |                 |        | 004Bh   | DMA0 Interrupt Control Register                          | DM0IC   | 66       |

| Watch dag Timer Sunt Register         WDC         80           0004Fh         Watch dag Timer Sunt Register         ADIC         60           0010h         Address Match Interrupt Register 0         RMADD         78           0011h         Address Match Interrupt Register 0         RMADD         78           0015h         Address Match Interrupt Register 0         RMADD         78           0015h         Address Match Interrupt Register 1         RMADD         78           0015h         Componence Control Register         TAIC         60           0015h         Componence Control R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 000Ch   |                                         |                 |        | 004Ch   | DMA1 Interrupt Control Register                          | DM1IC   | 66       |

| OperFin         Watch dag Timer Control Register         WDC         28.80         OperFin         OperFin         Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 000Dh   |                                         |                 |        | 004Dh   | Key Input Interrupt Control Register                     | KUPIC   | 66       |

| 0010h         Address Match Interrup Register 0         RMAD0         78           0020h         UART2 Receive Interrup Cortex Register         S2RIC         68           0021h         Address Match Interrup Register 0         S2RIC         68           0023h         C         60         UART2 Receive Interrup Cortex Register         S0RIC         66           0025h         UART2 Receive Interrup Cortex Register         S1RIC         68           0025h         UART2 Receive Interrup Cortex Register         S1RIC         68           0025h         UART2 Receive Interrup Cortex Register         TAGC         60           0025h         UART2 Receive Interrup Cortex Register         TAGC         60           0025h         UART2 Receive Interrup Cortex Register         TAGC         60           005h         UART2 Receive Interrup Cortex Register         TAGC         60           005h         UART2 Receive Interrup Cortex Register         TAGC         60           005h         Timer A1 Interrup Cortex Register         TAGC         60           005h         Timer A1 Interrup Cortex Register         TEGC         66           005h         Timer B1 Interrup Control Register         TEGC         66           005h         NT Interrup Control Regis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 000Eh   | Watchdog Timer Start Register           | WDTS            | 80     | 004Eh   | A/D Conversion Interrupt Control Register                | ADIC    | 66       |

| 0011h         0051h         UARTO Transmit Interrupt Control Register         SUTC         66           0051h         Address Match Interrupt Register 1         RMAD1         78         0051h         UARTO Transmit Interrupt Control Register         STTC         60           0051h         Address Match Interrupt Register 1         RMAD1         78         0051h         UARTO Transmit Interrupt Control Register         STTC         60           0051h         UARTO Transmit Interrupt Control Register         TAUC         66         0055h         Timer AD Interrupt Control Register         TAUC         66           0051h         Immer AD Interrupt Control Register         TAUC         66         0055h         Timer AD Interrupt Control Register         TAUC         66           0051h         Immer AD Interrupt Control Register         TAUC         66         0055h         Timer AD Interrupt Control Register         TAUC         66           0051h         Timer BD Interrupt Control Register         TBUC         66         0055h         Timer BD Interrupt Control Register         TBUC         67           0051h         Timer BD Interrupt Control Register         TBUC         67         0056h         Timer BD Interrupt Control Register         TBUC         67           0052h         Timer BD Interrupt Control Regi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 000Fh   | Watchdog Timer Control Register         | WDC             | 28, 80 | 004Fh   | UART2 Transmit Interrupt Control Register                | S2TIC   | 66       |

| 0012h         002h         0.04RT0         680H0         690H0         690H0 <t< td=""><td>0010h</td><td>Address Match Interrupt Register 0</td><td>RMAD0</td><td>78</td><td>0050h</td><td>UART2 Receive Interrupt Control Register</td><td>S2RIC</td><td>66</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0010h   | Address Match Interrupt Register 0      | RMAD0           | 78     | 0050h   | UART2 Receive Interrupt Control Register                 | S2RIC   | 66       |

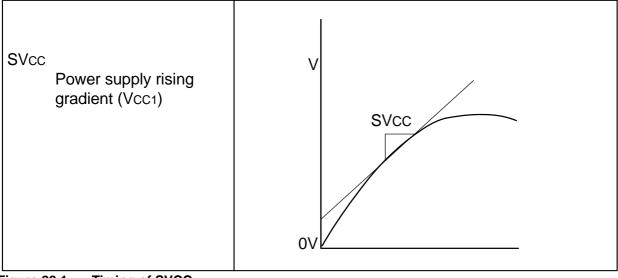

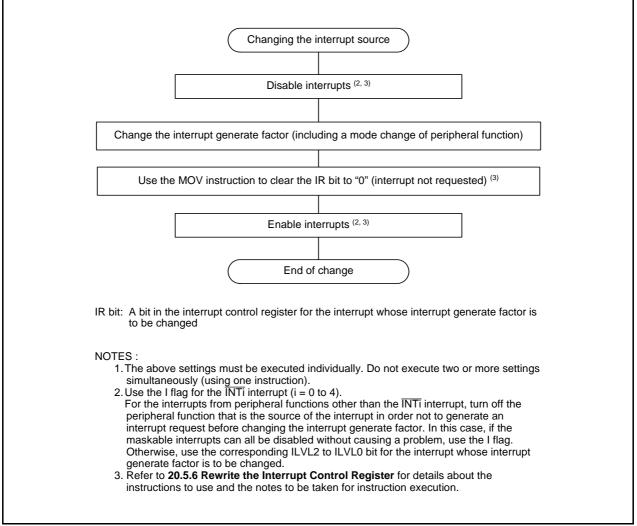

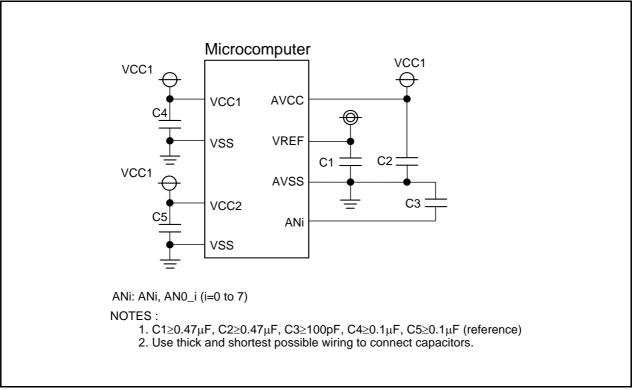

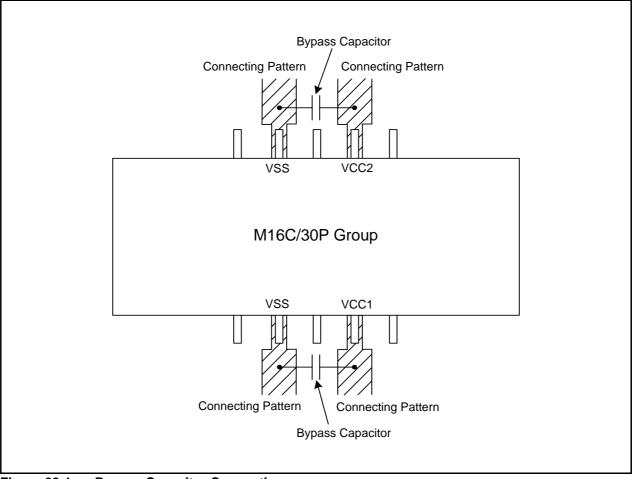

| 0013h         Address Match Interrupt Register 1         RMAD1         78           0014h         Address Match Interrupt Register 1         RMAD1         78           0015h         Address Match Interrupt Register 1         FNIC         66           0016h         Immer Al Interrupt Control Register         TAIC         66           0017h         Immer Al Interrupt Control Register         TAIC         66           0058h         Timer Al Interrupt Control Register         TAIC         66           0058h         Timer Al Interrupt Control Register         TAIC         66           0058h         Timer Al Interrupt Control Register         TBIC         66           0058h         Timer Bl Interrupt Control Register         TDIC         67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0011h   |                                         |                 |        | 0051h   | UART0 Transmit Interrupt Control Register                | SOTIC   | 66       |