# TC70/71

# $\begin{array}{l} \textbf{MICROMASTER}^{\intercal M} - \textbf{SYSTEM SUPERVISOR WITH POWER SUPPLY} \\ \textbf{MONITOR, WATCHDOG AND BATTERY BACKUP} \end{array}$

## FEATURES

- Maximum Functional Integration: Precision Power Supply Monitor, Watchdog Timer, External RESET Override, Threshold Detector and Battery Backup Controller in an 8-Pin Package

- Generates Power-on RESET and Guards Against Unstable Processor Operation Resulting from Power "Brown-out"

- Automatically Halts and Restarts an Out-of-Control Microprocessor

- Output Can be Wire-ORed, or Hooked to Manual RESET Pushbutton Switch

- Watchdog Disable Pin for Easier Prototyping (TC70)

- Voltage Monitor for Power Fail or Low Battery Warning (TC71)

- Available in 8-Pin Plastic DIP or 8-Pin SOIC Packages

- Cost Effective

## **TYPICAL APPLICATIONS**

- All Microprocessor-based Systems

- Test Equipment

- Instrumentation

- Set-Top Boxes

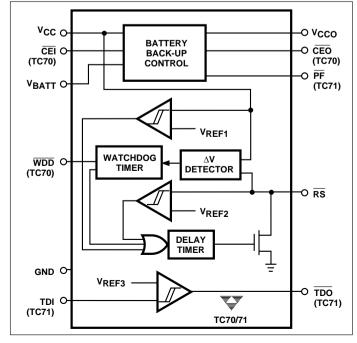

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The TC70/71 is a fully-integrated power supply monitor, watchdog and battery backup circuit in a space-saving 8-pin package.

When power is initially applied, the TC70/71 holds the processor in its reset state for a minimum of 500msec after  $V_{CC}$  is in tolerance to ensure stable system start-up. After start-up, processor sanity is monitored by the on-board watchdog circuit. The processor must provide periodic high-to-low level transitions to the TC70/71 to verify proper execution. Should the processor fail to supply this signal within the specified timeout period, an out-of-control processor is indicated and the TC70/71 issues a momentary processor reset as a result. The TC70 also features a watchdog disable pin to facilitate system test and debug.

The output of the TC70/71 can be wire-ORed to a pushbutton switch (or electronic signal) to reset the processor. When connected to a push-button switch, the TC70/71 provides contact debounce.

The integrated battery backup circuit on-board the TC70/ 71 converts CMOS RAM into nonvolatile memory by first write-protecting, then switching the  $V_{CC}$  line of the RAM over to an external battery.

The TC71 incorporates an additional 1.3V threshold detector for power fail warning, low battery detection or to monitor power supply voltages other than +5V.

## **ORDERING INFORMATION**

| Part No. | Package           | Temp. Range     |

|----------|-------------------|-----------------|

| TC70COA  | 8-Pin SOIC        | 0°C to +70°C    |

| TC70CPA  | 8-Pin Plastic DIP | 0°C to +70°C    |

| TC70EOA  | 8-Pin SOIC        | - 40°C to +85°C |

| TC70EPA  | 8-Pin Plastic DIP | - 40°C to +85°C |

| TC71COA  | 8-Pin SOIC        | 0°C to +70°C    |

| TC71CPA  | 8-Pin Plastic DIP | 0°C to +70°C    |

| TC71EOA  | 8-Pin SOIC        | - 40°C to +85°C |

| TC71EPA  | 8-Pin Plastic DIP | – 40°C to +85°C |

|          |                   |                 |

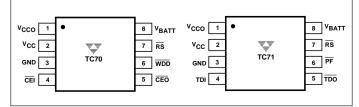

#### PIN CONFIGURATIONS (DIP and SOIC)

# TC70/71

## **ABSOLUTE MAXIMUM RATINGS\***

Voltage (Any Pin) with Respect to

Ground ...... GND – 0.3 to  $V_{CC}$  + 0.3V Operating Temperature Range ...... – 40°C to +85°C

ELECTRICAL CHARACTERISTICS:

\*This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to Absolute Maximum Rating Conditions for extended periods may affect device reliability.

#### **Recommended DC Operations**: $T_A = T_{MIN}$ to $T_{MAX}$ , unless otherwise specified.

| Symbol          | Parameter        | Test Conditions       | Min | Тур | Max | Unit |

|-----------------|------------------|-----------------------|-----|-----|-----|------|

| V <sub>CC</sub> | Supply Voltage   | Note 1                | 4.5 | 5.0 | 5.5 | V    |

| VIH             | Input HIGH Level | CEI, WDD (Note 1)     | 2.5 | _   | _   | V    |

| V <sub>IH</sub> | Input HIGH Level | RS (Note 1)           | 2.2 | _   | _   | V    |

| V <sub>IL</sub> | Input LOW Level  | CEI, WDD, RS (Note 1) |     |     | 0.8 | V    |

## **ELECTRICAL CHARACTERISTICS:**

**DC**:  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = 4.5V$  to 5.5V, unless otherwise specified.

| Symbol            | Parameter                                                                               | Test Conditions                                          | Min   | Min Typ |      | Unit |  |

|-------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------|-------|---------|------|------|--|

| I <sub>CC1</sub>  | Operating Current                                                                       | Notes 2, 3                                               | _     | 5       | 6.5  | mA   |  |

| I <sub>CC2</sub>  | Operating Current in $V_{CC} = 0$ ; $V_{BATT} = 2.8V$ ; (Note 3)<br>Battery Backup Mode |                                                          | _     | 0.01    | 0.20 | μΑ   |  |

| I <sub>IH</sub>   | Input Leakage                                                                           | CEI                                                      | _     | 4       | 7    | μΑ   |  |

| IIL               | Input Leakage                                                                           | CEI                                                      | _     | 1       | _    | μΑ   |  |

| IIH               | Input Leakage                                                                           | RS                                                       | _     | 1       | —    | μΑ   |  |

| I <sub>STBY</sub> | Battery Standby Current                                                                 | $5.5V > V_{CC} > V_{BATT} + 0.2V$                        | - 1.0 | —       | 0.02 | μΑ   |  |

| I <sub>STBY</sub> | Battery Standby Current                                                                 | $5.5V > V_{CC} > V_{BATT} + 0.2V$<br>$T_A = 25^{\circ}C$ | - 0.1 | _       | 0.02 | μΑ   |  |

# **ELECTRICAL CHARACTERISTICS:**

DC: Power Supply Monitor, EXT. RESET and Watchdog: T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>CC</sub> = 4.5V to 5.5V, unless otherwise specified.

| Symbol              | Parameter                                            | Test Conditions                                                                          | Min                   | Тур | Max                   | Unit |

|---------------------|------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| I <sub>OL</sub>     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                                                                          | 2                     | 5   | —                     | mA   |

| I <sub>OH</sub>     | Output Current 2.4V<br>(TDO, CEO, PF Pins)           | V <sub>OH</sub> = 2.4V                                                                   | 2                     | 3   |                       | mA   |

| WDDI                | WDD Input Current                                    | WDD = GND<br>$WDD = V_{CC}$                                                              | - 120<br>             | _   | <br>25                | μA   |

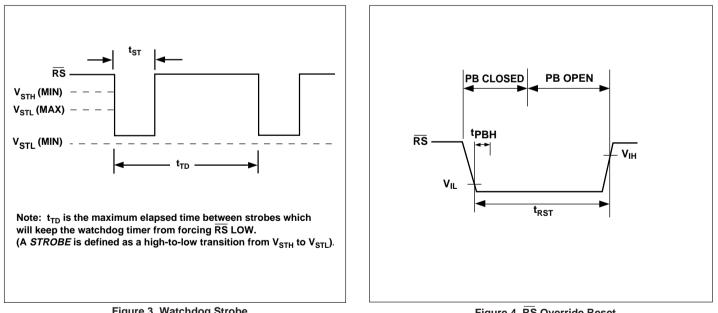

| V <sub>STH</sub>    | RS Strobe (HIGH) Level                               | Figure 3 (Note 1)                                                                        | V <sub>DD</sub> – 0.5 |     | —                     | V    |

| V <sub>STL</sub>    | RS Strobe (LOW) Level                                | Figure 3 (Note 1)                                                                        | 2.2                   |     | V <sub>DD</sub> – 1.8 | V    |

| V <sub>CCTRIP</sub> | V <sub>CC</sub> Trip Point                           | (Note 1) $0^{\circ}C \le T_A \le 70^{\circ}C$<br>- $40^{\circ}C \le T_A \le 85^{\circ}C$ | 4.25<br>4.20          | —   | 4.49<br>4.49          |      |

# **ELECTRICAL CHARACTERISTICS:**

**DC:** Battery Backup and Threshold Detector: T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>CC</sub> = 4.5V to 5.5V, unless otherwise specified.

| Symbol            | Parameter                               | Test Conditions                                                                  | Min                     | Тур               | Max | Unit |

|-------------------|-----------------------------------------|----------------------------------------------------------------------------------|-------------------------|-------------------|-----|------|

| V <sub>OUT1</sub> | V <sub>CCO</sub> Output Voltage         | I <sub>OUT</sub> = 1mA                                                           | $V_{CC} - 0.3$          |                   | —   | V    |

|                   |                                         | I <sub>OUT</sub> = 50mA                                                          | V <sub>CC</sub> – 0.5   | $V_{CC} - 0.20$   | —   |      |

| V <sub>OUT2</sub> | V <sub>OUT</sub> in Battery Backup Mode | $I_{OUT} = 250 \mu \text{A},  V_{CC} < V_{BATT} - 0.2,  V_{BATT} = 2.8 \text{V}$ | V <sub>BATT</sub> – 0.1 | $V_{BATT} - 0.02$ | —   | V    |

# MICROMASTER™ – SYSTEM SUPERVISOR WITH POWER SUPPLY MONITOR, WATCHDOG AND BATTERY BACKUP

# **TC70/71**

#### ELECTRICAL CHARACTERISTICS: (Cont.)

**DC:** Battery Backup and Threshold Detector:  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = 4.5V$  to 5.5V, unless otherwise specified.

| Symbol                  | Parameter                                                                                                           | Test Conditions                                  | Min                     | Тур                      | Max | Unit |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-------------------------|--------------------------|-----|------|

| IOUT1                   | V <sub>CCO</sub> Output Current                                                                                     | $V_{CC} = 4.5V, V_{CCO} = 3.5V$                  | 50                      | 100                      | _   | mA   |

| I <sub>OUT2</sub>       | V <sub>CCO</sub> Output Current in<br>Battery Backup Mode                                                           | $V_{CCO} = V_{BATT} - 0.3V$<br>$V_{BATT} = 2.8V$ | 500                     |                          |     | μA   |

| V <sub>SW</sub>         | Battery Switchover Threshold (V <sub>CC</sub> Falling)                                                              |                                                  | —                       | V <sub>BATT</sub> – 0.01 | _   | V    |

| V <sub>HYST</sub>       | Battery Switchover Hysteresis                                                                                       |                                                  |                         | 20                       | —   | mV   |

| VOHCEO                  | $\overline{CEO}$ Output Voltage in $V_{CC} < V_{BATT} - 0.2, V_{BATT} = 2.8$ Battery Backup Mode $I_{OH} = 10\mu A$ |                                                  | V <sub>BATT</sub> – 0.2 |                          |     | V    |

| V <sub>TDI</sub>        | Threshold Detector Trip Voltage                                                                                     |                                                  | 1.2                     | _                        | 1.4 | V    |

| I <sub>TDI</sub>        | Threshold Detector Input Current $T_A = 25^{\circ}C$                                                                |                                                  | -25                     | _                        | +25 | nA   |

| V <sub>TDI (HYST)</sub> | Threshold Detector Hysteresis                                                                                       |                                                  |                         | 10                       |     | mV   |

#### **ELECTRICAL CHARACTERISTICS:**

AC: Power Supply Monitor, EXT. RESET and Watchdog: T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>CC</sub> = 4.5V to 5.5V, unless otherwise specified.

| Symbol           | Parameter                        | Test Conditions   | Min | Тур | Max | Unit |

|------------------|----------------------------------|-------------------|-----|-----|-----|------|

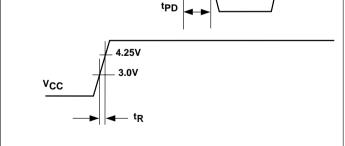

| t <sub>PBH</sub> | PB Hold Time                     | Figure 4 (Note 4) | 20  |     |     | msec |

| t <sub>RST</sub> | Reset Active Time                | Figure 6          | 500 | _   | 900 | msec |

| t <sub>ST</sub>  | RS STROBE Pulsewidth Figure 3    |                   | 500 |     |     | nsec |

| t <sub>TD</sub>  | Watchdog Timeout Period          | Figure 3          | 500 | 700 | 900 | msec |

| t <sub>RPD</sub> | V <sub>CC</sub> Detect to RS LOW | Figure 6          |     |     | 100 | nsec |

## **ELECTRICAL CHARACTERISTICS:**

AC: Battery Backup and Threshold Detector: T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, V<sub>CC</sub> = 4.5V to 5.5V, unless otherwise specified.

| Symbol          | Parameter              | Test Conditions | Min | Тур | Max | Unit |

|-----------------|------------------------|-----------------|-----|-----|-----|------|

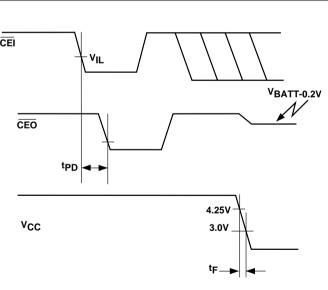

| t <sub>PD</sub> | CE Propagational Delay | Figure 7        | —   | —   | 50  | nsec |

# **ELECTRICAL CHARACTERISTICS:**

**AC**:  $T_A = T_{MIN}$  to  $T_{MAX}$ .

| Symbol         | Parameter                                       | Test Conditions   | Min | Тур | Max | Unit |

|----------------|-------------------------------------------------|-------------------|-----|-----|-----|------|

| t <sub>F</sub> | V <sub>CC</sub> Fall Time From<br>4.25V to 3.0V | Figure 5 (Note 1) | 10  |     | _   | µsec |

| t <sub>R</sub> | V <sub>CC</sub> Rise Time From 3.0V to 4.25V    | Figure 5 (Note 1) | 0   | —   | —   | μsec |

NOTES: 1. All voltages referenced to ground.

2. No output load.

Measured with V<sub>CCO</sub> and CEO open.

The RS output must be held low for a minimum of 20msec to guarantee a reset.

# MICROMASTER<sup>™</sup> – SYSTEM SUPERVISOR WITH POWER SUPPLY MONITOR, WATCHDOG AND BATTERY BACKUP

# TC70 TC71

#### **PIN DESCRIPTION**

| Pin No<br>(TC70) | Pin No<br>(TC71) | Symbol            | Description                                                                                                                                                                                                                                                                                                                              |

|------------------|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | 1                | Vcco              | $V_{CC}$ Output. The higher of $V_{CC}$ or $V_{BATT}$ is internally switched to this output. Connect to $V_{CC}$ if $V_{BATT}$ and $V_{CCO}$ are not used.                                                                                                                                                                               |

| 2                | 2                | Vcc               | V <sub>CC</sub> Input. +5V power supply.                                                                                                                                                                                                                                                                                                 |

| 3                | 3                | GND               | GND Input. Ground.                                                                                                                                                                                                                                                                                                                       |

| 4                | _                | CEI               | Chip enable input. Chip enable to static RAM or other device to be battery backed-up. Connect to ground if $V_{CCO}$ is not used.                                                                                                                                                                                                        |

| -                | 4                | TDI               | Threshold detector input. When the voltage on threshold detector input (TDI) is less than 1.3V, threshold detector output (TDO) goes low.                                                                                                                                                                                                |

| 5                | _                | CEO               | Chip enable output. This line goes low only when $\overline{\text{CEI}}$ is low and $V_{\text{CC}}$ is above the RESET threshold.                                                                                                                                                                                                        |

| -                | 5                | TDO               | Threshold detector output. TDO goes low when TDI is less than 1.3V and V <sub>CC</sub> is greater than V <sub>BATT</sub> . (The threshold detector is turned off when V <sub>CC</sub> is less than V <sub>BATT</sub> .                                                                                                                   |

| 6                | _                | WDD               | Watchdog disable input. Grounding this line disables the watchdog timer (no RESET pulses are generated after the watchdog timer times out). This input is provided to facilitate system debug. This input is internally pulled-up and can be left open, or tied to $V_{CC}$ for normal watchdog operation.                               |

| -                | 6                | PF                | Power fail output. This line goes low when V <sub>CC</sub> is below 4.5V nominal. It is used to write-protect the external device to be battery backed.                                                                                                                                                                                  |

| 7                | 7                | RS                | <ul> <li>RESET/STORE (Bidirectional). An open drain with pull-up (in output mode) that goes active if:</li> <li>1. V<sub>CC</sub> falls below 4.5V nominal</li> <li>2. If pulled low by an external electronic signal or switch closure</li> <li>3. If the watchdog is not strobed within the minimum watchdog timeout period</li> </ul> |

|                  |                  |                   | 4. During power-up and power down<br>In the input mode, $\overline{\text{RS}}$ is a negative edge triggered input that resets the<br>watchdog timer when pulled to ground through a 10k $\Omega$ , 5% tolerance resistor.                                                                                                                |

| 8                | 8                | V <sub>BATT</sub> | Backup battery input. Connect to ground if battery backup is not used.                                                                                                                                                                                                                                                                   |

## **DETAILED DESCRIPTION**

#### **Precision Power Supply Monitor**

The  $\overline{\text{RS}}$  pin is immediately driven low any time V<sub>CC</sub> is below 4.5V nominal. The processor is held in its reset state during power-up and power-down.  $\overline{\text{RS}}$  remains low for a minimum of 500msec after V<sub>CC</sub> is within tolerance to allow the power supply and processor to stabilize.

#### Watchdog Timer

The processor drives the  $\overline{\text{RS}}$  pin with an input/output (I/O) line in series with a voltage divider to V<sub>DD</sub>. Pulling the bottom of this divider low results in an internal voltage change (strobe) sufficient to reset the watchdog timer, but above the V<sub>IL</sub> input threshold of the processor  $\overline{\text{RESET}}$  input. The processor must continuously apply strobes in this manner within a set period to verify proper software execution. A momentary reset (500msec minimum) is generated if a hardware or software failure keeps  $\overline{\text{RS}}$  from being

strobed within the watchdog timeout period. This action typically initiates the processor's power-up routine. If the interruption persists, new reset pulses are generated each timeout period until  $\overline{\text{RS}}$  is strobed. The timeout period is typically 700msec.

It is often difficult to debug a system while the watchdog is continuously generating reset pulses. For example, the watchdog must be disabled when the system is operated with an in-circuit emulator (ICE). The watchdog disable input (TC70) is provided for system debugging, (or if the watchdog timer on-board the processor is to be used). Grounding WDD disables the watchdog (all other functions remain intact). For normal watchdog operation, WDD can be tied to  $V_{DD}$ .

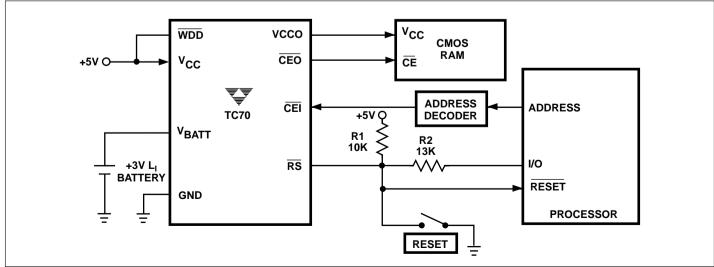

The software routine that drives the RS strobe must be in a section of the program that executes frequently enough so the time between toggles is less than one watchdog timeout period. The strobe signal can be derived from microprocessor address, data and/or control signals. Typical circuit examples are shown in Figure 1.

#### **Resistor Value Selection**

The values of R1 and R2 must be chosen to ensure a valid low strobe level (V<sub>STL</sub>) on  $\overline{\text{RS}}$  when the processor I/O line is low. The use of  $10k\Omega$ ,  $\pm 5\%$  tolerance resistors are recommended. These values result in a nominal strobe level of 2.83V on  $\overline{\text{RS}}$  (min/max of 2.43V/3.24V, assuming V<sub>DD</sub> = 5.0V  $\pm 10\%$ ). Other resistor values can be used, so long as the additive tolerances of the power supply and resistor values result in a strobe that falls within V<sub>STH</sub> and V<sub>STL</sub> under all additive tolerance conditions.

#### **External Override Reset Control**

A built-in debounce circuit allows a pushbutton switch (or other electronic reset signal) to be wire-ORed to  $\overline{RS}$  as an external reset override (Figure 4). The external reset signal is required to be an active low signal of at least 20msec in duration. Internally, this input is timed to provide a minimum reset pulse width output of 500msec.

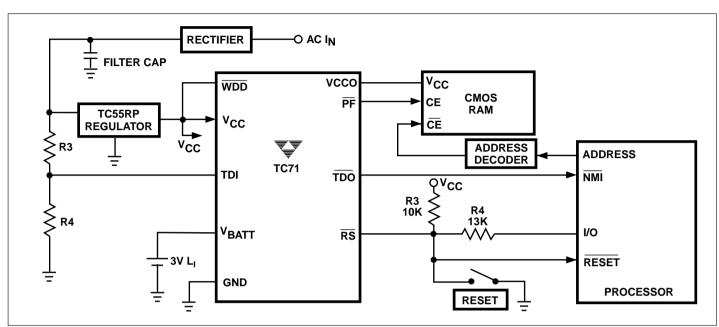

#### **Threshold Detector**

The TC71 issues a low-true output on the TDO pin any time the TDI pin is less than 1.3V and  $V_{CC}$  is greater than  $V_{BATT}$ . The voltage to be monitored is connected to the TDI input through a simple resistor divider. The threshold detector can be used to generate an early power fail warning if the unregulated DC input to the +5V regulator is available for monitoring.

#### Integrated Battery Backup (TC70)

The  $\overline{CEO}$  line (TC70) drives the  $\overline{CE}$  input of a CMOS RAM or other device to be battery-backed.  $\overline{CEO}$  follows  $\overline{CEI}$ as long as V<sub>CC</sub> is greater than 4.5V nominal. If V<sub>CC</sub> falls below 4.5V nominal,  $\overline{CEO}$  is driven to the potential of VCCO thus write protecting the RAM and preventing accidental data corruption during power up and power down. The battery switchover circuit compares V<sub>CC</sub> to the V<sub>BATT</sub> input and connects VCCO to whichever is higher. Switchover (V<sub>SW</sub>) occurs when V<sub>CC</sub> is 10mV below V<sub>BATT</sub> as V<sub>CC</sub> falls, and when V<sub>CC</sub> is 10mV more than V<sub>BATT</sub> as V<sub>CC</sub> rises. The battery switchover comparator has 20mV of hysteresis to prevent switch chattering if V<sub>CC</sub> falls very slowly.

#### **Integrated Battery Backup (TC71)**

The TC71 differs from the TC70 in that it has a Power Fail (PF) output instead of a gated chip enable (CEI, CEO). PF must be externally gated with the decode for the CMOS RAM or other device to be battery-backed. (Many CMOS RAMs have both CE and CE enables. In this case, the PF output can be connected directly to the CE input of the RAM). PF is high as long as V<sub>CC</sub> is greater than 4.5V nominal. When V<sub>CC</sub> falls below 4.5V nominal, PF is driven low. Battery switchover for the TC71 is otherwise identical to that of the TC70.

## **Supply Monitor Noise Sensitivity**

The TC70/71 is optimized for fast response to negativegoing changes in V<sub>DD</sub>. Systems with an inordinate amount of electrical noise on V<sub>DD</sub> (such as systems using relays), may require a 0.1 $\mu$ F bypass capacitor to reduce detection sensitivity. This capacitor should be installed as close to the TC70/71 as possible to keep the capacitor lead length short.

# TYPICAL APPLICATIONS

Figure 1 shows a full feature implementation of the TC70; Figure 2 shows the TC71. Resistors R1 and R2 of Figure 2 set the trip point voltage for the early power fail warning circuit using the TC71 threshold detector.

Figure 1. TC70 Typical Application

# MICROMASTER™ – SYSTEM SUPERVISOR WITH POWER SUPPLY MONITOR, WATCHDOG AND BATTERY BACKUP

Figure 2. TC71 Typical Application

Figure 3. Watchdog Strobe

Figure 4. RS Override Reset

**TC70 TC71**

# MICROMASTER<sup>™</sup> – SYSTEM SUPERVISOR WITH POWER SUPPLY MONITOR, WATCHDOG **AND BATTERY BACKUP**

tR vcc tF v<sub>cc</sub>\_ 4.25V 4.25V <sup>t</sup>RPD <sup>t</sup>RST 3.0\ RS VOH VOL Figure 5. Power Up/Down Slew Rate Figure 6. Power Up/Down Reset Timing ٧н CEI CEI ٧IL VBATT-0.2V VBATT- 0.2V CEO ۷ін CEO

Figure 7. Battery Backup (Power-Up)

TC70 TC71