EVAL-AD7687SDZ(RevC) Ver la hoja de datos (PDF) - Analog Devices

Número de pieza

componentes Descripción

Fabricante

EVAL-AD7687SDZ

(Rev.:RevC)

(Rev.:RevC)

Analog Devices

EVAL-AD7687SDZ Datasheet PDF : 28 Pages

| |||

Data Sheet

AD7687

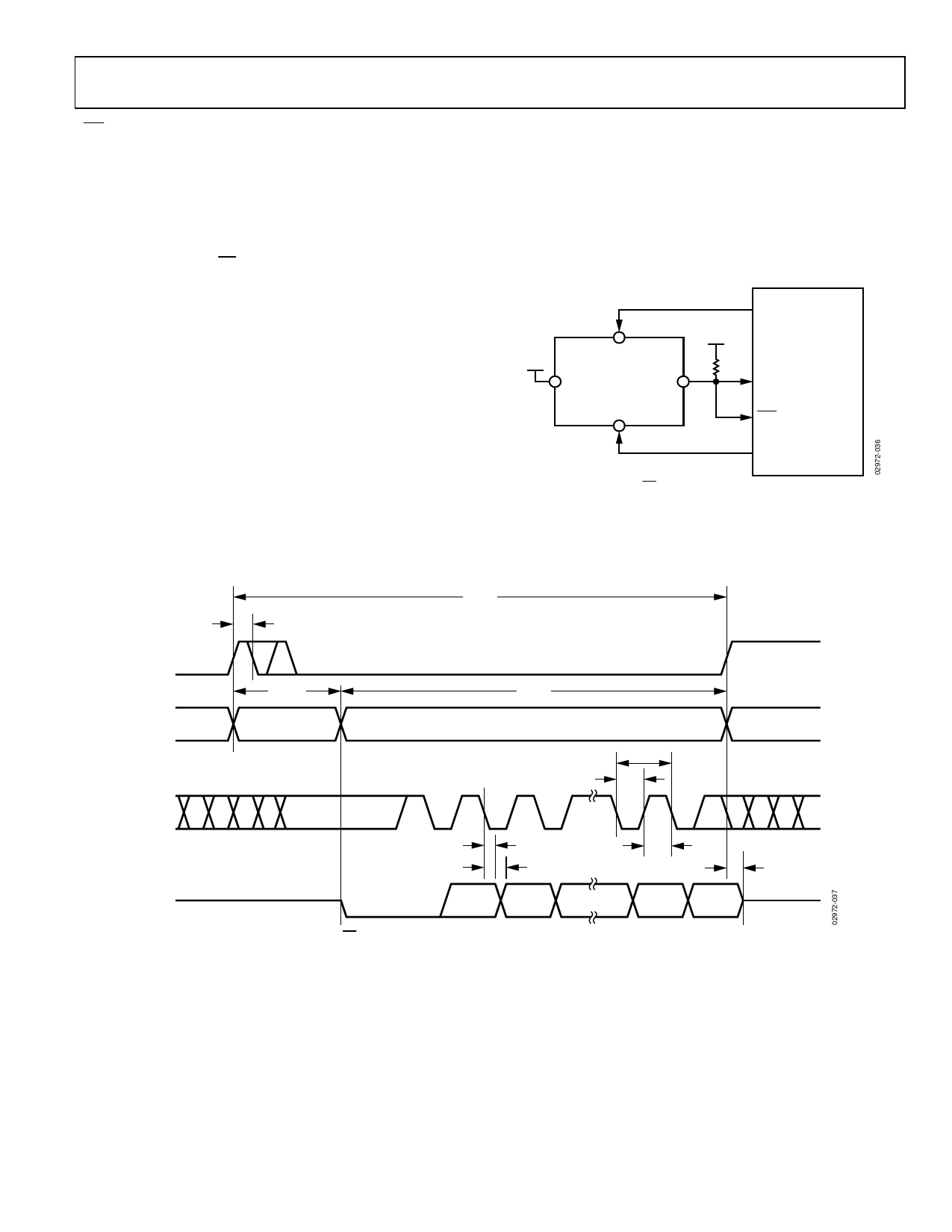

CS MODE 3-WIRE WITH BUSY INDICATOR

This mode is usually used when a single AD7687 is connected

to an SPI-compatible digital host having an interrupt input.

The connection diagram is shown in Figure 37 and the

corresponding timing is given in Figure 38.

With SDI tied to VIO, a rising edge on CNV initiates a

conversion, selects the CS mode, and forces SDO to high

impedance. SDO is maintained in high impedance until the

completion of the conversion irrespective of the state of CNV.

Prior to the minimum conversion time, CNV could be used to

select other SPI devices, such as analog multiplexers, but CNV

must be returned low before the minimum conversion time and

held low until the maximum conversion time to guarantee the

generation of the BUSY signal indicator. When the conversion

is complete, SDO goes from high impedance to low. With a

pull-up on the SDO line, this transition can be used as an

interrupt signal to initiate the data reading controlled by the

digital host. The AD7687 then enters the acquisition phase and

powers down. The data bits are then clocked out, MSB first, by

subsequent SCK falling edges. The data is valid on both SCK

edges. Although the rising edge can be used to capture the data,

a digital host using the SCK falling edge allows a faster reading

rate provided it has an acceptable hold time. After the optional

17th SCK falling edge, or when CNV goes high, whichever is

earlier, SDO returns to high impedance.

If multiple AD7687s are selected at the same time, the SDO

output pin handles this contention without damage or induced

latch-up. Meanwhile, it is recommended to keep this contention

as short as possible to limit extra power dissipation.

CNV

VIO

SDI AD7687 SDO

SCK

CONVERT

VIO

DIGITAL HOST

47kΩ

DATA IN

IRQ

CLK

Figure 37. CS Mode 3-Wire with BUSY Indicator

Connection Diagram (SDI High)

SDI = 1

tCNVH

CNV

tCONV

ACQUISITION CONVERSION

SCK

SDO

tCYC

tACQ

ACQUISITION

tSCKL

tSCK

1

2

tHSDO

tDSDO

D15

3

D14

15

16

17

tSCKH

tDIS

D1

D0

Figure 38. CS Mode 3-Wire with BUSY Indicator Serial Interface Timing (SDI High)

Rev. C | Page 19 of 28