74LV165PW,118 Ver la hoja de datos (PDF) - NXP Semiconductors.

Número de pieza

componentes Descripción

Fabricante

74LV165PW,118 Datasheet PDF : 20 Pages

| |||

Nexperia

74LV165

8-bit parallel-in/serial-out shift register

9,

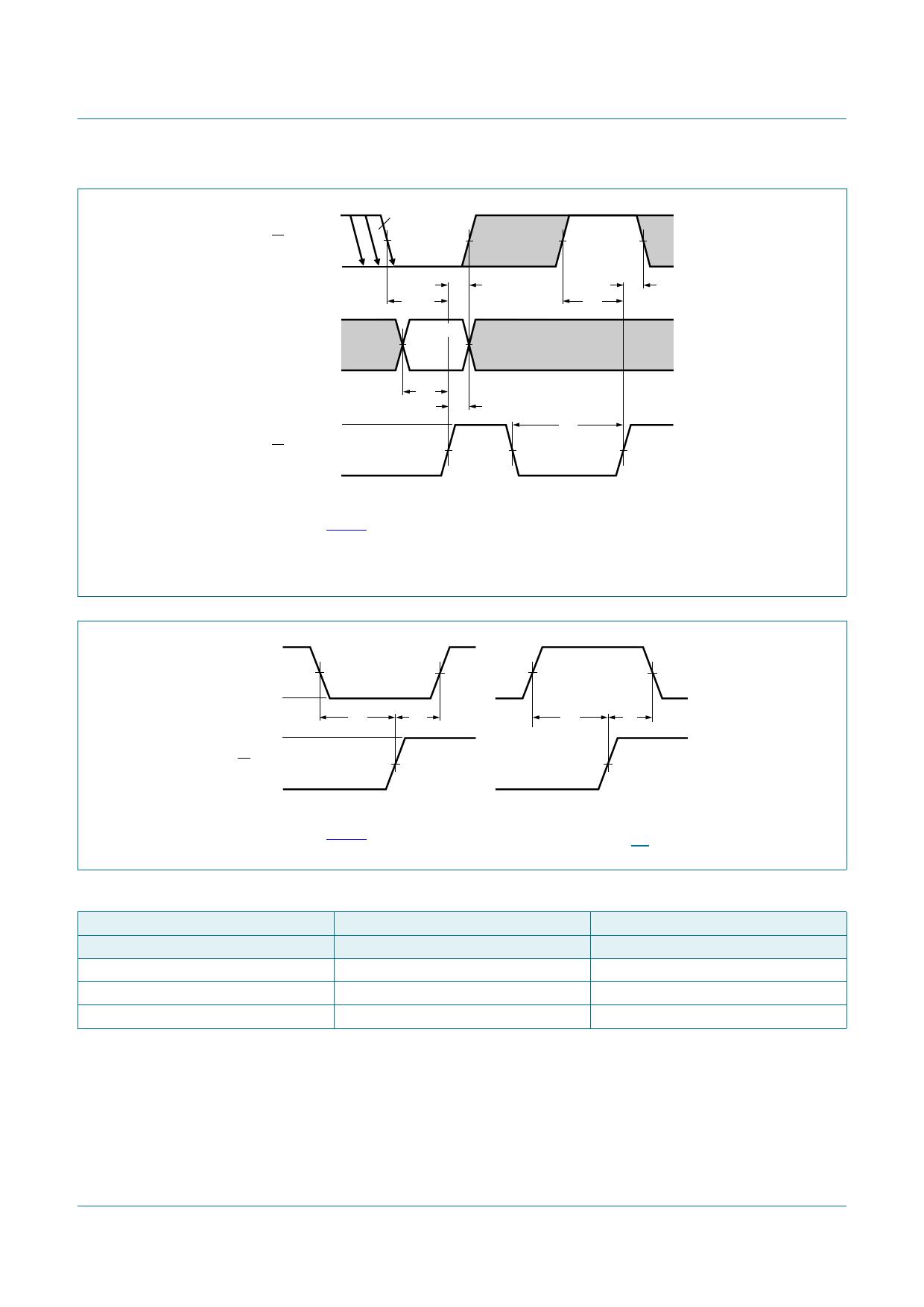

&3&(LQSXW

*1'

9,

'6LQSXW

*1'

9,

&3&(LQSXW

*1'

90

WK

WVX

/

VWDEOH

90

WVX

WK

90

WK

WVX

W:

DDD

Measurement points are given in Table 8.

(1) CE may change only from HIGH-to-LOW while CP is LOW. The shaded areas indicate when the input is permitted to change for

predictable output performance.

Fig 10. Set-up and hold times

9,

'QLQSXW

*1'

9,

3/LQSXW

*1'

90

WVX

WK

90

90

WVX

WK

90

DDD

Measurement points are given in Table 8.

Fig 11. Set-up and hold times from the data inputs (Dn) to the parallel load input (PL)

Table 8. Measurement points

Supply voltage

VCC

< 2.7 V

2.7 V to 3.6 V

4.5 V

Input

VM

0.5VCC

1.5 V

0.5VCC

Output

VM

0.5VCC

1.5 V

0.5VCC

74LV165

Product data sheet

All information provided in this document is subject to legal disclaimers.

Rev. 7 — 9 March 2016

© Nexperia B.V. 2017. All rights reserved

12 of 20