CY7C006A-20AXC Ver la hoja de datos (PDF) - Cypress Semiconductor

NГғmero de pieza

componentes DescripciГіn

Fabricante

CY7C006A-20AXC Datasheet PDF : 22 Pages

| |||

CY7C006A/CY7C007A

CY7C016A/CY7C017A

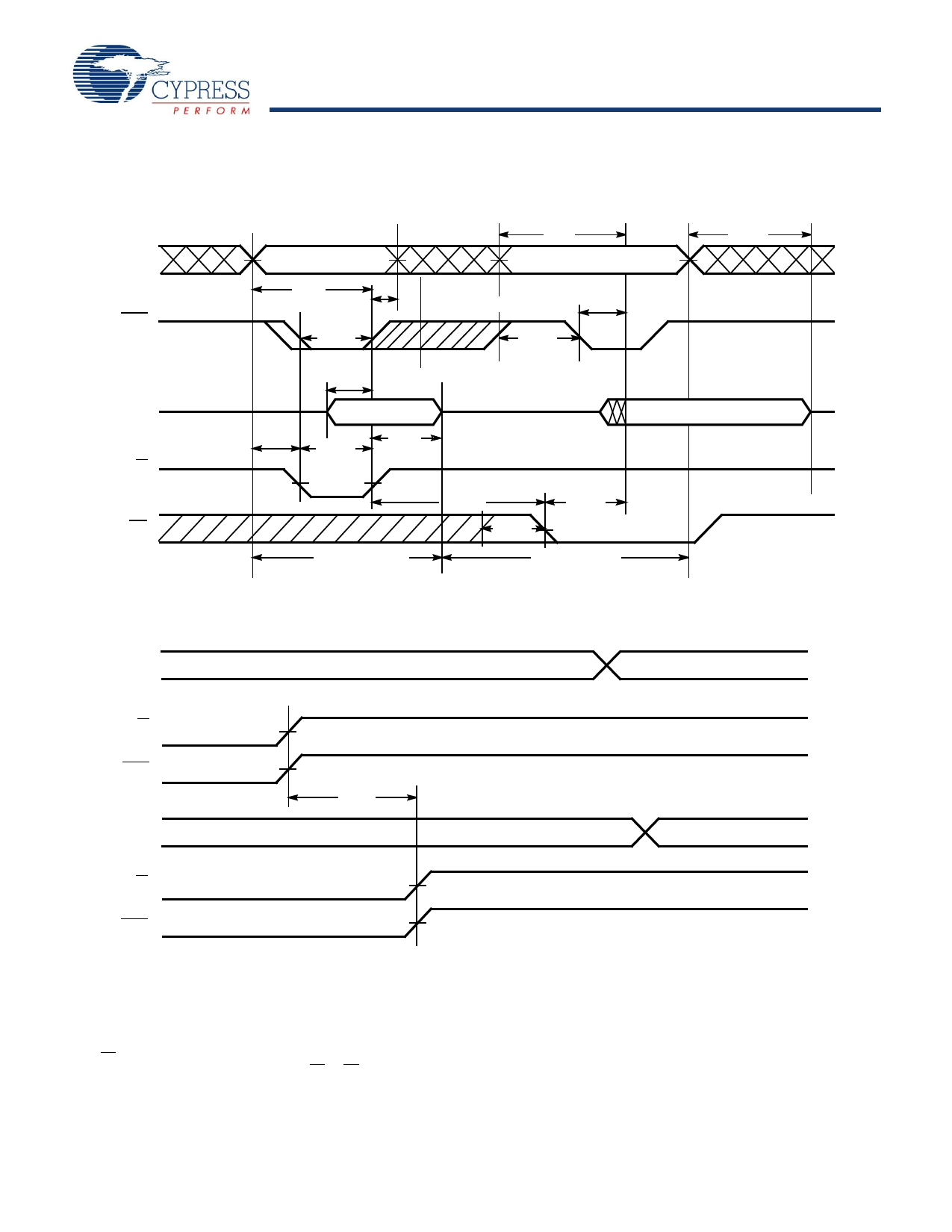

Switching Waveforms (continued)

Semaphore Read After Write Timing, Either Side[39]

A0–A 2

SEM

VALID ADRESS

tAW

tHA

tSCE

tAA

VALID ADRESS

tSOP

tACE

tOHA

I/O0

R/W

OE

tSD

DATAIN VALID

tSA

tPWE

tHD

DATAOUT VALID

WRITE CYCLE

tSWRD

tSOP

tDOE

READ CYCLE

Timing Diagram of Semaphore Contention[40, 41, 42]

A0L –A2L

MATCH

R/WL

SEM L

A 0R–A2R

R/WR

SEM R

tSPS

MATCH

Notes

39. CE = HIGH for the duration of the above timing (both write and read cycle).

40. I/O0R = I/O0L = LOW (request semaphore); CER = CEL = HIGH.

41. Semaphores are reset (available to both ports) at cycle start.

42. If tSPS is violated, the semaphore will definitely be obtained by one side or the other, but which side will get the semaphore is unpredictable.

Document Number: 38-06045 Rev. *F

Page 13 of 22

[+] Feedback