LMA2009JC45 Ver la hoja de datos (PDF) - LOGIC Devices

Número de pieza

componentes Descripción

Fabricante

LMA2009JC45 Datasheet PDF : 7 Pages

| |||

DEVICES INCORPORATED

DEVICES INCORPORATED

LMA 1009/2009

12 x 12-LbiMt MAult1ip0lie0r-A9c/c2um0u0la9tor

12 x 12-bit Multiplier-Accumulator

FEATURES

DESCRIPTION

u 20 ns Multiply-Accumulate Time

u Low Power CMOS Technology

u Replaces Fairchild TDC1009/

TMC2009

u Two’s Complement or Unsigned

Operands

u Accumulator Performs Preload,

Accumulate, and Subtract

u Three-State Outputs

u 68-pin PLCC, J-Lead

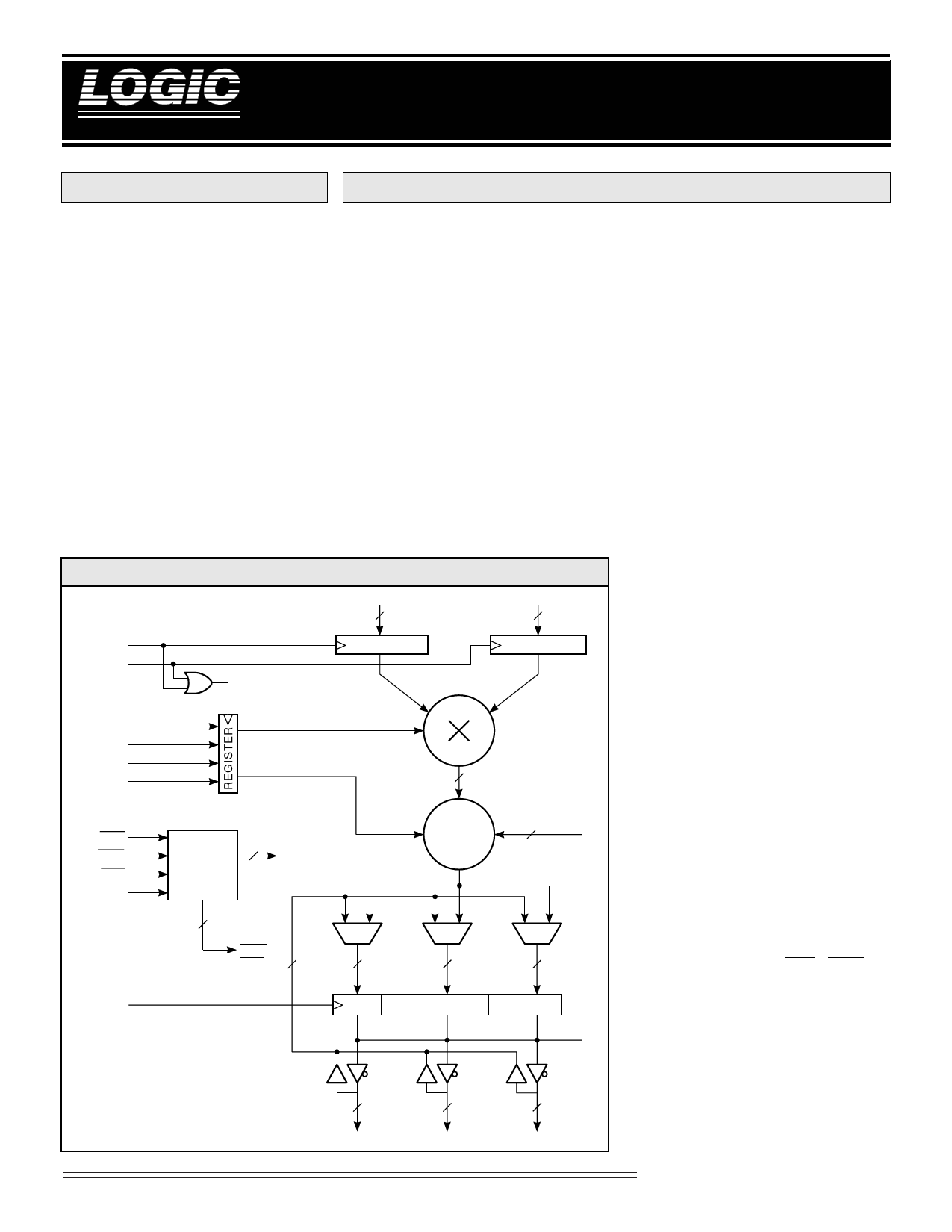

LMA1009/2009 BLOCK DIAGRAM

CLK A

CLK B

RND

TC

ACC

SUB

OEX

OEM

OEL

PREL

CLK R

PRELOAD

CONTROL 3

LOGIC

LEX

LEM

LEL

3

OEX

OEM

OEL

LEX

27

The LMA1009 and LMA2009 are high-

speed, low power 12-bit multiplier-accu-

mulators. They are pin-for-pin equiva-

lent to the TRW TDC1009/TMC2009

multiplier-accumulators. The LMA1009

and LMA2009 are functionally identical;

they differ only in packaging. Full ambi-

ent temperature range operation is

achieved by the use of advanced CMOS

technology.

The LMA1009/2009 produces the 24-bit

product of two 12-bit numbers. The

results of a series of multiplications may

be accumulated to form the sum of prod-

ucts. Accumulation is performed to

27-bit precision with the multiplier prod-

uct sign extended as appropriate.

A11-0

12

A REGISTER

B11-0

12

B REGISTER

24

R

R+A A

R–A

PASS R

27

LEM

LEL

3

12

12

ACCUMULATOR REGISTER

OEX

3

OEM

12

OEL

12

Data present at the A and B input regis-

ters is latched on the rising edges of

CLK A and CLK B respectively. RND,

TC, ACC, and SUB controls are latched

on the rising edge of the logical OR of

CLK AandCLK B. TCspecifiestheinput

as two’s complement

(TC HIGH) or unsigned magnitude

(TC LOW). RND, when HIGH, adds ‘1’

to the most significant bit position of the

least significant half of the product. Sub-

sequent truncation of the 12 least signifi-

cant bits produces a result correctly

rounded to 12-bit precision.

The ACC and SUB inputs control accu-

mulator operation. ACC HIGH results in

addition of the multiplier product and

the accumulator contents, with the result

stored in the accumulator register on the

rising edge of CLK R. ACC and SUB

HIGH results in subtraction of the accu-

mulator contents from the multiplier

product, with the result stored in the

accumulator register. With ACC LOW

and SUB LOW, no accumulation occurs

and the next product is loaded directly

into the accumulator register. ACC LOW

and SUB HIGH is undefined.

The LMA1009/2009 output register (ac-

cumulator register) is divided into three

independently controlled sections. The

least significant result (LSR) and most

significant result (MSR) registers are 12

bits in length. The extended result regis-

ter (XTR) is 3 bits long.

Each output register has an independ-

ent output enable control. In addition

to providing control of the three-state

output buffers, when OEX, OEM, or

OEL are HIGH and PREL is HIGH, data

can be preloaded via the bidirectional

output pins into the respective output

registers. Data present on the output

pins is latched on the rising edge of

CLK R. The interrelation of PREL and

the enable controls is summarized in

Table 1.

R26-24

R23-12

R11-0

Multiplier-Accumulators

1

03/29/2000–LDS.10/2009-L