M61532FP Ver la hoja de datos (PDF) - Hitachi -> Renesas Electronics

Número de pieza

componentes Descripción

Fabricante

M61532FP Datasheet PDF : 15 Pages

| |||

M61532FP

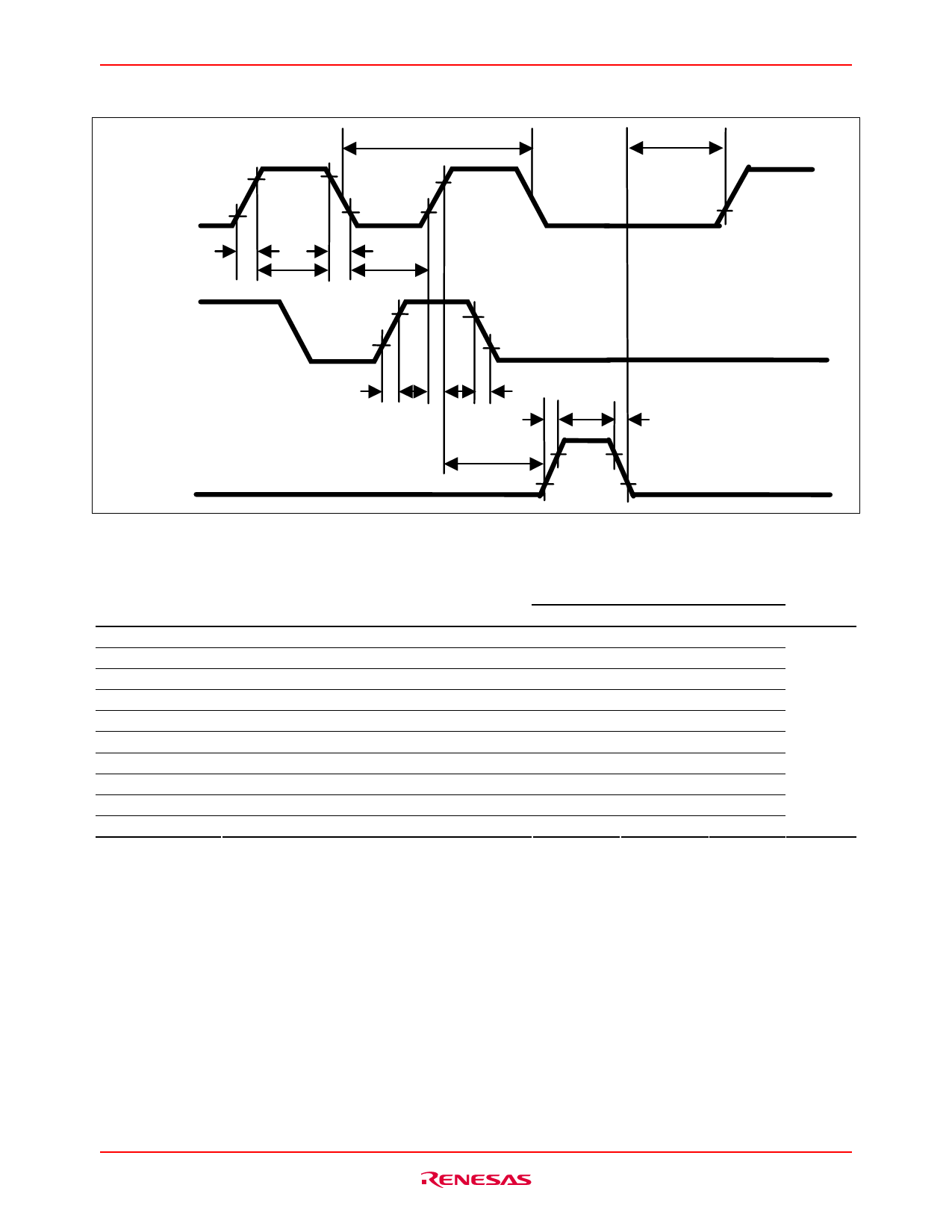

Clock and Data Timings

75%

CLOCK

25%

tr

tWHC

DATA

tcr

tf

tWLC

75%

25%

tSC

25%

LATCH

tr

tf

tSD tHD

tr

tWHC

tf

tSL

75%

25%

Timing Definition of Digital Block

Symbol

tcr

tWHC

tWLC

tr

tf

tSD

tHD

tSL

tWHL

tSC

Parameter

Clock cycle time

Clock pulse width (“H” level)

Clock pulse width (“L” level)

Rising time of clock,data and latch

Falling time of clock,data and latch

Data setup time

Data hold time

Latch setup time

Latch pulse width

Clock setup time

Limits

Min

typ

Max

Unit

4

µsec

1.6

1.6

0.4

0.4

0.8

0.8

1

1.6

4

Rev.1.0, Sep.19.2003, page 6 of 14