LP173WF4-SPF1 Ver la hoja de datos (PDF) - LG

Número de pieza

componentes Descripción

Fabricante

LP173WF4-SPF1 Datasheet PDF : 31 Pages

| |||

Product Specification

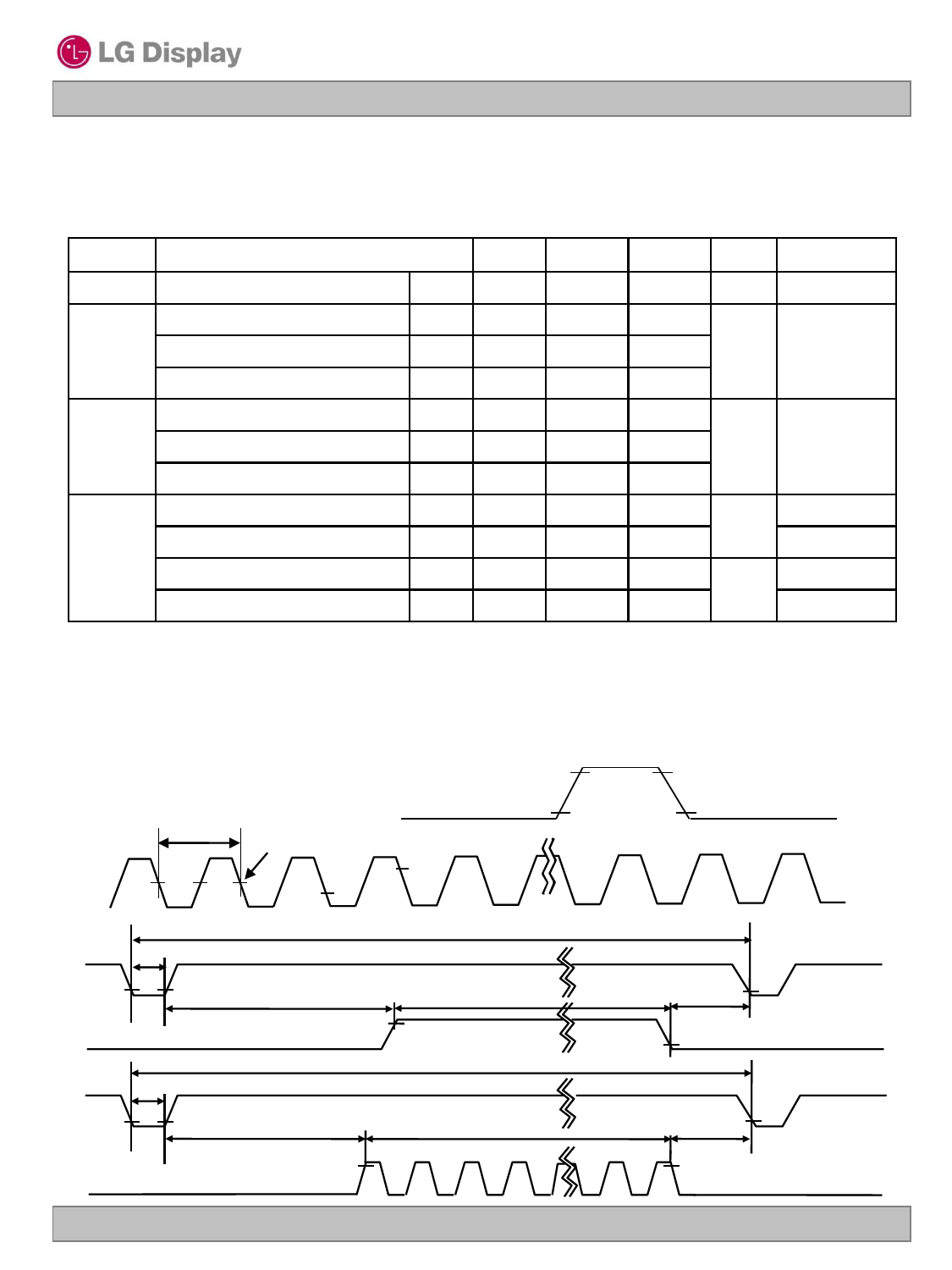

3-4. Signal Timing Specifications

LP173WF4

Liquid Crystal Display

This is the signal timing required at the input of the User connector. All of the interface signal timing should be

satisfied with the following specifications and specifications of eDP Tx/Rx for its proper operation.

Table 5. TIMING TABLE

ITEM

Symbol

Min

Typ

Max Unit

Note

DCLK

Frequency

Period

fCLK

-

Thp

-

138.7

2080

-

MHz

-

Hsync Width

tWH

-

32

-

tCLK

Width-Active

tWHA

-

1920

-

Vsync

Data

Enable

Period

Width

Width-Active

Horizontal back porch

Horizontal front porch

Vertical back porch

Vertical front porch

tVP

-

tWV

-

tWVA

-

tHBP

-

tHFP

-

tVBP

-

tVFP

-

1111

5

1080

80

48

23

3

-

-

tHP

-

-

tCLK

-

-

tHP

-

Notice. all reliabilities are specified for timing specification based on refresh rate of 60Hz. However,

LP173WF4 has a good actual performance even at lower refresh rate (e.g. 40Hz or 50Hz) for power saving

Mode, whereas LP173WF4 is secured only for function under lower refresh rate. 60Hz at Normal mode, 50Hz,

40Hz at Power save mode. Don’t care Flicker level (power save mode).

3-5. Signal Timing Waveforms

Data Enable, Hsync, Vsync

tCLK

DCLK

0.5 Vcc

High: 0.7VCC

Low: 0.3VCC

Condition : VCC =3.3V

Hsync tWH

tHBP

Data Enable

tWV

Vsync

tVBP

Data Enable

Ver. 0.0

tHP

tWHA

tVP

tWVA

Oct. 15, 2013

tHFP

tVFP

10 / 31