HT47C20L Ver la hoja de datos (PDF) - Holtek Semiconductor

Número de pieza

componentes Descripción

Fabricante

HT47C20L Datasheet PDF : 45 Pages

| |||

HT47C20L

If the wake-up results from an interrupt acknowledg-

ment, the actual interrupt subroutine execution will be

delayed by more than one cycle. However, if the

wake-up results in the next instruction execution, the ex-

ecution will be performed immediately.

To minimize power consumption, all the I/O pins should

be carefully managed before entering the halt mode.

Reset

There are three ways in which a reset may occur.

· RES reset during normal operation

· RES reset during halt mode

· WDT time-out reset during normal operation

· The LVR is enable and the VDD is lower then VLVR

The WDT time-out during halt mode is different from

other chip reset conditions, since it can perform a warm

reset that just resets the Program Counter and SP leav-

ing the other circuits in their original state. Some regis-

ters remain unchanged during other reset conditions.

Most registers are reset to the ²initial condition² when

the reset conditions are met. By examining the PDF and

TO flags, the program can distinguish between different

²chip resets².

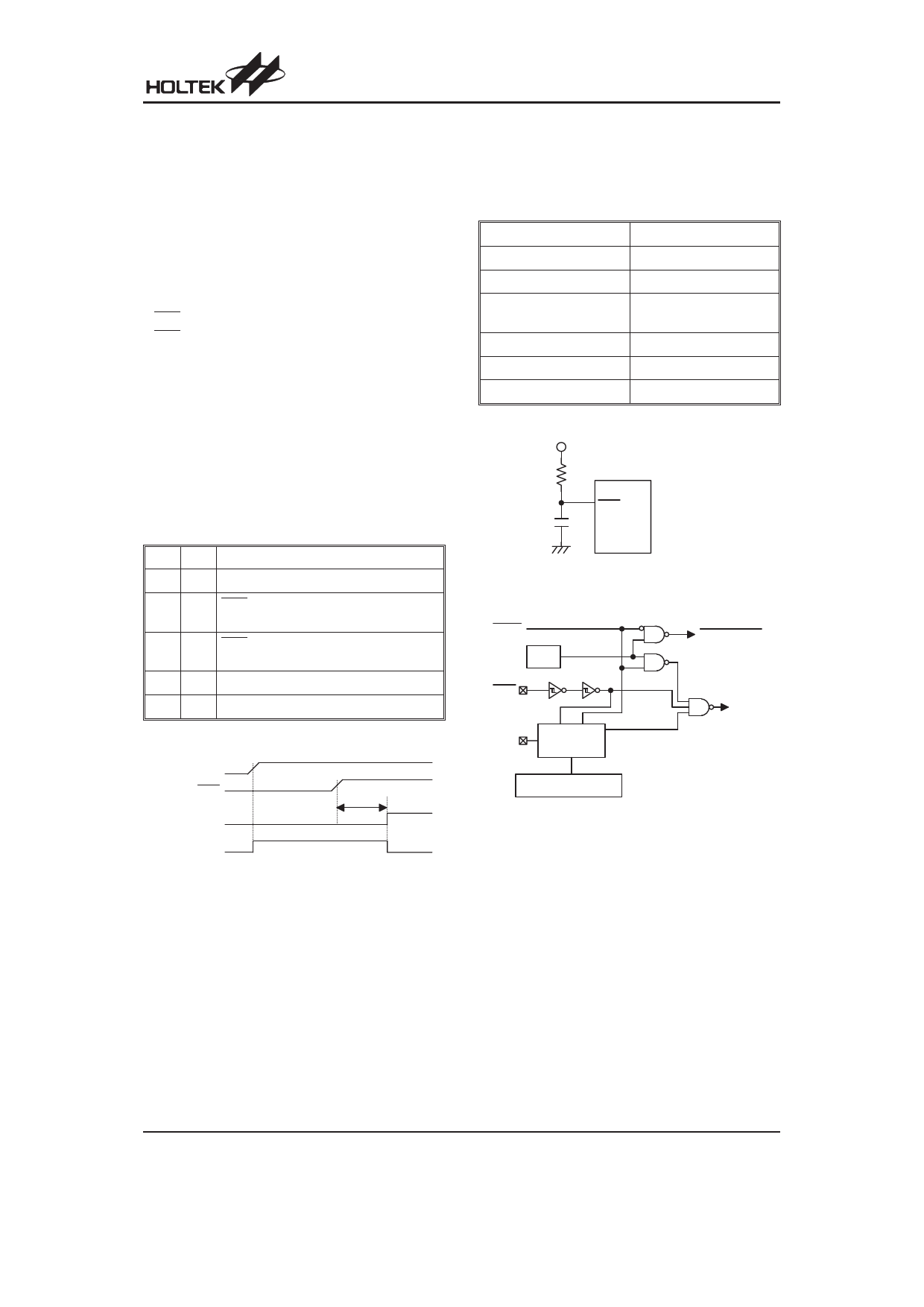

TO PDF

RESET Conditions

0 0 System power-up

u

u

RES reset or LVR reset during normal

operation

0

1

RES reset or LVR reset wake-up from

HALT mode

1 u WDT time-out during normal operation

1 1 WDT wake-up from HALT mode

Note: ²u² means ²unchanged²

VDD

RES

tS S T

S S T T im e - o u t

C h ip R e s e t

Reset Timing Chart

To guarantee that the crystal oscillator has started and

stabilized, the SST (system start-up timer) provides an

extra delay of 8192 system clock pulses when the sys-

tem powers up.

The functional unit chip reset status are shown below.

Program Counter

000H

Interrupt

Disabled

Prescaler, Divider

Cleared

WDT, Real Time Clock, Clear. After master reset,

Time Base

begin counting

Timer/event Counter

Off

Input/output Ports

Input mode

Stack Pointer

Points to the top of the stack

V DD

RES

Reset Circuit

H A LT

W DT

W DT

T im e - o u t

R eset

RES

E x te rn a l

O SC1

SST

1 3 - b it R ip p le

C o u n te r

W a rm R e s e t

C o ld

R eset

P o w e r - o n D e te c tio n

Reset Configuration

Rev. 2.30

14

December 2, 2005