SI8610 Ver la hoja de datos (PDF) - Silicon Laboratories

Número de pieza

componentes Descripción

Fabricante

SI8610 Datasheet PDF : 36 Pages

| |||

Si8610/20/21/22

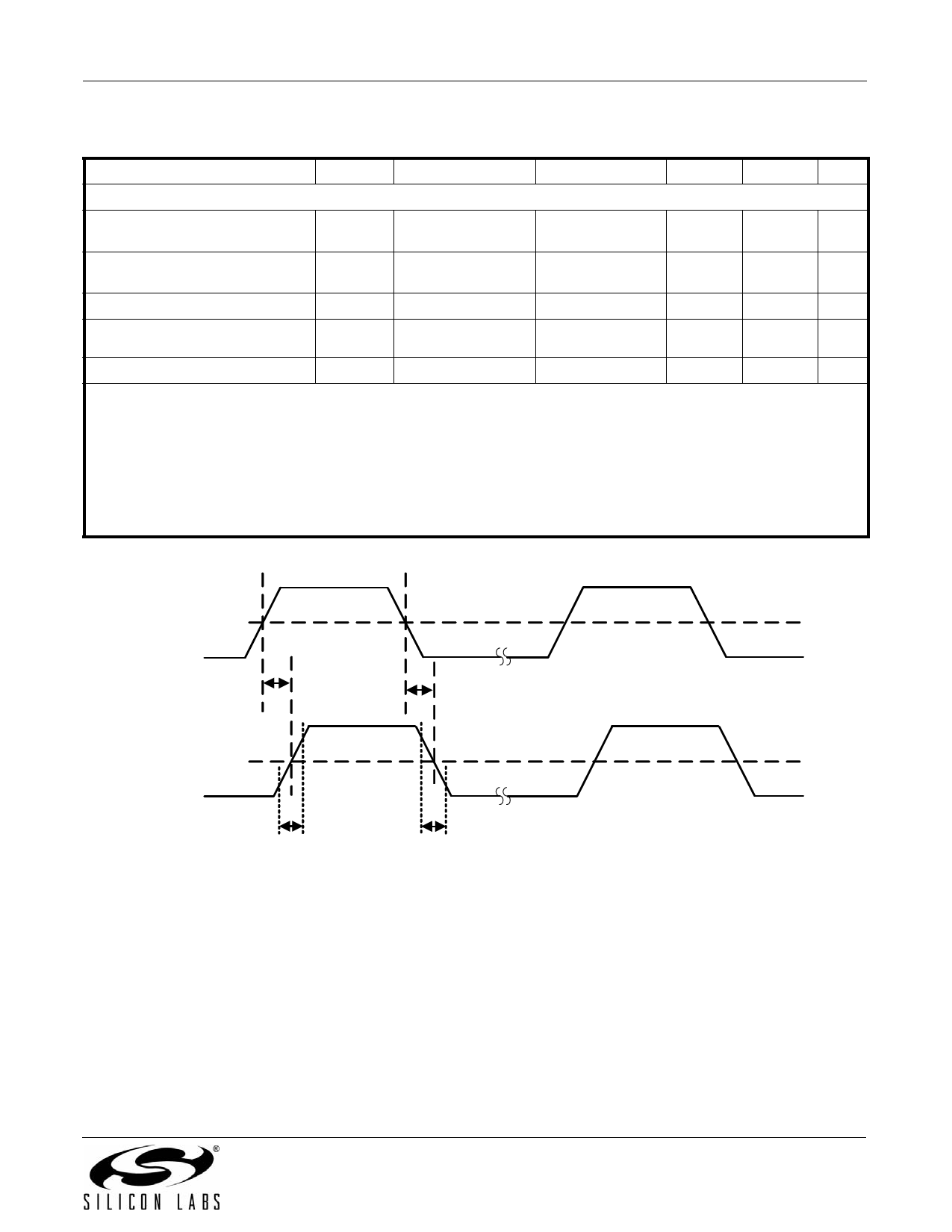

Table 2. Electrical Characteristics (Continued)

(VDD1 = 5 V ±10%, VDD2 = 5 V ±10%, TA = –40 to 125 ºC)

Parameter

All Models

Output Rise Time

Symbol Test Condition

Min

tr

CL = 15 pF

See Figure 1

—

Typ

Max Unit

2.5

4.0

ns

Output Fall Time

tf

CL = 15 pF

See Figure 1

—

2.5

4.0

ns

Peak Eye Diagram Jitter

tJIT(PK)

See Figure 6

—

350

—

ps

Common Mode Transient

Immunity

CMTI

VI = VDD or 0 V

35

50

— kV/µs

Startup Time3

tSU

—

15

40

µs

Notes:

1. The nominal output impedance of an isolator driver channel is approximately 50 , ±40%, which is a

combination of the value of the on-chip series termination resistor and channel resistance of the output driver

FET. When driving loads where transmission line effects will be a factor, output pins should be appropriately

terminated with controlled impedance PCB traces.

2. tPSK(P-P) is the magnitude of the difference in propagation delay times measured between different units

operating at the same supply voltages, load, and ambient temperature.

3. Start-up time is the time period from the application of power to valid data at the output.

1.4 V

Typical

Input

1.4 V

Typical

Output

tPLH

tPHL

90%

10%

90%

10%

tr

tf

Figure 1. Propagation Delay Timing

Rev. 1.3

7