SST58SM032-70-C-FSI データシートの表示(PDF) - Silicon Storage Technology

部品番号

コンポーネント説明

メーカー

SST58SM032-70-C-FSI Datasheet PDF : 40 Pages

| |||

ATA-Disk Module

SST58SM008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

SST58LM008 / 016 / 024 / 032 / 048 / 064 / 096 / 128 / 192

Advance Information

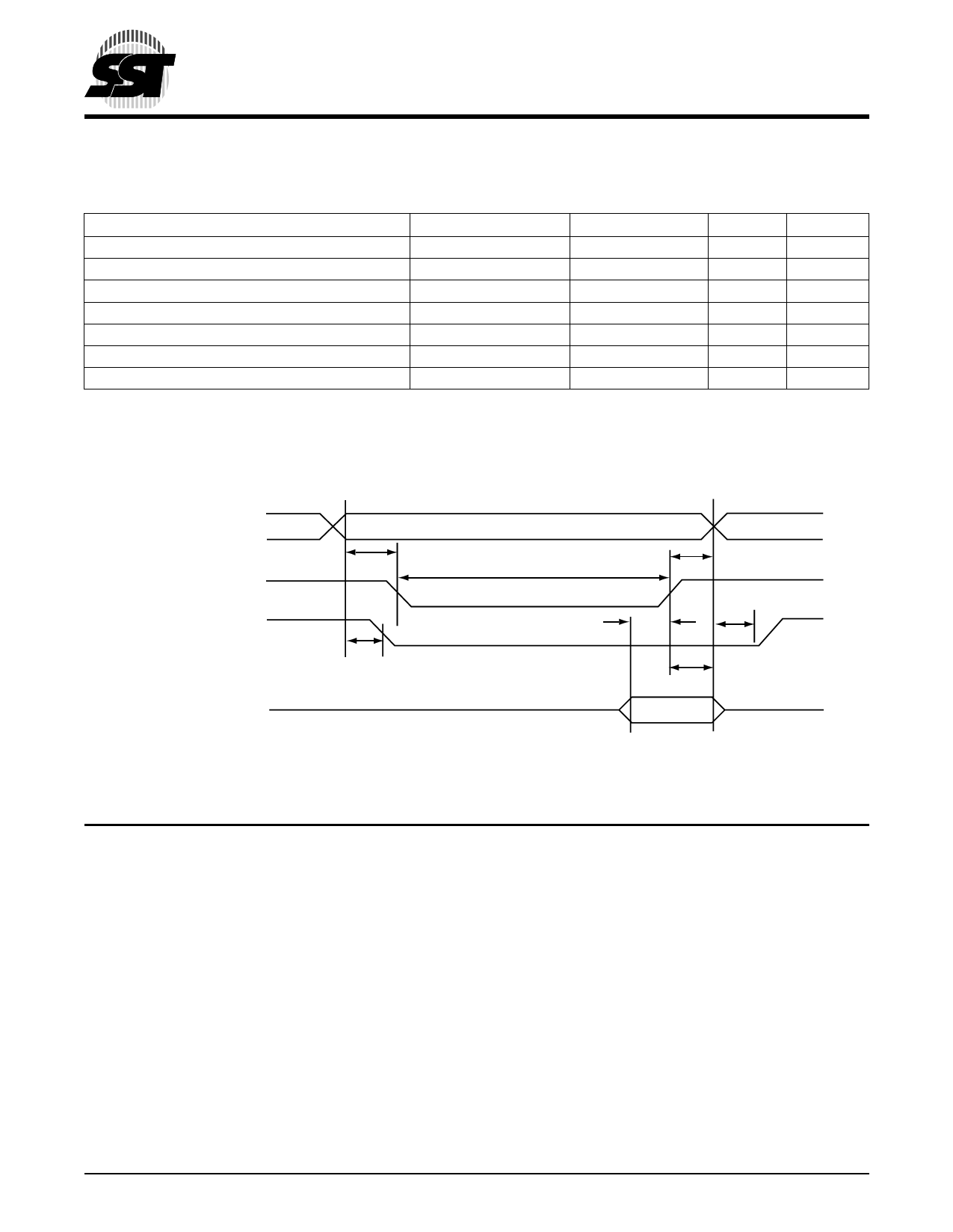

2.3.6 I/O Input (Read) Timing Specification

TABLE 2-5: I/O READ TIMING

Item

Data Setup before IORD#

Data Hold following IORD#

IORD# Width Time

Valid Address Setup before IORD#

Valid Address Hold following IORD#

IOCS16# Delay Falling from Address

IOCS16# Delay Rising from Address

Symbol

tsu(IORD)

th(IORD)

tw(IORD)

tsuA(IORD)

thA(IORD)

tdfIOCS16(ADR)

tdrIOCS16(ADR)

IEEE Symbol

tDVIRH

tlGHQX

tlGLIGH

tAVIGL

tlGHAX

tAVISL

tAVISH

Note: All times are in nanoseconds. The maximum load on IOCS16# is 1 LSTTL with 50pF total load.

All AC specifications are guaranteed by design.

Min

Max

20

-

5

-

70

-

25

-

10

-

-

20

20

T2-5.4 519

Valid Address1

IORD#

IOCS16#

tdfIOCS16(ADR)

tsuA(IORD)

tw(IORD)

tsu (IORD)

D15-D0

Dout

1. Valid Address consists of signals CS1FX#, CS3FX#, and A2-A0.

FIGURE 1: I/O READ TIMING DIAGRAM

thA(IORD)

tdrIOCS16(ADR)

th(IORD)

519 ILL2-7.3

©2001 Silicon Storage Technology, Inc.

12

S71193-01-000 9/01 519