VSC9110 データシートの表示(PDF) - Vitesse Semiconductor

部品番号

コンポーネント説明

メーカー

VSC9110 Datasheet PDF : 24 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

STS-48 Physical Layer

ATM UNI/NNI Device

Data Sheet

VSC9110

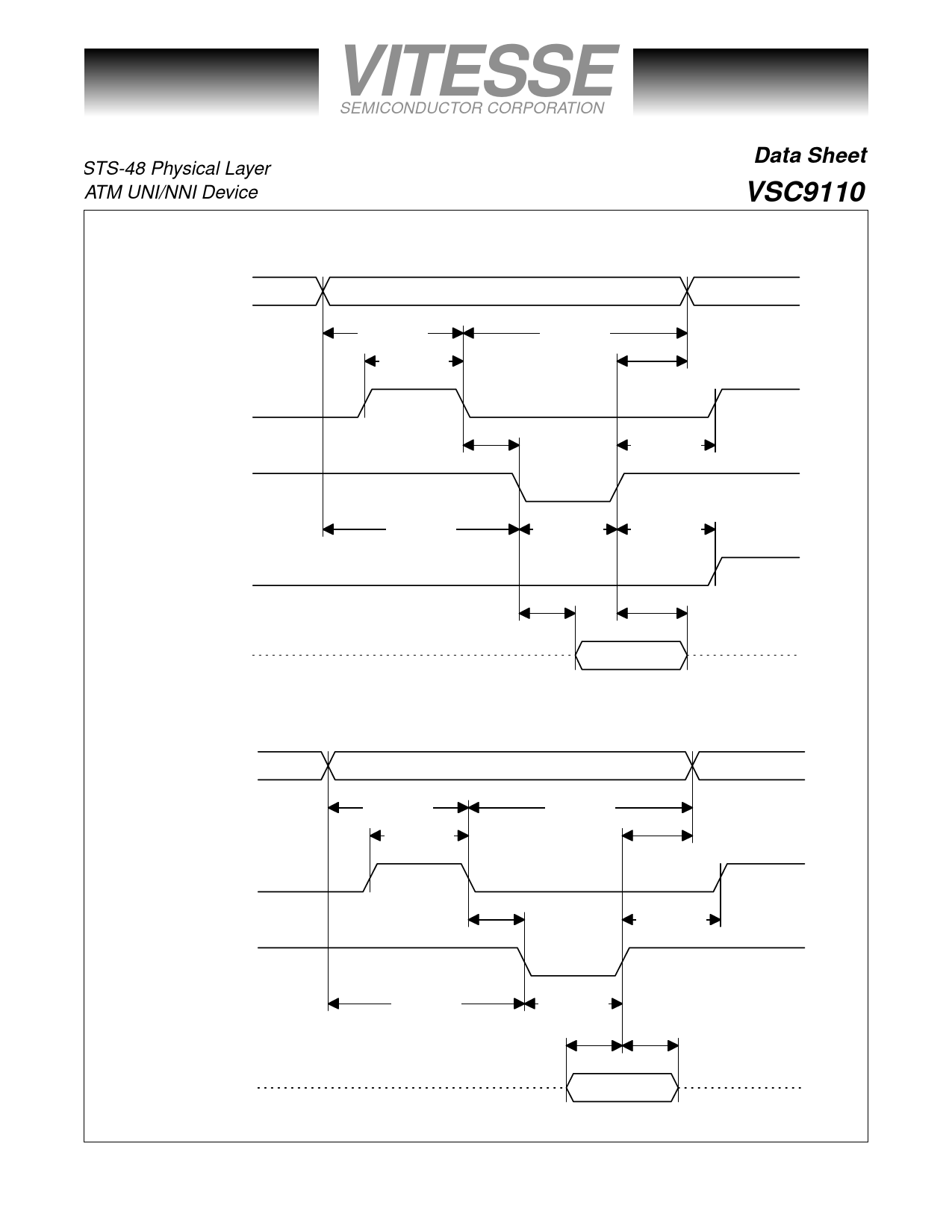

Figure 6: CPU Read Access Timing Dependencies

A[7..0]

ALE

CSB

RDB

INTB

D[7..0]

Valid Address

TSU,ALE

TPW,ALE

TH,ALE

TH,AR/W

TSU,LR/W

TH,LR/W

TSU,AR/W

TPW,R/W

TZ,INTR

TP,RD

Valid Data

TZ,RD

A[7..0]

ALE

CSB

WRB

D[7..0]

Figure 7: CPU Write Access Timing Dependencies

Valid Address

TSU,ALE

TPW,ALE

TH,ALE

TH,AR/W

TSU,LR/W

TH,LR/W

TSU,AR/W

TPW,R/W

TSU, DW

Valid Data

TH, DW

Page 12

© VITESSE SEMICONDUCTOR CORPORATION

741 Calle Plano, Camarillo, CA 93012 • 805/388-3700 • FAX: 805/987-5896

G52198-0, Rev. 4.2

1/8/00