WC32P040-33P4M データシートの表示(PDF) - White Electronic Designs Corporation

部品番号

コンポーネント説明

メーカー

WC32P040-33P4M

White Electronic Designs Corporation

WC32P040-33P4M Datasheet PDF : 23 Pages

| |||

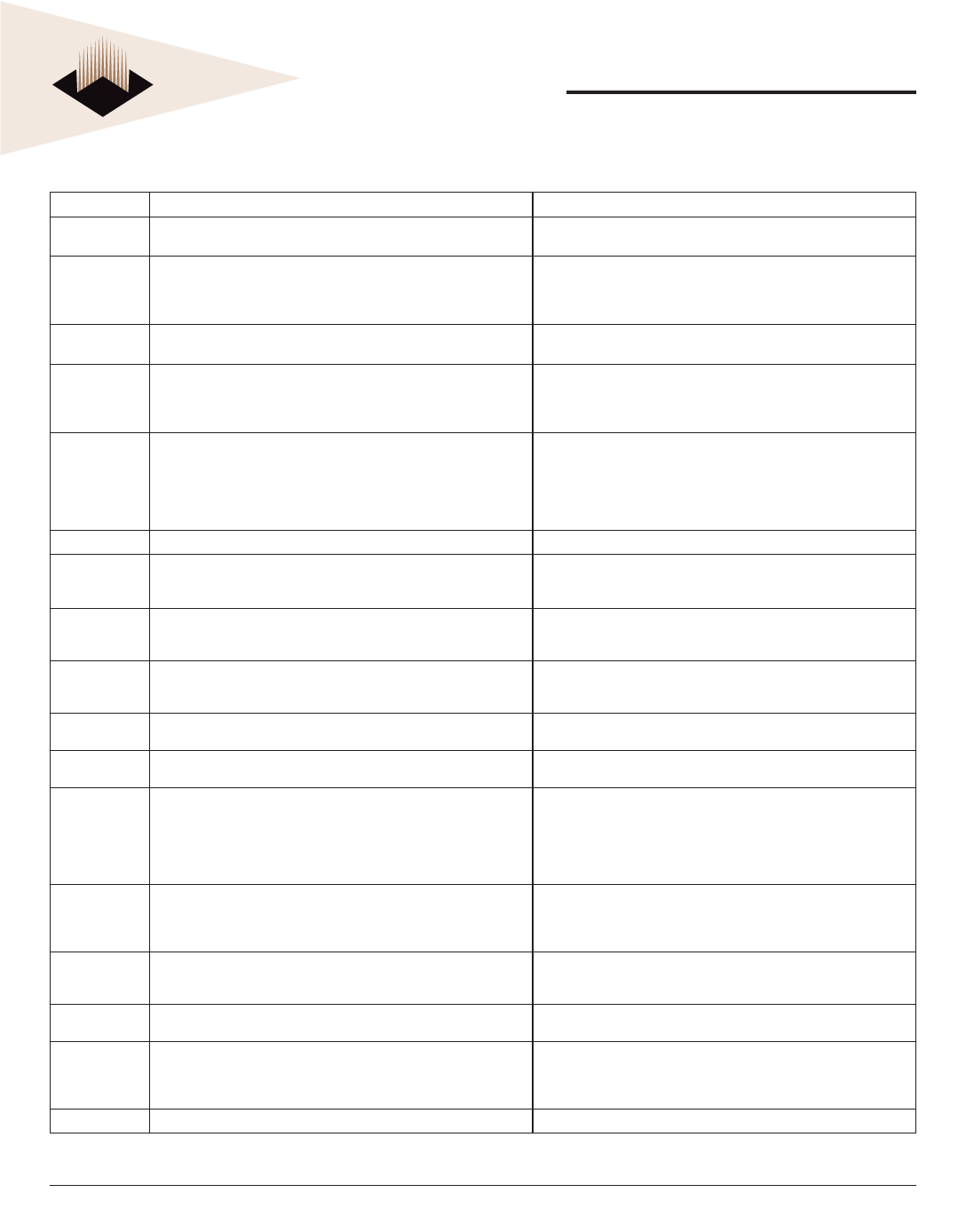

White Electronic Designs

WC32P040-XXM

Opcode

FMOVE

FMOVEM

FMOVEM

FMUL

FNEG

FNOP

FRESTORE

FSAVE

FScc

FSGLDIV

FSGLMUL

FSQRT

FSUB

FTRAPcc

FTST

ILLEGAL

JMP

INSTRUCTION SET SUMMARY (contd)

Operation

Source Destination

Register List Destination

Source Register List

Register List Destination

Source Register List

Source x FPn FPn

–(Source) FPn

None

If in supervisor state

then FPU State Frame Internal State

else TRAP

If in supervisor state

then FPU Internal State State Frame

else TRAP

If condition true

then 1s Destination

else 0s Destination

FPn ÷ Source FPn

Source x FPn FPn

Square Root of Source FPn

FPn – Source FPn

If condition true

then TRAP

Condition Codes tor Operand FPCC

SSP – 2 SSP; Vector Offset (SSP);

SSP – 4 SSP; PC (SSP);

SSp – 2 SSP; SR (SSP)

Illegal Instruction Vector Address PC

Destination Address PC

Syntax

FMOVE.L <ea>,FPcr

FMOVE.L FPcr,<ea>

FMOVEM.X <list>,<ea>(3)

FMOVEM.X Dn,<ea>

FMOVEM.X <ea>,<list>(3)

FMOVEM.X <ea>,Dn

FMOVEM.L <list>,<ea>(4)

FMOVEM.L <ea>,<list>(4)

FMUL.<fmt> <ea>,FPn

FMUL.X FPm,FPn

FrMUL<fmt> <ea>,FPn(2)

FrMUL.X FPm,FPn(3)

FNEG.<fmt> <ea>,FPn

FNEG.X FPm,FPn

FNEG.X FPn

FrNEG.<fmt> <ea>,FPn(2)

FrNEG.X FPm,FPn(2)

FrNEG.X FPn(2)

FNOP

FRESTORE <ea>

FSAVE <ea>

FScc.SIZE <ea>

FSGLDIV.<fmt> <ea>,FPn

FSGLDIV.X FPm,FPn

FSGMUL.<tmt> <ea>,FPn

FSGLMUL.X FPm, FPn

FSQRT.<fmt> <ea>,FPn

FSQRT.X FPm,FPn

FSQRT.X FPn

FrSQRT.<fmt> <ea,,FPn(2)

FrSQRT FPm,FPn(2)

FrSQRT FPn(2)

FSUB.<fmt> <ea>,FPn

FSUB.X FPm,FPn

FrSUB.<tmt> <ea>,FPn(2)

FrSUB.X FPm,FPn3(2)

FTRAPcc

FTRAPcc.W #<data>

FTRAPcc.L #<data>

FTST.dmt> <ea>

FTST.X FPm

ILLEGAL

JMP <ea>

July 1998

7

White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com