74ABT16899 データシートの表示(PDF) - Philips Electronics

部品番号

コンポーネント説明

メーカー

74ABT16899

Philips Electronics

74ABT16899 Datasheet PDF : 16 Pages

| |||

Philips Semiconductors

18-bit latched transceiver with 16-bit

parity generator/checker (3-State)

Product specification

74ABT16899

74ABTH16899

FEATURES

• Symmetrical (A and B bus functions are identical)

• Selectable generate parity or ”feed-through” parity for A-to-B and

B-to-A directions

• Independent transparent latches for A-to-B and B-to-A directions

• Selectable ODD/EVEN parity

• Continuously checks parity of both A bus and B bus latches as

ERRA and ERRB

• Open-collector ERR output

• Ability to simultaneously generate and check parity

• Can simultaneously read/latch A and B bus data

• Output capability: +64 mA/–32mA

• Latch-up protection exceeds 500mA per Jedec Std 17

• ESD protection exceeds 2000 V per MIL STD 883 Method 3015

and 200 V per Machine Model

• Power up 3-State

• Power-up reset

• Live insertion/extraction permitted

• Bus-hold data inputs eliminate the need for external pull-up

resistors to hold unused inputs

DESCRIPTION

The 74ABT/H16899 is a 16-bit to 16-bit parity transceiver with

separate transparent latches for the A bus and B bus. Either bus

can generate or check parity. The parity bit can be fed-through with

no change or the generated parity can be substituted with the SEL

input.

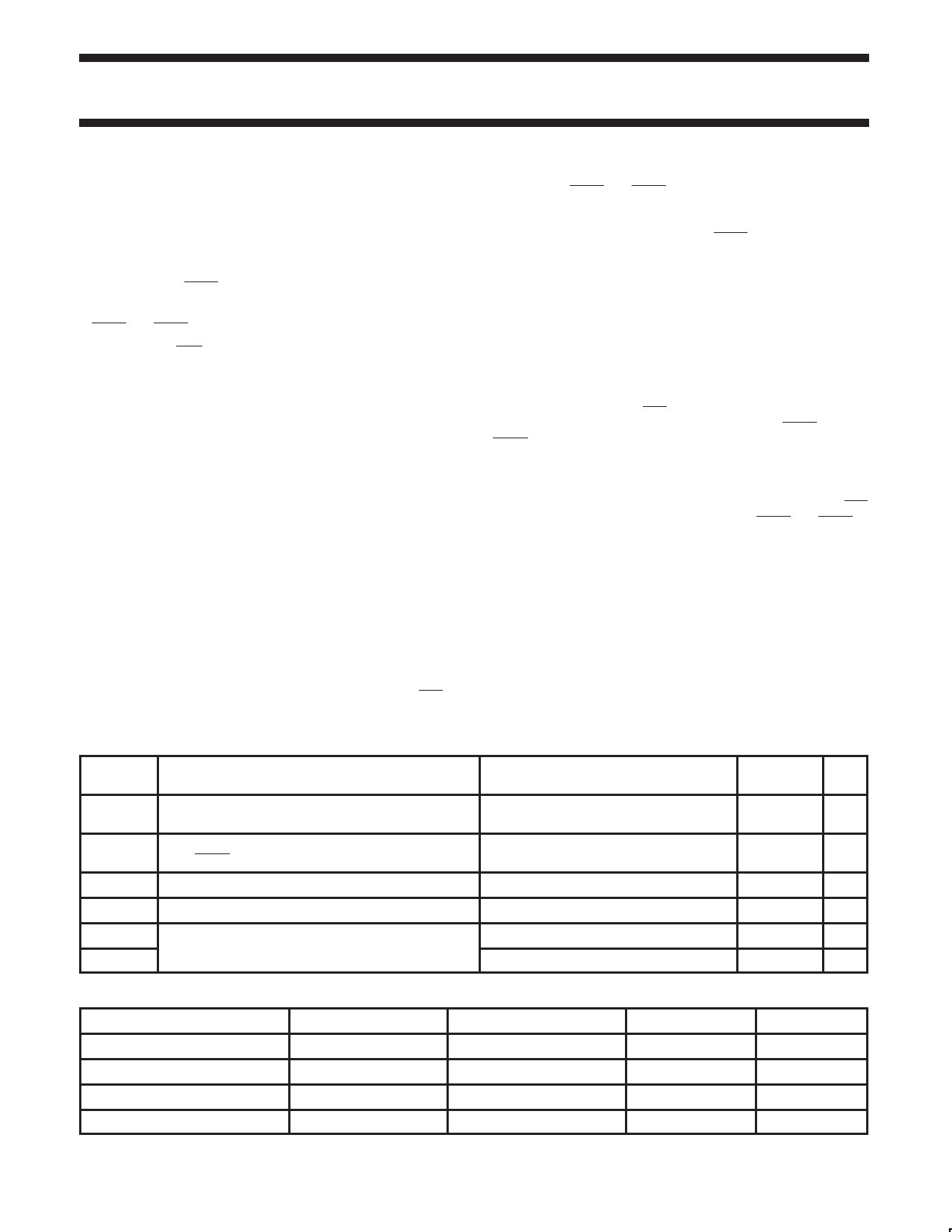

QUICK REFERENCE DATA

SYMBOL

PARAMETER

tPLH

tPHL

tPLH

tPHL

CIN

CI/O

ICCZ

ICCL

Propagation delay

An to Bn or Bn to An

Propagation delay

An to ERRA

Input capacitance

Output capacitance

Quiescent supply current

Parity error checking of the A and B bus latches is continuously

provided with ERRA and ERRB, even with both buses in 3-State.

The 74ABT/H16899 features independent latch enables for the A

and B bus latches, a select pin for ODD/EVEN parity, and separate

error signal output pins for checking parity.

FUNCTIONAL DESCRIPTION

The 74ABT/H16899 has three principal modes of operation which

are outlined below. All modes apply to both the A-to-B and B-to-A

directions.

Transparent latch, Generate parity, Check A and B bus parity:

Bus A (B) communicates to Bus B (A), parity is generated and

passed on to the B (A) Bus as BPAR (APAR). If LEA and LEB are

High and the Mode Select (SEL) is Low, the parity generated from

A0-A7 and B0-B7 can be checked and monitored by ERRA and

ERRB. (Fault detection on both input and output buses.)

Transparent latch, Feed-through parity, Check A and B bus

parity:

Bus A (B) communicates to Bus B (A) in a feed-through mode if SEL

is High. Parity is still generated and checked as ERRA and ERRB

and can be used as an interrupt to signal a data/parity bit error to the

CPU.

Latched input, Generate/Feed-through parity, Check A (and B)

bus parity:

Independent latch enables (LEA and LEB) allow other permutations

of:

• Transparent latch / 1 bus latched / both buses latched

• Feed-through parity / generate parity

• Check in bus parity / check out bus parity / check in and out bus

parity

CONDITIONS

Tamb = 25°C; GND = 0V

CL = 50pF; VCC = 5V

CL = 50pF; VCC = 5V

VI = 0V or VCC

Outputs disabled; VO = 0V or VCC

Outputs disabled; VCC =5.5V

Output Low; VCC = 5.5V

TYPICAL UNIT

2.7

ns

5.0

ns

4

pF

7

pF

500

µA

10.5

mA

ORDERING INFORMATION

PACKAGES

56-Pin Plastic SSOP Type III

56-Pin Plastic TSSOP Type II

56-Pin Plastic SSOP Type III

56-Pin Plastic TSSOP Type II

TEMPERATURE RANGE OUTSIDE NORTH AMERICA

–40°C to +85°C

74ABT16899 DL

–40°C to +85°C

74ABT16899 DGG

–40°C to +85°C

74ABTH16899 DL

–40°C to +85°C

74ABTH16899 DGG

NORTH AMERICA

BT16899 DL

BT16899 DGG

BH16899 DL

BH16899 DGG

DWG NUMBER

SOT371-1

SOT364-1

SOT371-1

SOT364-1

1998 Feb 25

2

853-1960 19018