A8351601 データシートの表示(PDF) - AMIC Technology

部品番号

コンポーネント説明

メーカー

A8351601 Datasheet PDF : 44 Pages

| |||

A8351601 Series

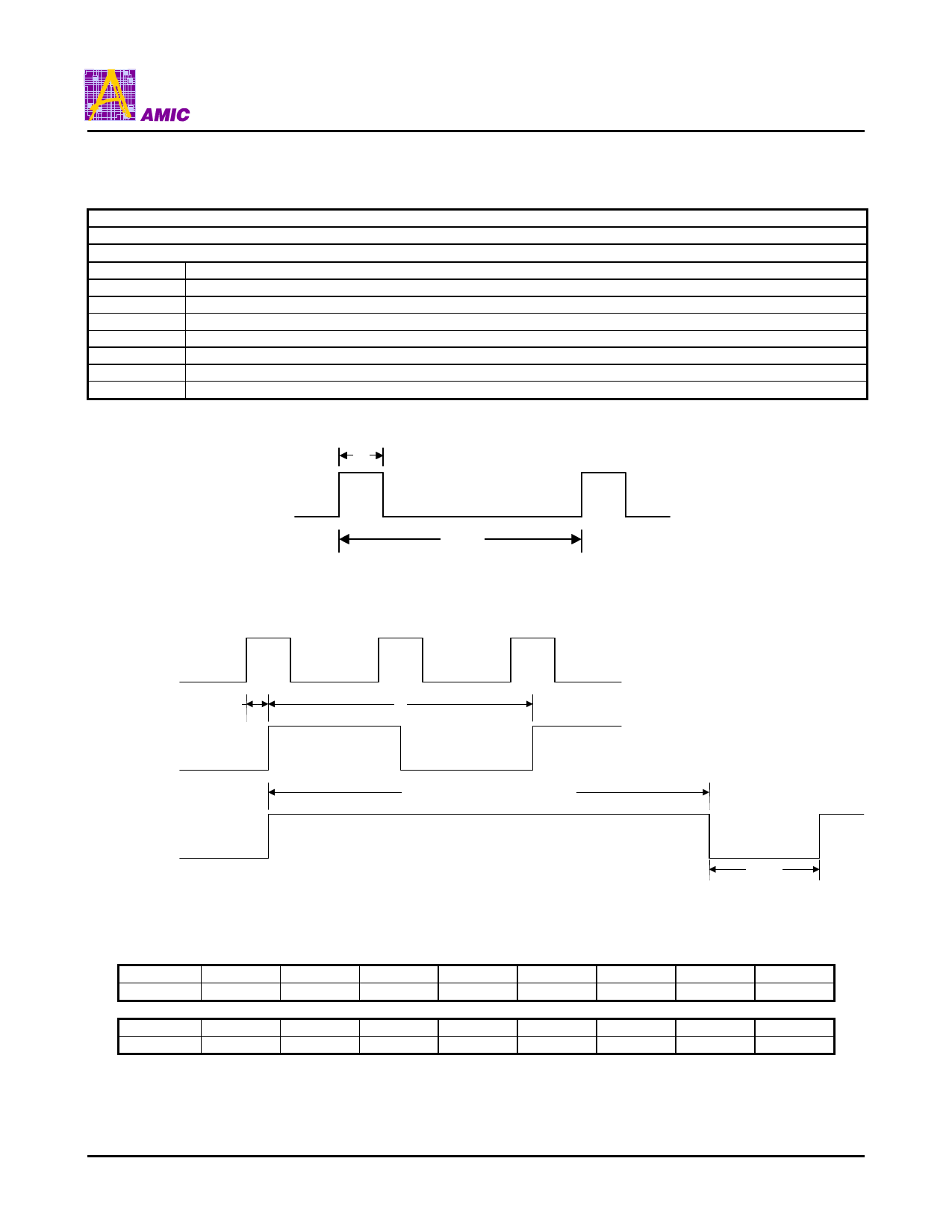

PWM1:

Pulse Width Modulation 1 Register. Not Bit Addressable.

7

6

5

4

3

2

1

-

PWM1.6

PWM1.5

PWM1.4

PWM1.3

PWM1.2

PWM1.1

Register Description:

PWM1.7

PWM4 output control. Set/Clear by specify 75% duty/67% duty.

PWM1.6

PWM1 frequency control bit. Set/Cleared by specify half/normal PWM1 frequency.

PWM1.5

PWM1 cycle control bit.

PWM1.4

PWM1 cycle control bit.

PWM1.3

PWM1 cycle control bit.

PWM1.2

PWM1 cycle positive edge width control bit.

PWM1.1

PWM1 cycle positive edge width control bit.

PWM1.0

PWM1 cycle positive edge width control bit.

Note:

T2

0

PWM1.0

T1

PWM1

Delay 4~11 CLK

PWM3

PWM4

T3

3072 T3(PWM1.7:1)/2048 T3(PWM1.7:0)

1024 T3

Xtal frequency = 14.7456MHz

Bit<5:3>

0

1

T1

1.017us 1.695us

Bit<2:0>

T2

0

542.4ns

1

67.8ns

2

2.373us

2

135.6ns

3

3.051us

3

203.4ns

4

3.729us

4

271.2ns

5

4.407us

5

339ns

6

5.085us

6

406.8ns

7

5.763us

7

474.6ns

(July, 2002, Version 1.0)

12

AMIC Technology, Inc.