AD9915BCPZ データシートの表示(PDF) - Analog Devices

部品番号

コンポーネント説明

メーカー

AD9915BCPZ Datasheet PDF : 47 Pages

| |||

AD9915

Data Sheet

Bits Mnemonic

Description

9

External OSK enable

0 = manual OSK enabled (default).

1 = automatic OSK enabled.

Ineffective unless CFR1[8] = 1.

8

OSK enable

0 = OSK disabled (default).

1 = OSK enabled. To engage any digital amplitude adjust using DRG, profile, or direct mode via

the 32-bit parallel port, or OSK pin, this bit must be set.

7

Digital power-down

This bit is effective without the need for an input/output update.

0 = clock signals to the digital core are active (default).

1 = clock signals to the digital core are disabled.

6

DAC power-down

0 = DAC clock signals and bias circuits are active (default).

1 = DAC clock signals and bias circuits are disabled.

5

REFCLK input power-down

This bit is effective without the need for an input/output update.

0 = REFCLK input circuits and PLL are active (default).

1 = REFCLK input circuits and PLL are disabled.

4

Open

Open.

3

External power-down control 0 = assertion of the EXT_PWR_DWN pin affects power-down.

1 = assertion of the EXT_PWR_DWN pin affects fast recovery power-down (default).

2

Open

Open.

1

SDIO input only

0 = configures the SDIO pin for bidirectional operation; 2-wire serial programming

mode (default).

1 = configures the serial data input/output pin (SDIO) as an input only pin; 3-wire serial

programming mode.

0

LSB first mode

0 = configures the serial input/output port for MSB-first format (default).

1 = configures the serial input/output port for LSB-first format.

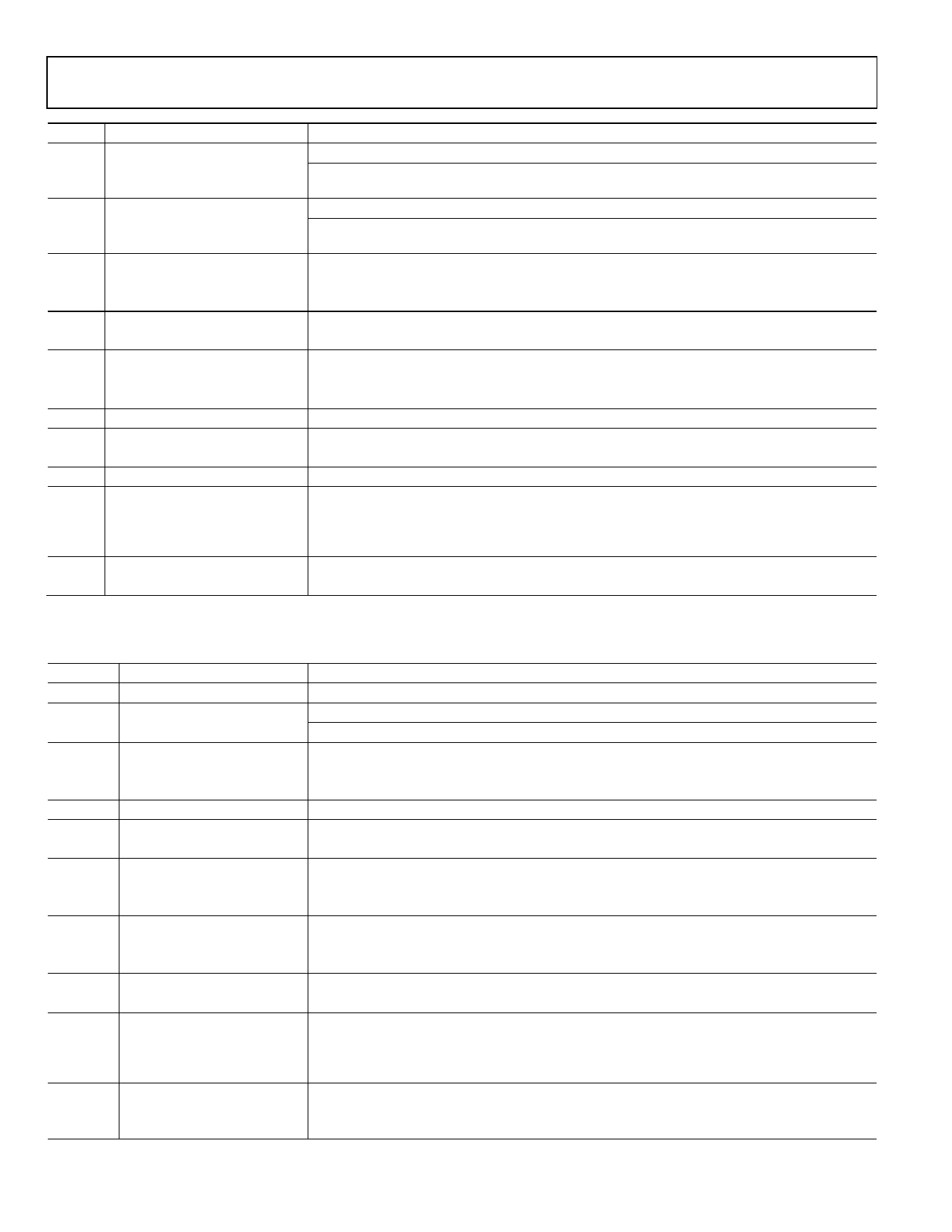

Control Function Register 2 (CFR2)—Address 0x01

Table 18. Bit Descriptions for CFR2

Bit(s)

Mnemonic

[31:24] Open

23

Profile mode enable

22

Parallel data port enable

[21:20]

19

18

Digital ramp destination

Digital ramp enable

Digital ramp no-dwell high

17

Digital ramp no-dwell low

16

Programmable modulus

enable

15

Matched latency enable

14

Frequency jump enable

Description

Open

0 = disables profile mode functionality (default).

1 = enables profile mode functionality. Profile pins select the desired profile.

See the Parallel Data Port Modulation Mode section for more details.

0 = disables parallel data port modulation functionality (default).

1 = enables parallel data port modulation functionality.

See Table 9 for details. Default is 00. See the Digital Ramp Generator (DRG) section for more details.

0 = disables digital ramp generator functionality (default).

1 = enables digital ramp generator functionality.

See the Digital Ramp Generator (DRG) section for details.

0 = disables no-dwell high functionality (default).

1 = enables no-dwell high functionality.

See the Digital Ramp Generator (DRG) section for details.

0 = disables no-dwell low functionality (default).

1 = enables no-dwell low functionality.

0 = disables programmable modulus.

1 = enables programmable modulus.

0 = simultaneous application of amplitude, phase, and frequency changes to the DDS arrive at

the output in the order listed in Table 2 under data latency (pipe line delay) (default).

1 = simultaneous application of amplitude, phase, and frequency changes to the DDS arrive at

the output simultaneously.

0 = disables frequency jump.

1 = enables frequency jump mode. Must have the digital generator DRG enabled for this

feature.

Rev. F | Page 42 of 47