CY22394 データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CY22394 Datasheet PDF : 17 Pages

| |||

CY22393

CY22394

CY22395

PLL*_En

This bit enables the PLL when HIGH. If PLL2 or PLL3 are not

enabled, then any output selecting the disabled PLL must

have a divider setting of zero (off). Since the PLL1_En bit is

dynamic, internal logic automatically turns off dependent

outputs when PLL1_En goes LOW.

DivSel

This bit controls which register is used for the CLKA and CLKB

dividers.

OscCap[5:0]

This controls the internal capacitive load of the oscillator. The

approximate effective crystal load capacitance is:

CLOAD = 6pF + (OscCap × 0.375pF)

Set to zero for external reference clock.

OscDrv[1:0]

These bits control the crystal oscillator gain setting. These

should always be set according to Table 5. The parameters

are the Crystal Frequency, Internal Crystal Parasitic Resis-

tance (available from the manufacturer), and the OscCap

setting during crystal start up, which occurs when power is

applied, or after shutdown is released. If in doubt, use the next

higher setting.

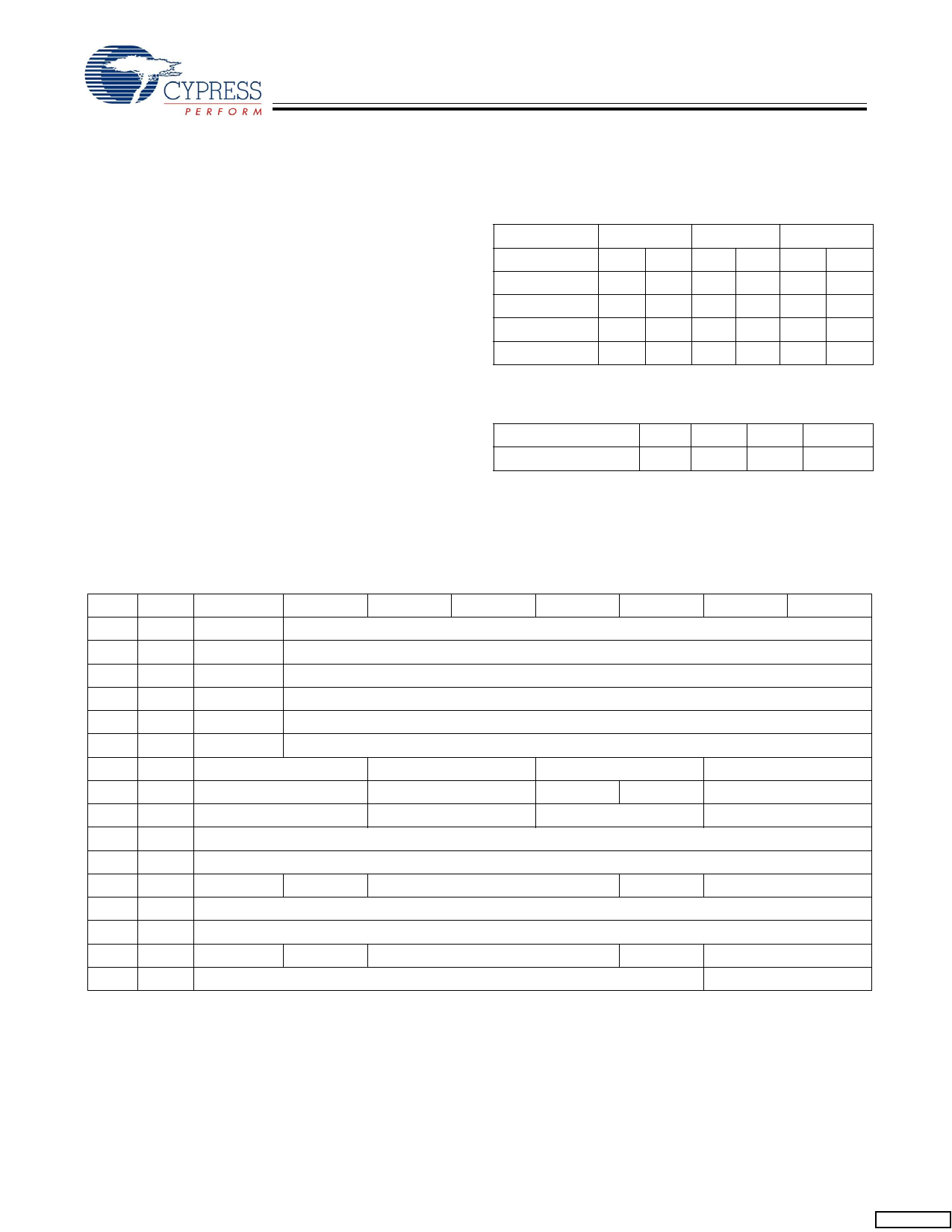

Table 5.

OscCap

00H–20H

Crystal Freq\ R 30Ω 60Ω

8–15 MHz

00 01

15–20 MHz 01 10

20–25 MHz 01 10

25–30 MHz 10 10

20H–30H

30Ω 60Ω

01 10

01 10

10 10

10 11

30H–40H

30Ω 60Ω

01 10

10 10

10 11

11 NA

For external reference, the use Table 6.

Table 6.

External Freq (MHz) 1–25 25–50

OscDrv[1:0]

00

01

50–90

10

90–166

11

Reserved

These bits must be programmed LOW for proper operation of

the device.

Serial Programming Bitmaps — Summary Tables

Addr DivSel

b7

b6

08H

0

ClkA_FS[0]

09H

1

ClkA_FS[0]

0AH 0 ClkB_FS[0]

0BH 1 ClkB_FS[0]

0CH – ClkC_FS[0]

0DH – ClkD_FS[0]

0EH –

ClkD_FS[2:1]

0FH

–

Clk{C,X}_ACAdj[1:0]

10H

–

ClkX_DCAdj[1]

11H

–

12H

–

13H

–

Reserved PLL2_En

14H

–

15H

–

16H

–

Reserved PLL3_En

17H

–

b5

b4

b3

b2

ClkA_Div[6:0]

ClkA_Div[6:0]

ClkB_Div[6:0]

ClkB_Div[6:0]

ClkC_Div[6:0]

ClkD_Div[6:0]

ClkC_FS[2:1]

ClkB_FS[2:1]

Clk{A,B,D,E}_ACAdj[1:0] PdnEn Xbuf_OE

Clk{D,E}_DCAdj[1]

ClkC_DCAdj[1]

PLL2_Q[7:0]

PLL2_P[7:0]

PLL2_LF[2:0]

PLL2_PO

PLL3_Q[7:0]

PLL3_P[7:0]

PLL3_LF[2:0]

PLL3_PO

Osc_Cap[5:0]

b1

b0

ClkA_FS[2:1]

ClkE_Div[1:0]

Clk{A,B}_DCAdj[1]

PLL2_P[9:8]

PLL3_P[9:8]

Osc_Drv[1:0]

Document #: 38-07186 Rev. *C

Page 7 of 17

[+] Feedback