CY7C1325G-133BGI データシートの表示(PDF) - Cypress Semiconductor

部品番号

コンポーネント説明

メーカー

CY7C1325G-133BGI Datasheet PDF : 16 Pages

| |||

CY7C1325G

Maximum Ratings

(Above which the useful life may be impaired. For user guide-

lines, not tested.)

Storage Temperature ................................. –65°C to +150°C

Ambient Temperature with

Power Applied............................................. –55°C to +125°C

Supply Voltage on VDD Relative to GND........ –0.5V to +4.6V

Supply Voltage on VDDQ Relative to GND ...... –0.5V to +VDD

DC Voltage Applied to Outputs

in tri-state ............................................ –0.5V to VDDQ + 0.5V

DC Input Voltage ................................... –0.5V to VDD + 0.5V

Current into Outputs (LOW)......................................... 20 mA

Static Discharge Voltage.......................................... > 2001V

(per MIL-STD-883, Method 3015)

Latch-up Current.................................................... > 200 mA

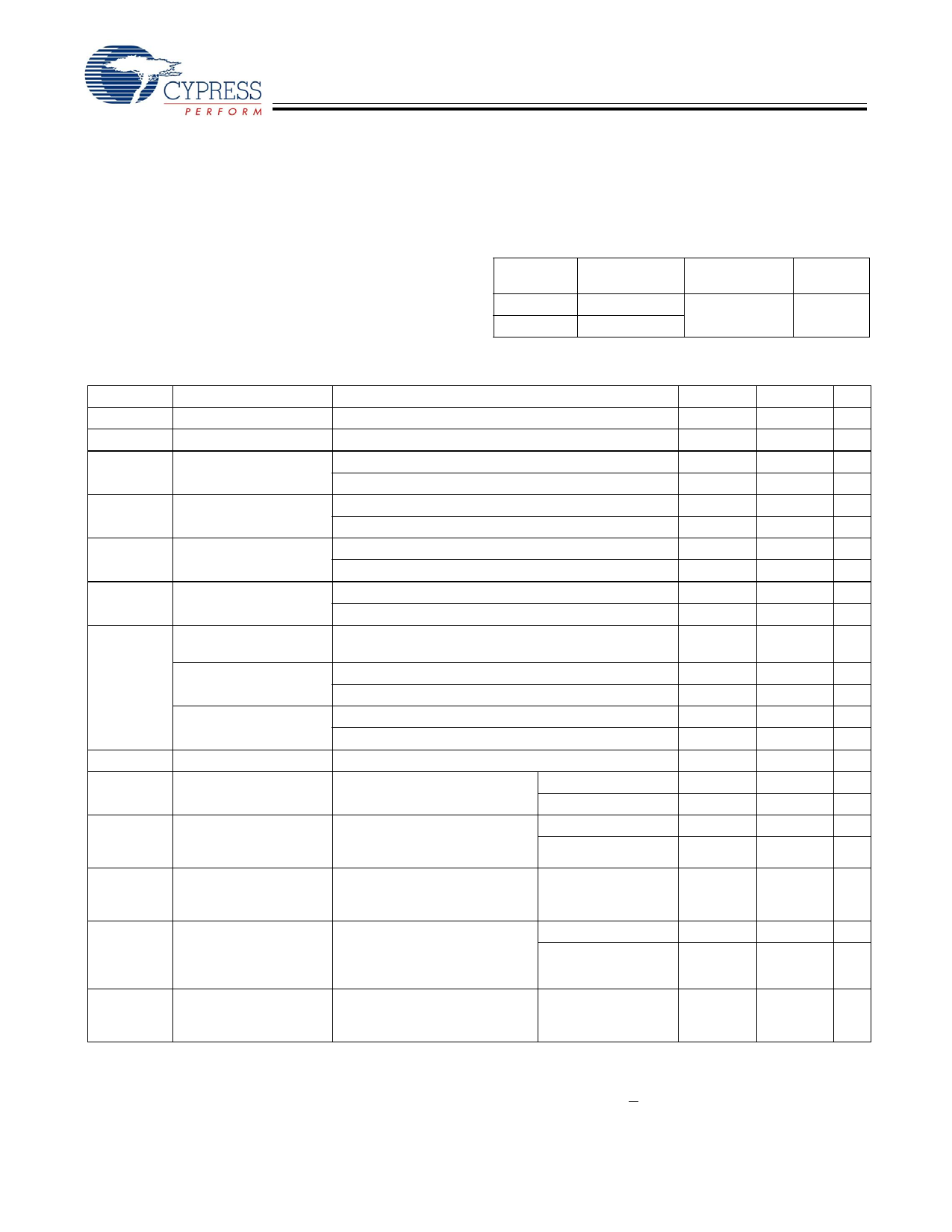

Operating Range

Range

Ambient

Temperature]

Commercial 0°C to +70°C

Industrial –40°C to +85°C

VDD

3.3V −5%/+10%

VDDQ

2.5V –5%

to VDD

Electrical Characteristics Over the Operating Range [7, 8]

Parameter

Description

Test Conditions

VDD

VDDQ

VOH

VOL

VIH

VIL

Power Supply Voltage

I/O Supply Voltage

Output HIGH Voltage

Output LOW Voltage

Input HIGH Voltage

Input LOW Voltage[7]

for 3.3V I/O, IOH = –4.0 mA

for 2.5V I/O, IOH = –1.0 mA

for 3.3V I/O, IOL = 8.0 mA

for 2.5V I/O, IOL = 1.0 mA

for 3.3V I/O

for 2.5V I/O

for 3.3V I/O

for 2.5V I/O

IX

Input Leakage Current GND ≤ VI ≤ VDDQ

except ZZ and MODE

Input Current of MODE Input = VSS

Input = VDD

Input Current of ZZ

Input = VSS

Input = VDD

IOZ

Output Leakage Current GND ≤ VI ≤ VDDQ, Output Disabled

IDD

VDD Operating Supply VDD = Max., IOUT = 0 mA,

7.5-ns cycle, 133 MHz

Current

f = fMAX= 1/tCYC

10-ns cycle, 100 MHz

ISB1

Automatic CE

Max. VDD, Device Deselected, 7.5-ns cycle, 133 MHz

Power-Down

Current—TTL Inputs

VIN ≥ VIH or VIN ≤ VIL, f = fMAX,

inputs switching

10-ns cycle, 100 MHz

ISB2

Automatic CE

Max. VDD, Device Deselected, All speeds

Power-Down

VIN ≥ VDD – 0.3V or VIN ≤ 0.3V,

Current—CMOS Inputs f = 0, inputs static

ISB3

Automatic CE

Max. VDD, Device Deselected, 7.5-ns cycle, 133 MHz

Power-down

VIN ≥ VDDQ – 0.3V or

Current—CMOS Inputs VIN ≤ 0.3V,

10-ns cycle, 100 MHz

f = fMAX, inputs switching

ISB4

Automatic CE

Max. VDD, Device Deselected, All speeds

Power-down

VIN ≥ VDD – 0.3V or VIN ≤ 0.3V,

Current—TTL Inputs f = 0, inputs static

Min.

3.135

2.375

2.4

2.0

2.0

1.7

–0.3

–0.3

−5

–30

–5

–5

Max. Unit

3.6

V

VDD

V

V

V

0.4

V

0.4

V

VDD + 0.3V V

VDD + 0.3V V

0.8

V

0.7

V

5

µA

µA

5

µA

µA

30

µA

5

µA

225 mA

205 mA

90

mA

80

mA

40

mA

75

mA

65

mA

45

mA

Notes:

7. Overshoot: VIH(AC) < VDD +1.5V (Pulse width less than tCYC/2), undershoot: VIL(AC) > –2V (Pulse width less than tCYC/2).

8. TPower-up: Assumes a linear ramp from 0V to VDD(min.) within 200 ms. During this time VIH < VDD and VDDQ < VDD.

Document #: 38-05518 Rev. *D

Page 7 of 16