VP531ECG データシートの表示(PDF) - Zarlink Semiconductor Inc

部品番号

コンポーネント説明

メーカー

VP531ECG Datasheet PDF : 17 Pages

| |||

VP531E/VP551E

TIMING INFORMATION

Parameters

Master clock frequency (PXCK input)

PXCK pulse width, HIGH

PXCK pulse width, LOW

PXCK rise time

PXCK fall time

PD7-0 set up time

PD7-0 hold time

SC_SYNC set up time

SC_SYNC hold time

PAL_ID set up time

PAL_ID hold time

PAL_ID duration

Conditions

10% to 90% points

90% to 10% points

Output delay

PXCK to COMPSYNC

PXCK to CLAMP

Note: Timing reference points are at the 50% level. Digital CLOAD <40pF.

Symbol

fPXCK

tPWH; PXCK

tPWL; PXCK

tRP

tFP

tSU;PD

tHD;PD

tSU;SC_SYNC

tHD;SC_SYNC

tSU;PAL_ID

tHD;PAL_ID

tDUR;PAL_ID

tDOS

Min.

10

14.5

10

5

10

0

10

0

9

Typ.

27.0

Max.

TBD

TBD

25

Units

MHz

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

PXCK

periods

ns

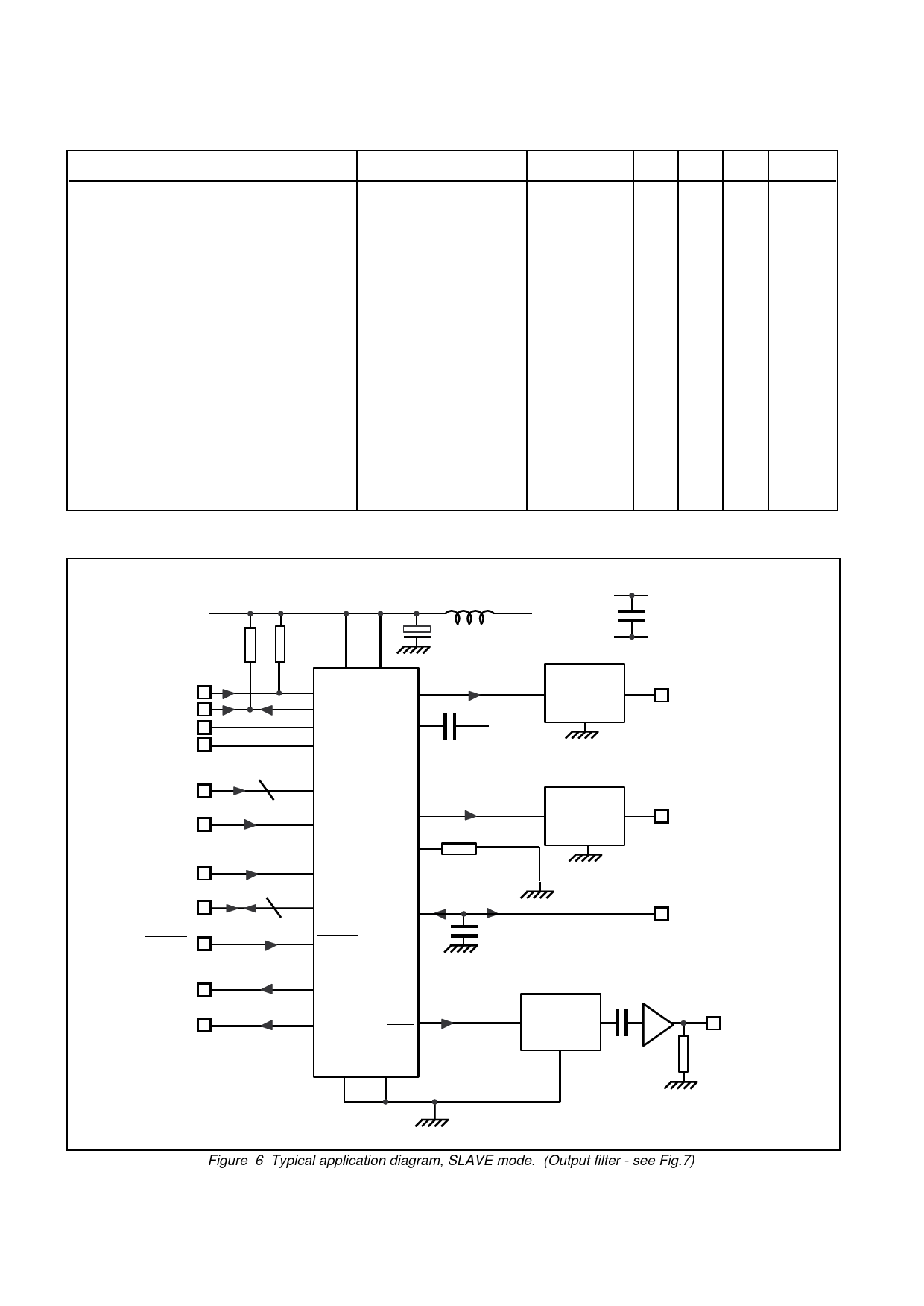

2k2Ω

I2C

BUS

SCL

SDA

SA1

SA2

FERRITE

BEAD +5V

2k2Ω

100µF

VDD, AVDD

28

30

26

SCL

SDA

SA1

LUMA 54

OUT

COMP 52

27 SA2

100nF+5V

10nF

OUTPUT

FILTER

VIDEO IN

REFSQ

PXCK

GPP

RESET

CLAMP

COMP

SYNC

39-46 PD0-7

8

CHROMA 58

35

REFSQ

OUT

DAC 51 769Ω

GAIN

15 PXCK

3-10 D0-7

8

34 RESET

50

VREF

100nF

OUTPUT

FILTER

17

CLAMP

18 COMP

SYNC

COMP 56

OUT

GND, AGND

OUTPUT

FILTER

VDD

AT EVERY

VDD PIN

GND

LUMAOUT

CHROMAOUT

VREF

-1

COMPOSITE

OUT

75Ω

GND

Figure 6 Typical application diagram, SLAVE mode. (Output filter - see Fig.7)

12