XWM8739LEFL データシートの表示(PDF) - Wolfson Microelectronics plc

部品番号

コンポーネント説明

メーカー

XWM8739LEFL Datasheet PDF : 35 Pages

| |||

WM8739 / WM8739L

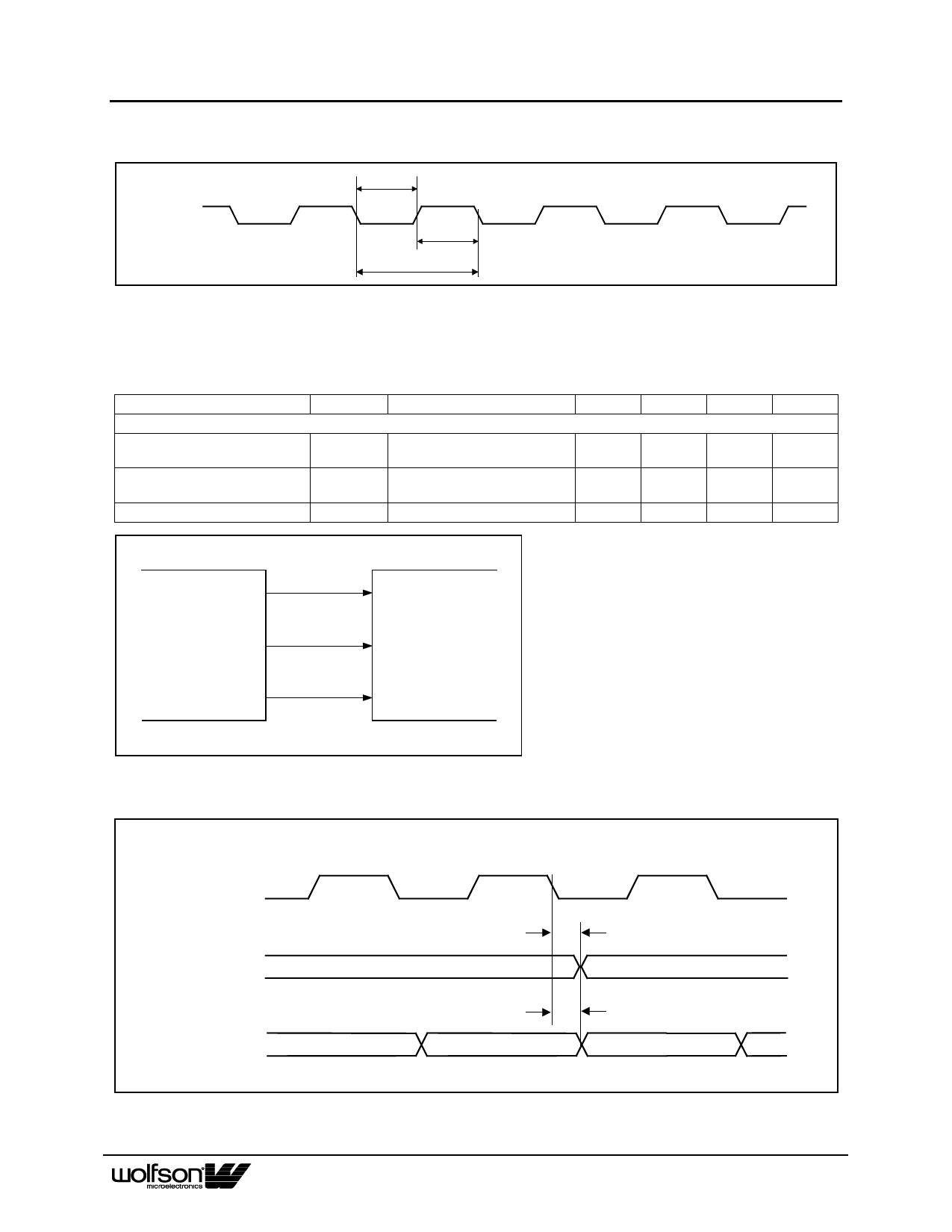

DIGITAL AUDIO INTERFACE TIMING

XTI/MCLK

tXTIL

tXTIH

tXTIY

Advanced Information

Figure 1 System Clock Timing Requirements

Test Conditions

AVDD, DBVDD = 3.3V, AGND = 0V, DCVDD = 3.3V, DGND = 0V, TA = +25oC, Slave Mode fs = 48kHz, XTI/MCLK = 256fs

unless otherwise stated.

PARAMETER

SYMBOL

System Clock Timing Information

XTI/MCLK System clock pulse width

high

TXTIH

XTI/MCLK System clock pulse width

low

TXTIL

XTI/MCLK System clock cycle time

TXTIY

TEST CONDITIONS

MIN

TYP

MAX

UNIT

20

ns

20

ns

50

ns

BCLK

WM8739

ADC ADCLRC

ADCDAT

DSP

ENCODER

Figure 2 Master Mode Connection

BCLK

(Output)

ADCLRC

(Output)

ADCDAT

Figure 3 Digital Audio Data Timing – Master Mode

tDL

tDDA

AI Rev 2.2 September 2001

7