EP1C12Q173I8 데이터 시트보기 (PDF) - Altera Corporation

부품명

상세내역

제조사

EP1C12Q173I8 Datasheet PDF : 104 Pages

| |||

Cyclone Device Handbook, Volume 1

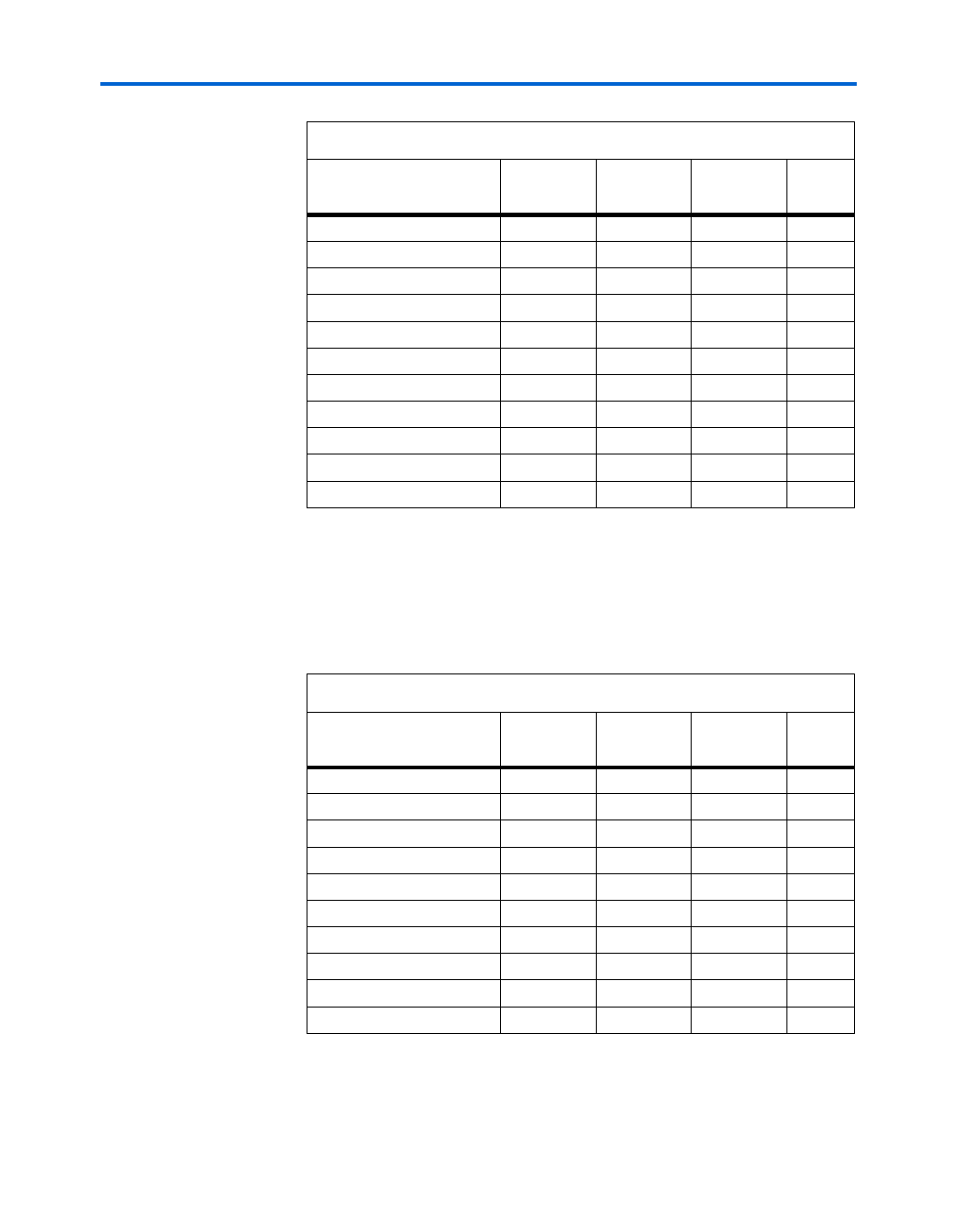

Table 4–49. Cyclone Maximum Input Clock Rate for Row Pins

I/O Standard

LVTTL

2.5 V

1.8 V

1.5 V

LVCMOS

SSTL-3 class I

SSTL-3 class II

SSTL-2 class I

SSTL-2 class II

3.3-V PCI (1)

LVDS

-6 Speed

Grade

464

392

387

387

405

405

414

464

473

464

567

-7 Speed

Grade

428

302

311

320

374

356

365

428

432

428

549

-8 Speed

Grade

387

207

252

243

333

293

302

396

396

387

531

Unit

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

Note to Tables 4–48 through 4–49:

(1) EP1C3 devices do not support the PCI I/O standard. These parameters are only

available on row I/O pins.

Tables 4–50 and 4–51 show the maximum output clock rate for column

and row pins in Cyclone devices.

Table 4–50. Cyclone Maximum Output Clock Rate for Column Pins

I/O Standard

LVTTL

2.5 V

1.8 V

1.5 V

LVCMOS

SSTL-3 class I

SSTL-3 class II

SSTL-2 class I

SSTL-2 class II

LVDS

-6 Speed

Grade

304

220

213

166

304

100

100

134

134

320

-7 Speed

Grade

304

220

213

166

304

100

100

134

134

320

-8 Speed

Grade

304

220

213

166

304

100

100

134

134

275

Note to Table 4–50:

(1) EP1C3 devices do not support the PCI I/O standard.

Unit

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

MHz

4–28

Preliminary

Altera Corporation

January 2007