74AHC74 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

제조사

74AHC74 Datasheet PDF : 20 Pages

| |||

Philips Semiconductors

Dual D-type flip-flop with set and reset;

positive-edge trigger

Product specification

74AHC74; 74AHCT74

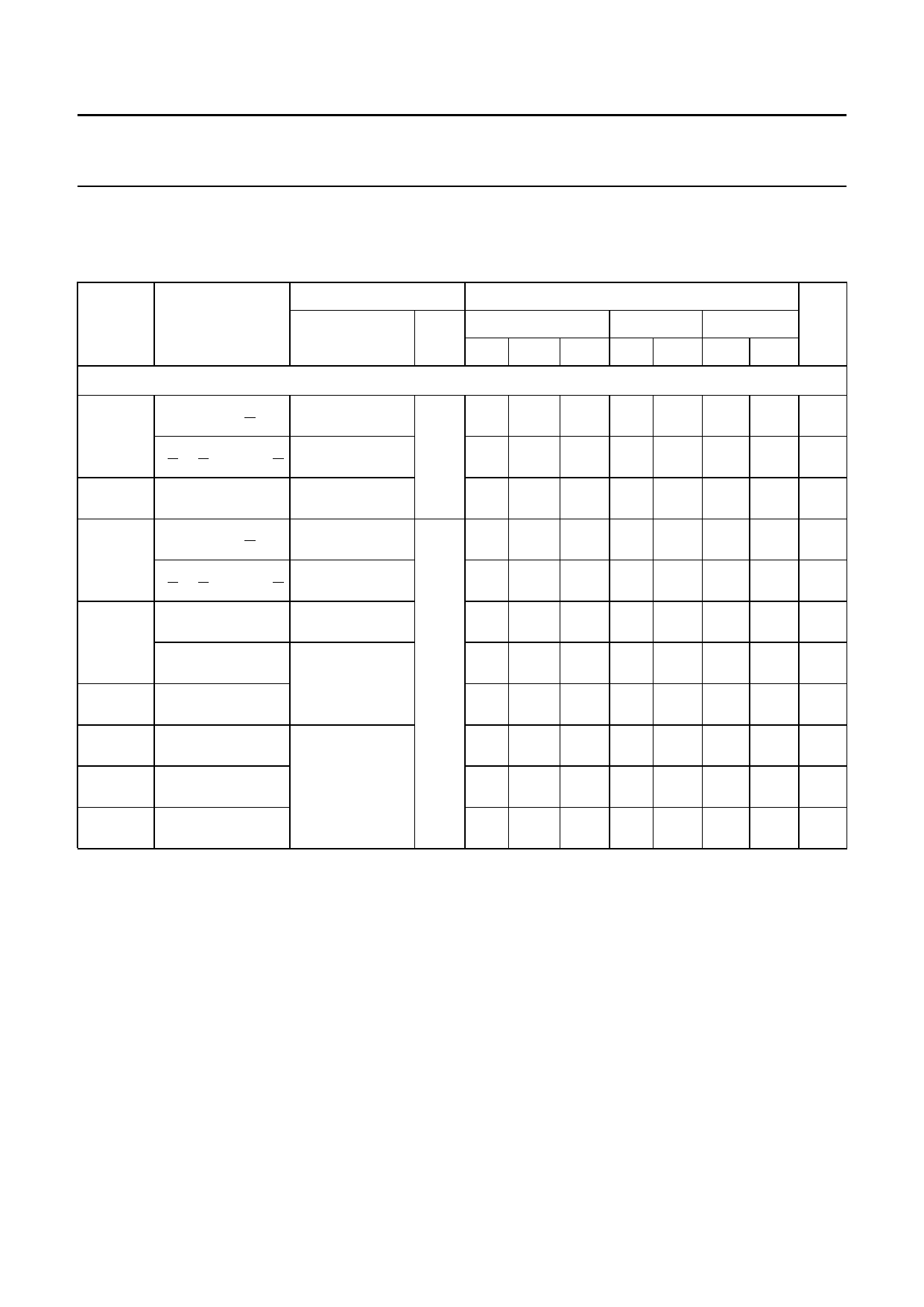

AC CHARACTERISTICS

Type 74AHC74

GND = 0 V; tr = tf ≤ 3.0 ns.

SYMBOL PARAMETER

TEST CONDITIONS

WAVEFORMS CL

Tamb (°C)

25

−40 to +85 −40 to +125 UNIT

MIN. TYP. MAX. MIN. MAX. MIN. MAX.

VCC = 3.0 to 3.6 V; note 1

tPHL/tPLH propagation delay see Figs 6 and 8 15 pF −

5.2

nCP to nQ, nQ

propagation delay see Figs 7 and 8

nSD nRD to nQ, nQ

fmax

maximum clock

pulse frequency

− 5.4

80 125

tPHL/tPLH propagation delay see Figs 6 and 8 50 pF −

7.4

nCP to nQ, nQ

propagation delay see Figs 7 and 8

nSD nRD to nQ, nQ

tW

clock pulse width see Figs 6 and 8

HIGH or LOW

− 7.7

6.0 −

set or reset pulse see Figs 7 and 8

width LOW

6.0 −

trem

removal time set or

reset

5.0 −

tsu

set-up time

see Figs 6 and 8

nD to nCP

6.0 −

th

hold time

nD to nCP

0.5 −

fmax

maximum clock

pulse frequency

50 75

11.9 1.0 14.0 1.0

12.3 1.0 14.5 1.0

−

45 −

45

15.4 1.0 17.5 1.0

15.8 1.0 18.0 1.0

−

7.0 −

7.0

−

7.0 −

7.0

−

5.0 −

5.0

−

7.0 −

7.0

−

0.5 −

0.5

−

70 −

70

15.0 ns

15.5 ns

−

ns

19.5 ns

20.0 ns

−

ns

−

ns

−

ns

−

ns

−

ns

−

ns

1999 Sep 23

8