CY7C027-15AI 데이터 시트보기 (PDF) - Cypress Semiconductor

부품명

상세내역

제조사

CY7C027-15AI Datasheet PDF : 18 Pages

| |||

PRELIMINARY

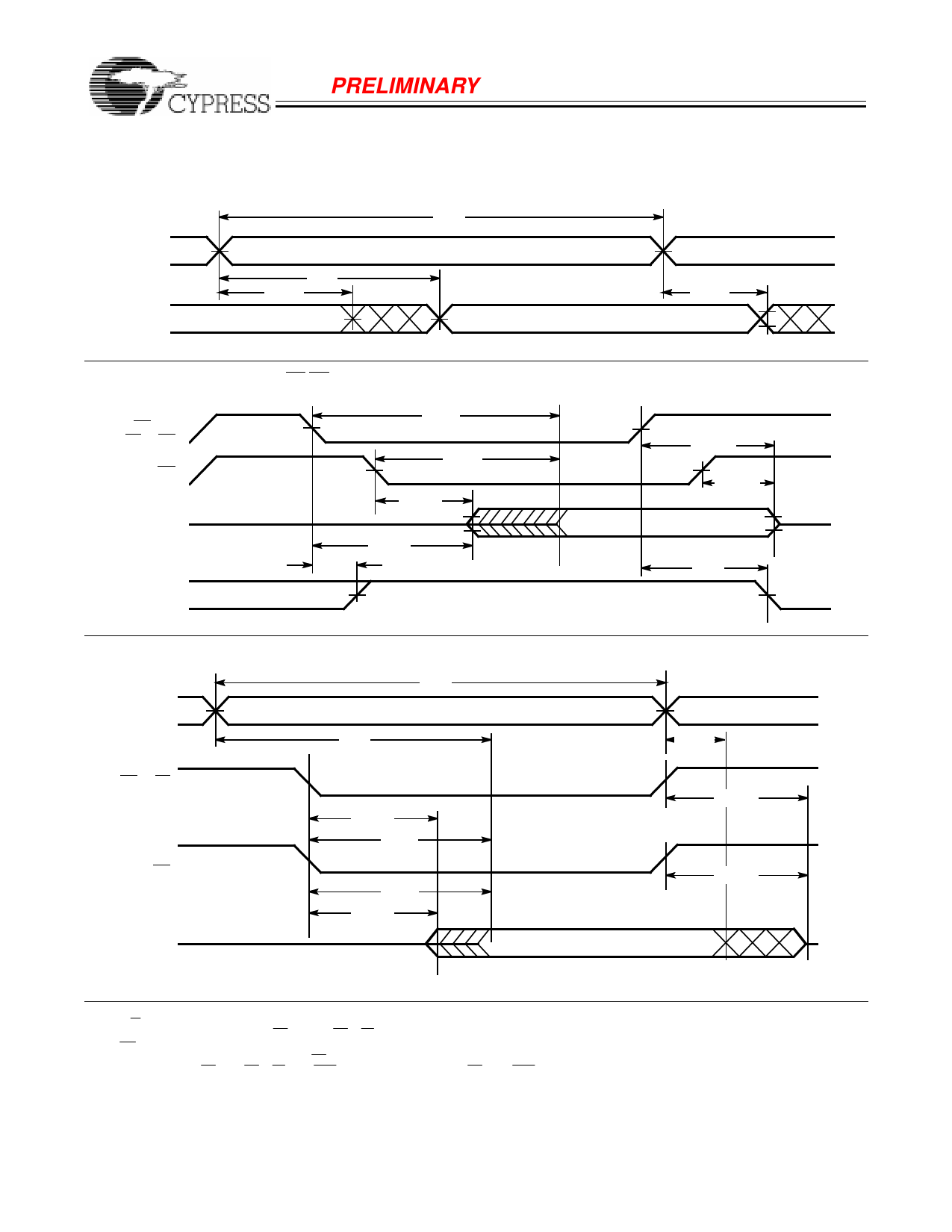

Switching Waveforms

Read Cycle No. 1 (Either Port Address Access)[21,22,23]

tRC

ADDRESS

DATA OUT

tAA

tOHA

PREVIOUS DATA VALID

Read Cycle No. 2 (Either Port CE/OE Access)[21,24,25]

CE and

LB or UB

OE

DATA OUT

ICC

CURRENT

ISB

tACE

tDOE

tLZOE

tLZCE

tPU

Read Cycle No. 3 (Either Port)[21,23,24,25]

tRC

ADDRESS

tAA

UB or LB

CE

DATA OUT

tLZCE

tABE

tACE

tLZCE

CY7C027/028

CY7C037/038

DATA VALID

tOHA

tHZCE

tHZOE

DATA VALID

tPD

tOHA

tHZCE

tHZCE

Notes:

21. R/W is HIGH for read cycles.

22. Device is continuously selected CE = VIL and UB or LB = VIL. This waveform cannot be used for semaphore reads.

23. OE = VIL.

24. Address valid prior to or coincident with CE transition LOW.

25. To access RAM, CE = VIL, UB or LB = VIL, SEM = VIH. To access semaphore, CE = VIH, SEM = VIL.

9