SAB9077 데이터 시트보기 (PDF) - Philips Electronics

부품명

상세내역

제조사

SAB9077 Datasheet PDF : 32 Pages

| |||

Philips Semiconductors

Picture-In-Picture (PIP) controller

Preliminary specification

SAB9077H

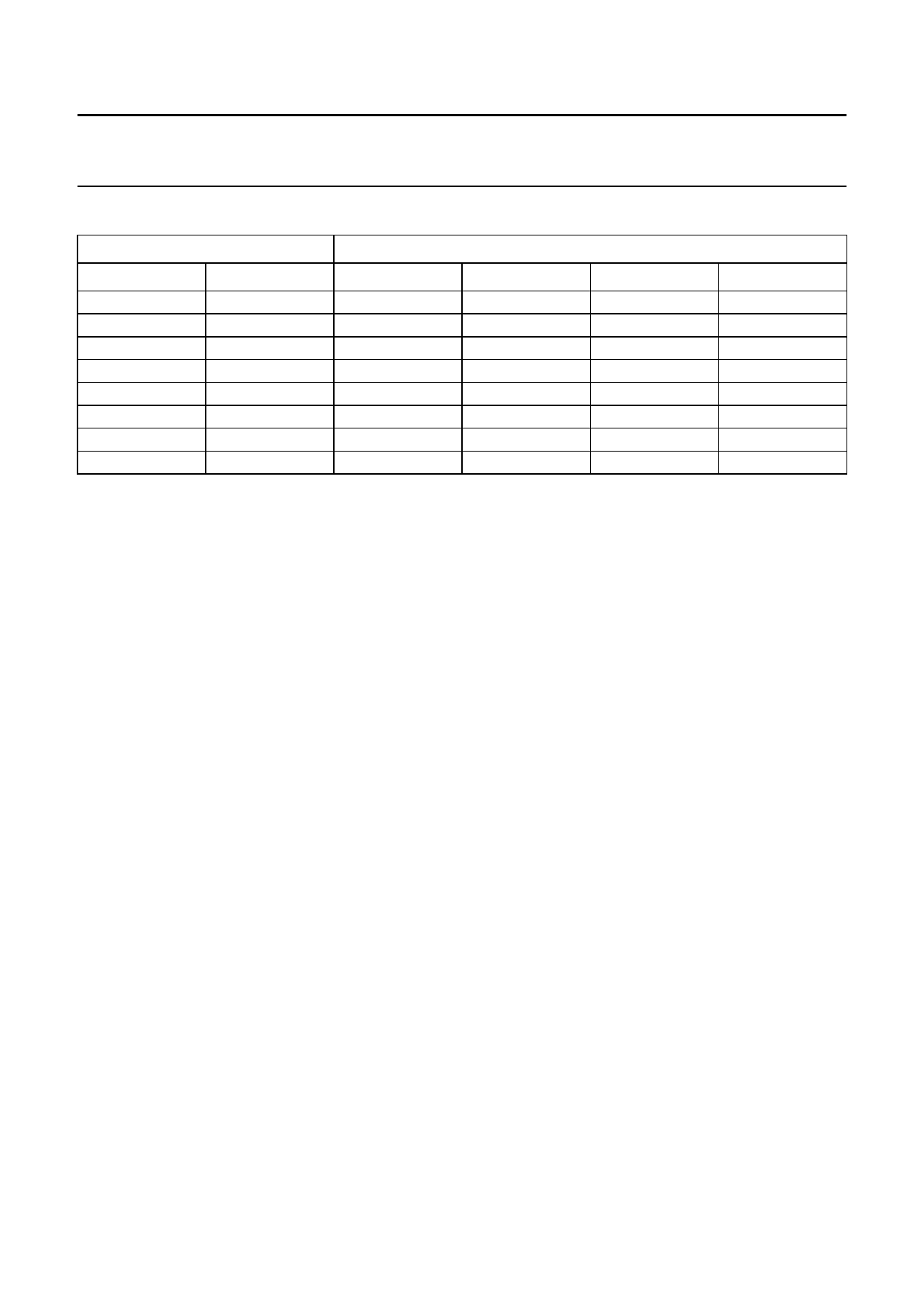

Table 5 Colour types and brightness levels

COLOUR TYPE

COLOUR

Black

Blue

Red

Magenta

Green

Cyan

Yellow

White

VALUE

0H

1H

2H

3H

4H

5H

6H

7H

4H

0%

30%

30%

30%

30%

30%

30%

60%

BRIGHTNESS LEVEL

5H

6H

10%

50%

50%

50%

50%

50%

50%

70%

30%

70%

70%

70%

70%

70%

70%

80%

7H

50%

100%

100%

100%

100%

100%

100%

100%

Table 5 indicates how I2C-bus register settings control the

colour and brightness. All colour registers are similar, they

contain one on/off bit, two brightness bits and three colour

type bits. To determine which colour is visible in the event

two or more colours being displayed on the same position,

the next priority scheme is followed:

1. Sub-select colour (SBS)

2. Sub-border colour (SB)

3. Main-select colour (MBS)

4. Main-border colour (MB)

5. Background colour (BG).

SA 15H AND SA 16H DECODER REGISTERS

The MVFILT and SVFILT bits can set the type of vertical

filtering. The MUVPOL and SUVPOL bits invert the UV

polarity of the incoming signals. The MVSPOL and

SVSPOL bits determine the active edge of the Vsync (see

Fig.7). The MHSYNC and SHSYNC bits determine the

timing of the Hsync pulse (burstkey or Hsync timing).

The MFPOL and SFPOL bits can invert the field

identification (ID) of the incoming fields (see Fig.7).

SA 17H DISPLAY SETTINGS REGISTER

The FBDEL bits can adjust the fast blank delay in 8 steps

of 1⁄2 a clock cycle (−8 to +7). 0H is mid-scale.

The DUVPOL bit inverts the UV polarity of the border

colours.

The DVSPOL bit determines the active edge of the Vsync

(see Fig.7). The DHSYNC bit determines the timing of the

Hsync pulse (burstkey or Hsync). The DFPOL bit can invert

the field ID of the incoming fields (see Fig.7).

SA 18H PEDESTAL SETTINGS REGISTER

The PEDESTU and PEDESTV bits give the U and V DAC

outputs an offset of −8 to +7 LSB when the FBL is

switched off. This can be used to adjust the White point of

the system.

1996 Aug 07

18