LPC47N267(2000) 데이터 시트보기 (PDF) - SMSC -> Microchip

부품명

상세내역

제조사

LPC47N267 Datasheet PDF : 180 Pages

| |||

11.6

11.7

12.0

12.1

12.2

12.3

12.4

12.5

12.6

12.7

12.8

13.0

13.1

13.2

14.0

14.1

14.2

14.3

14.4

15.0

15.1

16.0

16.1

16.2

16.3

16.4

16.5

17.0

17.1

18.0

18.1

19.0

19.1

19.2

20.0

20.1

20.2

20.3

20.4

20.5

20.6

21.0

21.1

21.2

22.0

23.0

24.0

24.1

24.2

ECP IMPLEMENTATION STANDARD .................................................................................................................80

PARALLEL PORT FLOPPY DISK CONTROLLER ...................................................................................................88

POWER MANAGEMENT ..............................................................................................................................90

FDC POWER MANAGEMENT...........................................................................................................................90

DSR FROM POWERDOWN..............................................................................................................................90

WAKE UP FROM AUTO POWERDOWN ..............................................................................................................90

REGISTER BEHAVIOR.....................................................................................................................................90

PIN BEHAVIOR ..............................................................................................................................................91

UART POWER MANAGEMENT ........................................................................................................................92

EXIT AUTO POWERDOWN...............................................................................................................................92

PARALLEL PORT ...........................................................................................................................................92

SERIAL IRQ ..................................................................................................................................................93

TIMING DIAGRAMS FOR SER_IRQ CYCLE.......................................................................................................93

ROUTABLE IRQ INPUTS .................................................................................................................................95

PCI CLKRUN SUPPORT ..............................................................................................................................96

OVERVIEW ...................................................................................................................................................96

NCLKRUN FOR SERIAL IRQ .........................................................................................................................96

NCLKRUN FOR LDRQ# ...............................................................................................................................96

USING NCLKRUN ........................................................................................................................................96

X-BUS INTERFACE ......................................................................................................................................98

X-BUS MODES..............................................................................................................................................99

GENERAL PURPOSE I/O ...........................................................................................................................102

GPIO PINS ................................................................................................................................................102

DESCRIPTION..............................................................................................................................................103

GPIO CONTROL .........................................................................................................................................104

GPIO OPERATION ......................................................................................................................................104

GPIO PME AND SMI FUNCTIONALITY...........................................................................................................105

SYSTEM MANAGEMENT INTERRUPT (SMI)............................................................................................106

SMI REGISTERS .........................................................................................................................................106

PME SUPPORT...........................................................................................................................................106

PME REGISTERS ........................................................................................................................................107

RUNTIME REGISTERS...............................................................................................................................107

RUNTIME REGISTERS BLOCK SUMMARY ........................................................................................................107

RUNTIME REGISTERS BLOCK DESCRIPTION ...................................................................................................108

CONFIGURATION ......................................................................................................................................113

CONFIGURATION ACCESS PORTS..................................................................................................................113

CONFIGURATION STATE ...............................................................................................................................113

CONFIGURATION REGISTERS SUMMARY ........................................................................................................114

CONFIGURATION REGISTERS DESCRIPTION ...................................................................................................116

LOGICAL DEVICE BASE I/O ADDRESS AND RANGE ..........................................................................................148

NOTE A. LOGICAL DEVICE IRQ AND DMA OPERATION ...................................................................................150

OPERATIONAL DESCRIPTION .................................................................................................................151

MAXIMUM GUARANTEED RATINGS.................................................................................................................151

DC ELECTRICAL CHARACTERISTICS ..............................................................................................................151

TIMING DIAGRAMS....................................................................................................................................154

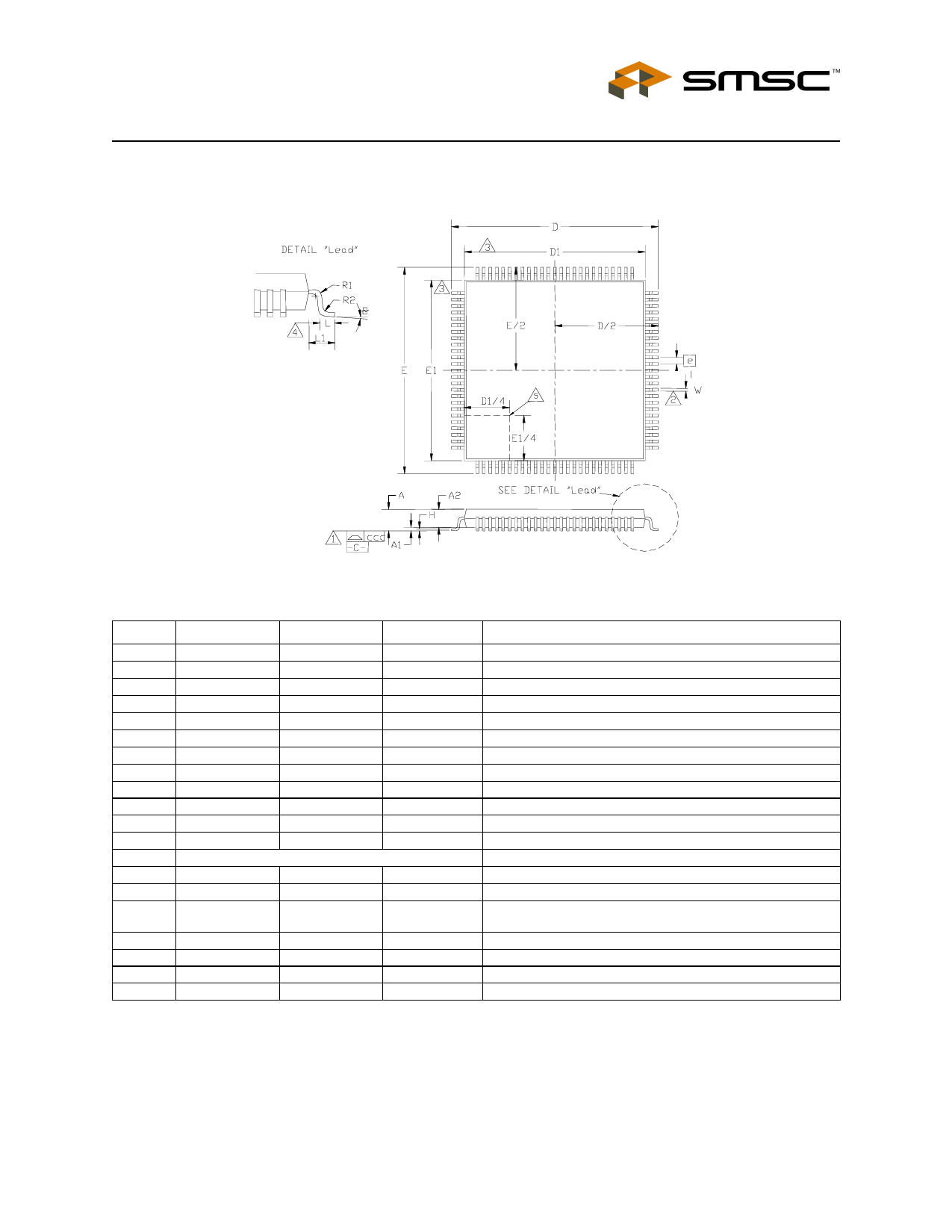

PACKAGE OUTLINES................................................................................................................................178

APPENDIX - TEST MODES ........................................................................................................................179

BOARD TEST MODE.....................................................................................................................................179

XNOR-CHAIN TEST MODE ..........................................................................................................................179

SMSC DS – LPC47N267

Page 5

Rev. 10/23/2000