MC14539B 데이터 시트보기 (PDF) - Motorola => Freescale

부품명

상세내역

제조사

MC14539B Datasheet PDF : 6 Pages

| |||

ÎÎÎÎSÎÎÎÎWIÎÎÎÎTCHÎÎÎÎINGÎÎÎÎCHÎÎÎÎARÎÎÎÎAChCaÎÎÎÎTrEacRtÎÎÎÎeISriTsÎÎÎÎtIiCcSÎÎÎÎ* (CÎÎÎÎL=5ÎÎÎÎ0pFÎÎÎÎ,TAÎÎÎÎ=2ÎÎÎÎ5_CÎÎÎÎ)SymÎÎÎÎbolÎÎÎÎÎÎÎÎVÎÎÎÎDDÎÎÎÎÎÎÎÎÎÎÎÎMinÎÎÎÎÎÎÎÎTÎÎÎÎypÎÎÎÎ# ÎÎÎÎÎÎÎÎMaxÎÎÎÎÎÎÎÎUÎÎÎÎnitÎÎÎÎ

Output Rise and Fall Time

tTLH, tTHL = (1.5 ns/pF) CL + 25 ns

tTLH, tTHL = (0.75 ns/pF) CL + 12.5 ns

tTLH, tTHL = (0.55 ns/pF) CL + 9.5 ns

tTLH,

ns

tTHL

5.0

—

100

200

10

—

50

100

15

—

40

80

Propagation Delay Time

X, Y Input to Output

tPLH, tPHL = (1.7 ns/pF) CL + 125 ns

tPLH, tPHL = (0.66 ns/pF) CL + 57 ns

tPLH, tPHL = (0.55 ns/pF) CL + 45 ns

tPLH,

ns

tPHL

5.0

—

210

420

10

—

90

180

15

—

70

140

A Input to Output

tPLH = (1.7 ns/pF) CL + 140 ns

tPLH = (0.66 ns/pF) CL + 77 ns

tPLH = (0.5 ns/pF) CL + 60 ns

tPLH

ns

5.0

—

225

450

10

—

110

220

15

—

85

170

tPHL = (1.7 ns/pF) CL + 160 ns

tPHL = (0.66 ns/pF) CL + 82 ns

tPHL = (0.5 ns/pF) CL + 65 ns

tPHL

5.0

—

245

490

ns

10

—

115

230

15

—

90

180

Strobe Input to Output

tPLH, tPHL = (1.7 ns/pF) CL + 60 ns

tPLH, tPHL = (0.66 ns/pF) CL + 42 ns

tPLH, tPHL = (0.5 ns/pF) CL + 35 ns

tPLH,

ns

tPHL

5.0

—

145

290

10

—

75

150

15

—

60

120

* The formulas given are for the typical characteristics only at 25_C.

#Data labelled “Typ” is not to be used for design purposes but is intended as an indication of the IC’s potential performance.

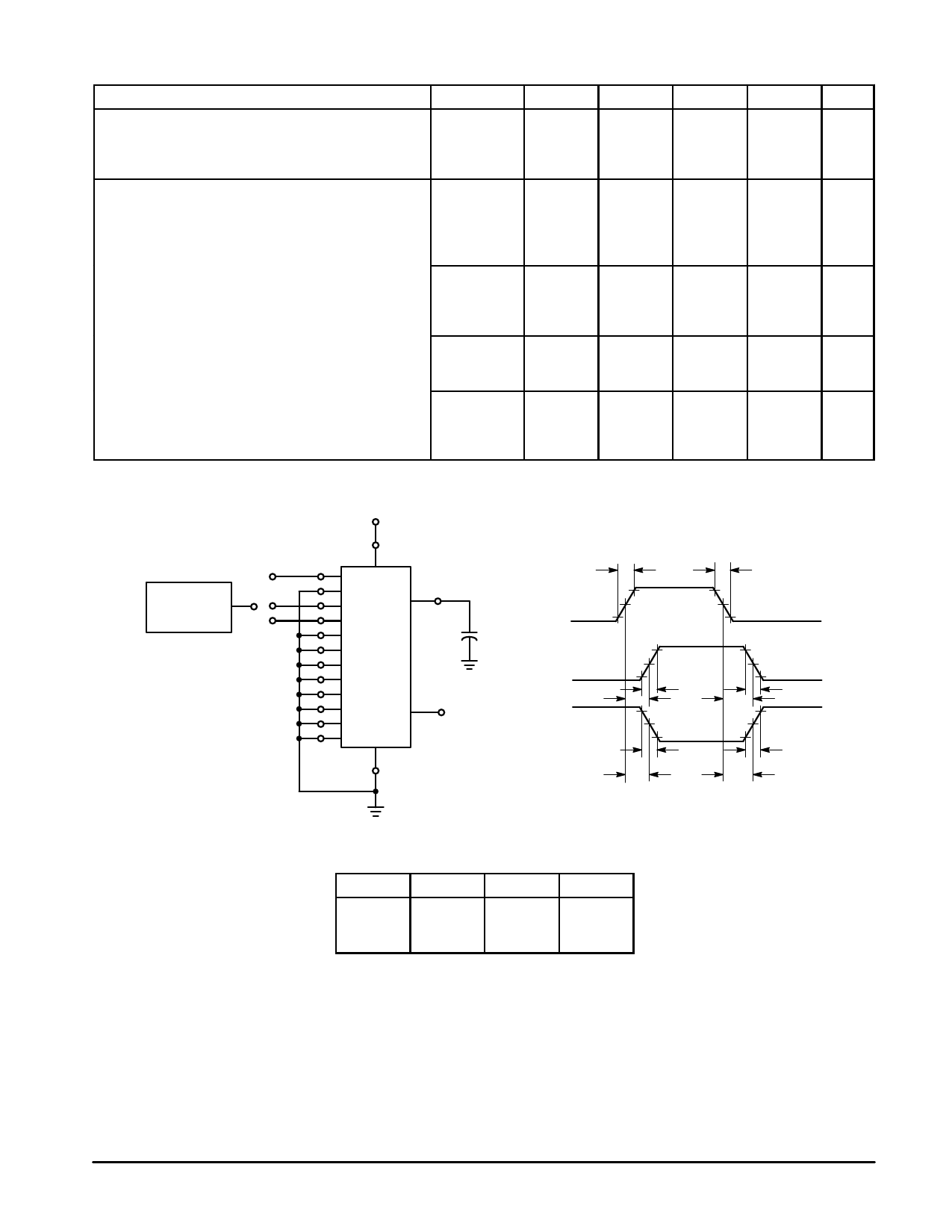

VDD

PULSE

GENERATOR

A

B

ST

Z

X0

X1

X2

X3

ST′

Y0

Y1

W

Y2

Y3

VSS

20 ns

INPUT

CL

OUTPUT

(TEST 1)

tPLH

OUTPUT

(TESTS 2 AND 3)

tPHL

20 ns

tTLH

tTHL

tPHL

tTHL

tTLH

tPLH

INPUT CONNECTIONS FOR tTLH, tTHL, tPHL, tPLH

Test

Strobe

A

1

Gnd

Gnd

2

P.G.

Gnd

3

Gnd

P.G.

X0

P.G.

VDD

VDD

Figure 1. AC Test Circuit and Waveforms

MOTOROLA CMOS LOGIC DATA

MC14539B

3