ST8016 데이터 시트보기 (PDF) - Sitronix Technology Co., Ltd.

부품명

상세내역

제조사

ST8016 Datasheet PDF : 28 Pages

| |||

ST8016

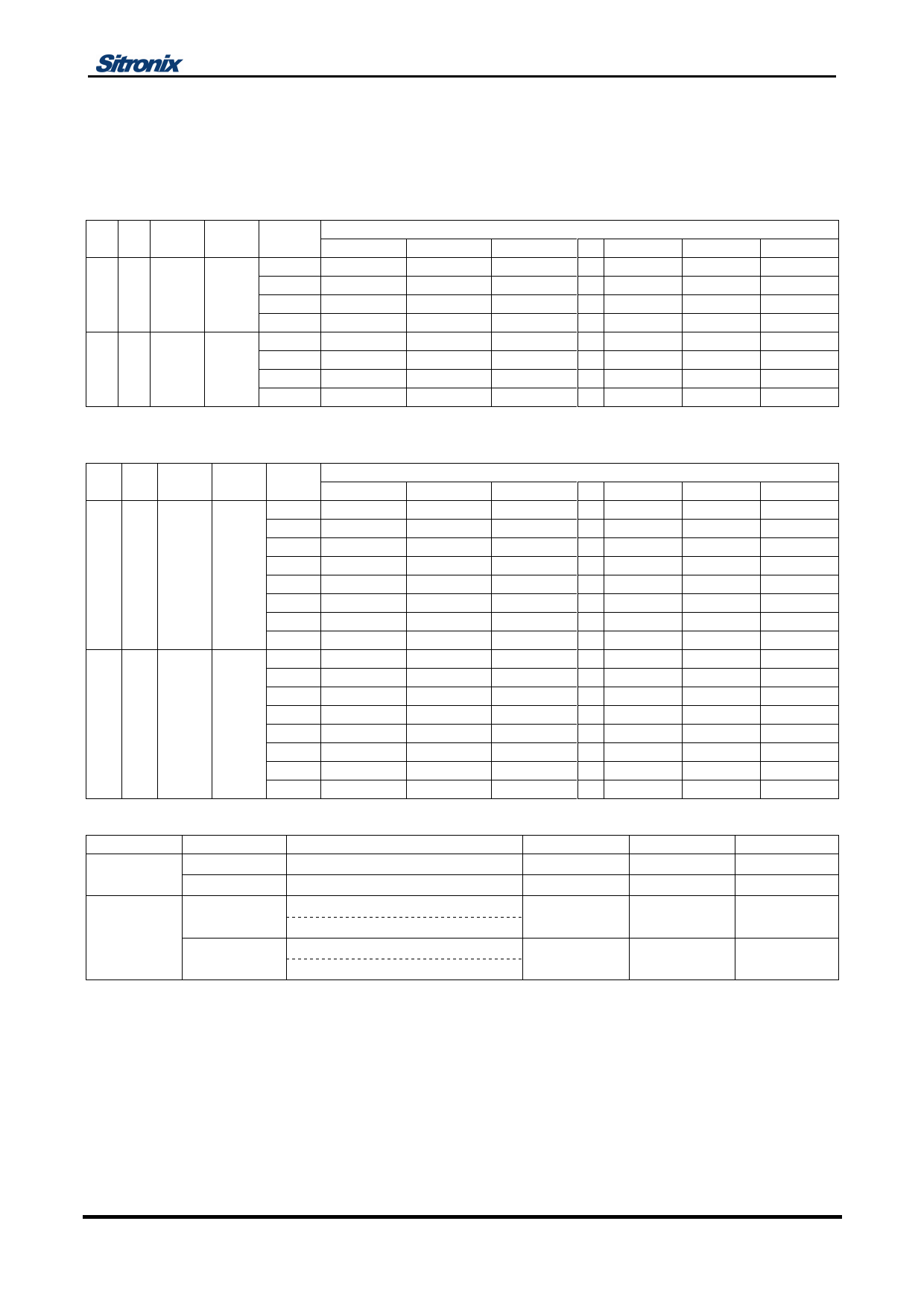

8.2.2 Relationship between the Display Data and LCD Drive Output Pins

(Segment Mode)

(a) 4-bit Parallel Input Mode

MD L/R EIO1 EIO2

L L Output Input

L H Input Output

DATA

INPUT

DI0

Dl1

DI2

DI3

DI0

Dl1

DI2

DI3

40 CLOCK 39 CLOCK

Y1

Y5

Y2

Y6

Y3

Y7

Y4

Y8

Y160

Y156

Y159

Y155

Y158

Y154

Y157

Y153

NUMBER OF CLOCKS

38 CLOCK … 3 CLOCK

Y9

…

Y149

Y10

…

Y150

Y11

…

Y151

Y12

…

Y152

Y152

…

Y12

Y151

…

Y11

Y150

…

Y10

Y149

…

Y9

2 CLOCK

Y153

Y154

Y155

Y156

Y8

Y7

Y6

Y5

1 CLOCK

Y157

Y158

Y159

Y160

Y4

Y3

Y2

Y1

(b) 8-bit Parallel Input Mode

MD L/R EIO1

EIO2

DATA

NUMBER OF CLOCKS

INPUT 20 CLOCK 19 CLOCK 18 CLOCK … 3 CLOCK 2 CLOCK 1 CLOCK

DI0

Y1

Dl1

Y2

DI2

Y3

H

L Output Input

DI3

DI4

Y4

Y5

Y9

Y17

…

Y137

Y145

Y153

Y10

Y18

…

Y138

Y146

Y154

Y11

Y19

…

Y139

Y147

Y155

Y12

Y20

…

Y140

Y148

Y156

Y13

Y21

Y141

Y149

Y157

DI5

Y6

Y14

Y22

Y142

Y150

Y158

DI6

Y7

Y15

Y23

Y143

Y151

Y159

DI7

DI0

Dl1

DI2

H

H

Input Output

DI3

DI4

Dl5

DI6

DI7

Y8

Y160

Y159

Y158

Y157

Y156

Y155

Y154

Y153

Y16

Y152

Y151

Y150

Y149

Y148

Y147

Y146

Y145

Y24

Y144

Y144

…

Y24

Y143

…

Y23

Y142

…

Y22

Y141

…

Y21

Y140

…

Y20

Y139

…

Y19

Y138

…

Y18

Y137

…

Y17

Y152

Y16

Y15

Y14

Y13

Y12

Y11

Y10

Y9

Y160

Y8

Y7

Y6

Y5

Y4

Y3

Y2

Y1

(Common Mode)

MD

L

(Single)

L/R

DATA TRANSFER DIRECTION

L

Y160 → Y1

H

Y1 → Y160

H

L

(Dual)

H

Y160 →

Y80 →

Y1 →

Y81 →

Y81

Y1

Y80

Y160

NOTES:

Ÿ L : VSS (0 V), H : VDD (+2.5 to +5.5 V), X : Don't care

Ÿ "Don't care" should be fixed to "H" or "L", avoiding floating.

EIO1

Output

Input

Output

Input

EIO2

Input

Output

Input

Output

DI7

X

X

Input

Input

Ver 2.0

Page 10/28

2008/05/07