TC74VHC273F 데이터 시트보기 (PDF) - Toshiba

부품명

상세내역

제조사

TC74VHC273F Datasheet PDF : 10 Pages

| |||

TC74VHC273F/FT/FK

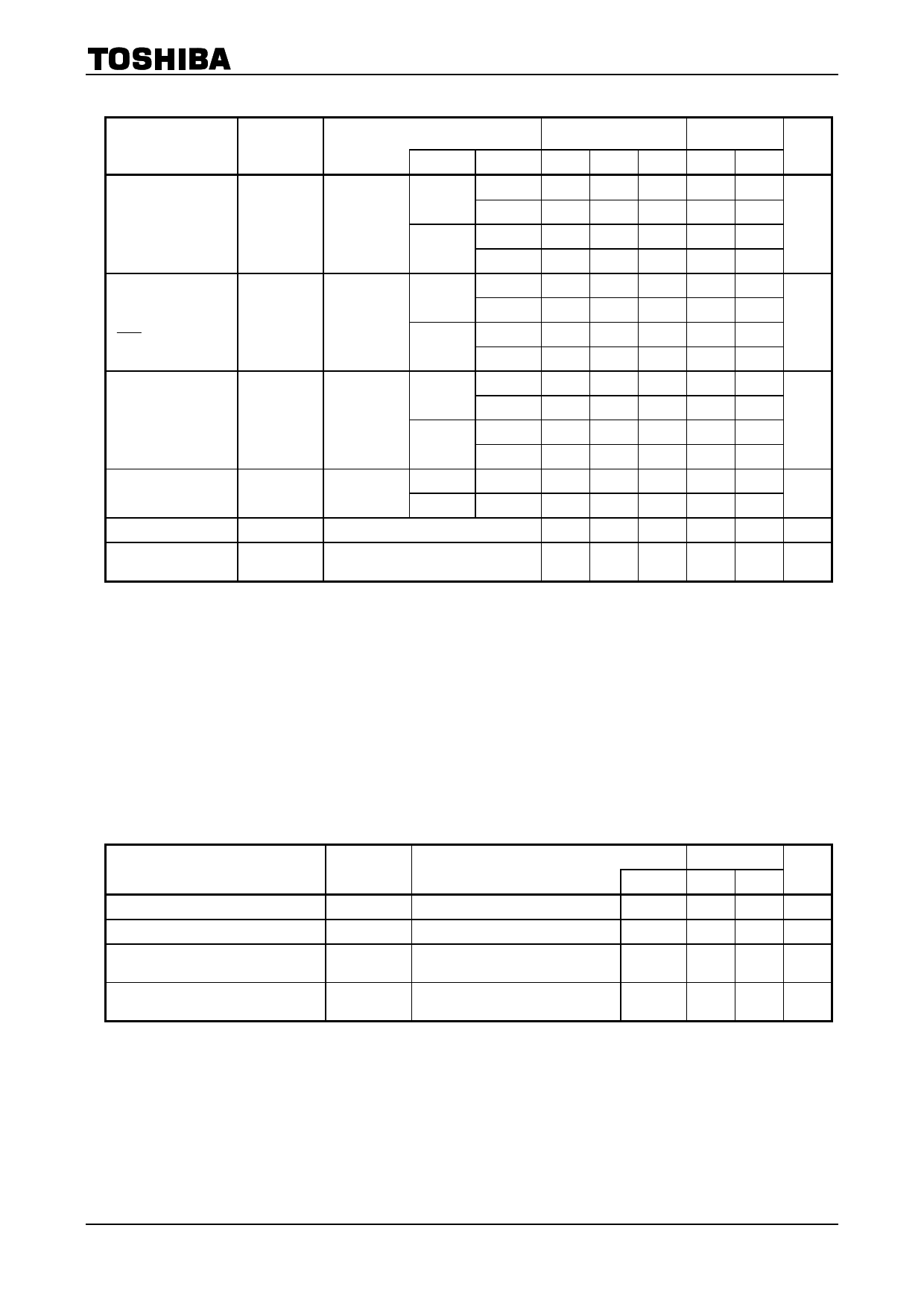

AC Characteristics (input: tr = tf = 3 ns)

Characteristics

Symbol

Propagation delay

time

tpLH

(CK-Q)

tpHL

Propagation delay

time

tpHL

( CLR -Q)

Maximum clock

frequency

fmax

Output to output skew

Input capacitance

Power dissipation

capacitance

tosLH

tosHL

CIN

CPD

Test Condition

VCC (V)

3.3 ± 0.3

⎯

5.0 ± 0.5

3.3 ± 0.3

⎯

5.0 ± 0.5

3.3 ± 0.3

⎯

5.0 ± 0.5

3.3 ± 0.3

(Note 1)

5.0 ± 0.5

⎯

CL (pF)

15

50

15

50

15

50

15

50

15

50

15

50

50

50

Ta = 25°C

Min Typ. Max

⎯

8.7 13.6

⎯ 11.2 17.1

⎯

5.8

9.0

⎯

7.3 11.0

⎯

8.9 13.6

⎯ 11.4 17.1

⎯

5.2

8.5

⎯

6.7 10.5

75 120 ⎯

50

75

⎯

120 165 ⎯

80 110 ⎯

⎯

⎯

1.5

⎯

⎯

1.0

⎯

4

10

(Note 2) ⎯

31

⎯

Ta = −40 to

85°C

Min Max

1.0 16.0

1.0 19.5

1.0 10.5

1.0 12.5

1.0 16.0

1.0 19.5

1.0 10.0

1.0 12.0

65

⎯

45

⎯

100

⎯

70

⎯

⎯

1.5

⎯

1.0

⎯

10

⎯

⎯

Unit

ns

ns

MHz

ns

pF

pF

Note 1: Parameter guaranteed by design.

tosLH = |tpLHm − tpLHn|, tosHL = |tpHLm − tpHLn|

Note 2: CPD is defined as the value of the internal equivalent capacitance which is calculated from the operating

current consumption without load.

Average operating current can be obtained by the equation:

ICC (opr) = CPD·VCC·fIN + ICC/8 (per bit)

And the total CPD when n pcs.of flip flop operate can be gained by the following equation:

CPD (total) = 22 + 9·n

Noise Characteristics (input: tr = tf = 3 ns)

Characteristics

Symbol

Quiet output maximum dynamic VOL

Quiet output minimum dynamic VOL

Minimum high level dynamic input

voltage

Maximum low level dynamic input

voltage

VOLP

VOLV

VIHD

VILD

CL = 50 pF

CL = 50 pF

CL = 50 pF

CL = 50 pF

Test Condition

Ta = 25°C

Unit

VCC (V) Typ. Max

5.0

0.5 0.8

V

5.0

−0.5 −0.8

V

5.0

⎯

3.5

V

5.0

⎯

1.5

V

5

2012-08-04