M4A5-384/128-5SAC 데이터 시트보기 (PDF) - Lattice Semiconductor

부품명

상세내역

제조사

M4A5-384/128-5SAC

Lattice Semiconductor

M4A5-384/128-5SAC Datasheet PDF : 63 Pages

| |||

Macrocell

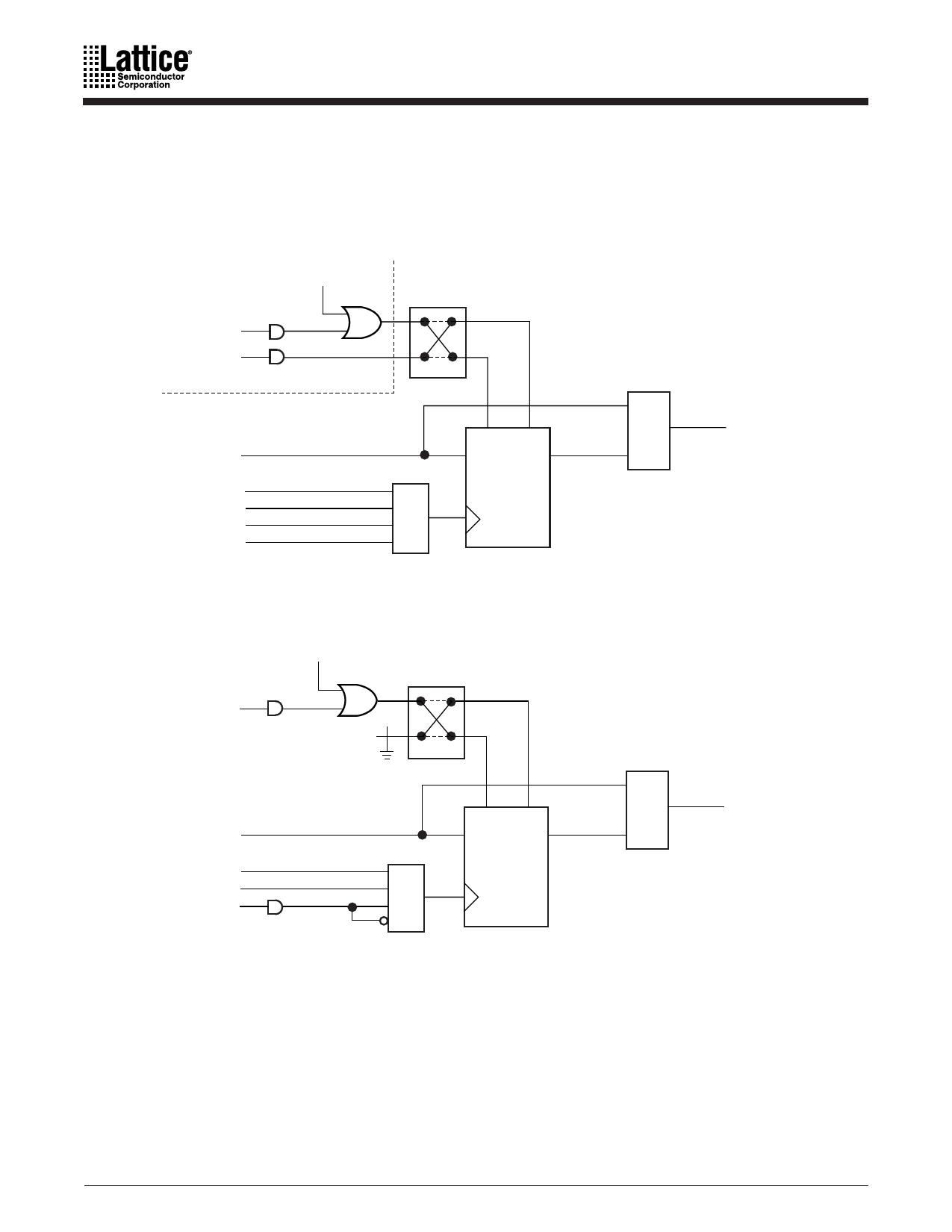

The macrocell consists of a storage element, routing resources, a clock multiplexer, and initialization

control. The macrocell has two fundamental modes: synchronous and asynchronous (Figure 5). The mode

chosen only affects clocking and initialization in the macrocell.

Power-Up

Reset

PAL-Block

Initialization

Product Terms

Common PAL-block resource

Individual macrocell resources

From Logic Allocator

From

PAL-Clock

Generator

Block CLK0

Block CLK1

Block CLK2

Block CLK3

SWAP

AP AR

D/T/L Q

a. Synchronous mode

To Output and Input

Switch Matrices

17466G-009

Individual

Initialization

Product Term

Power-Up

Reset

SWAP

From Logic

Allocator

From PAL-Block

Clock Generator

Individual Clock

Product Term

Block CLK0

Block CLK1

AP AR

D/T/L Q

b. Asynchronous mode

Figure 5. Macrocell

To Output and Input

Switch Matrices

17466G-010

In either mode, a combinatorial path can be used. For combinatorial logic, the synchronous mode will

generally be used, since it provides more product terms in the allocator.

10

ispMACH 4A Family