HMP8154 View Datasheet(PDF) - Intersil

Part Name

Description

Manufacturer

HMP8154 Datasheet PDF : 34 Pages

| |||

HMP8154, HMP8156A

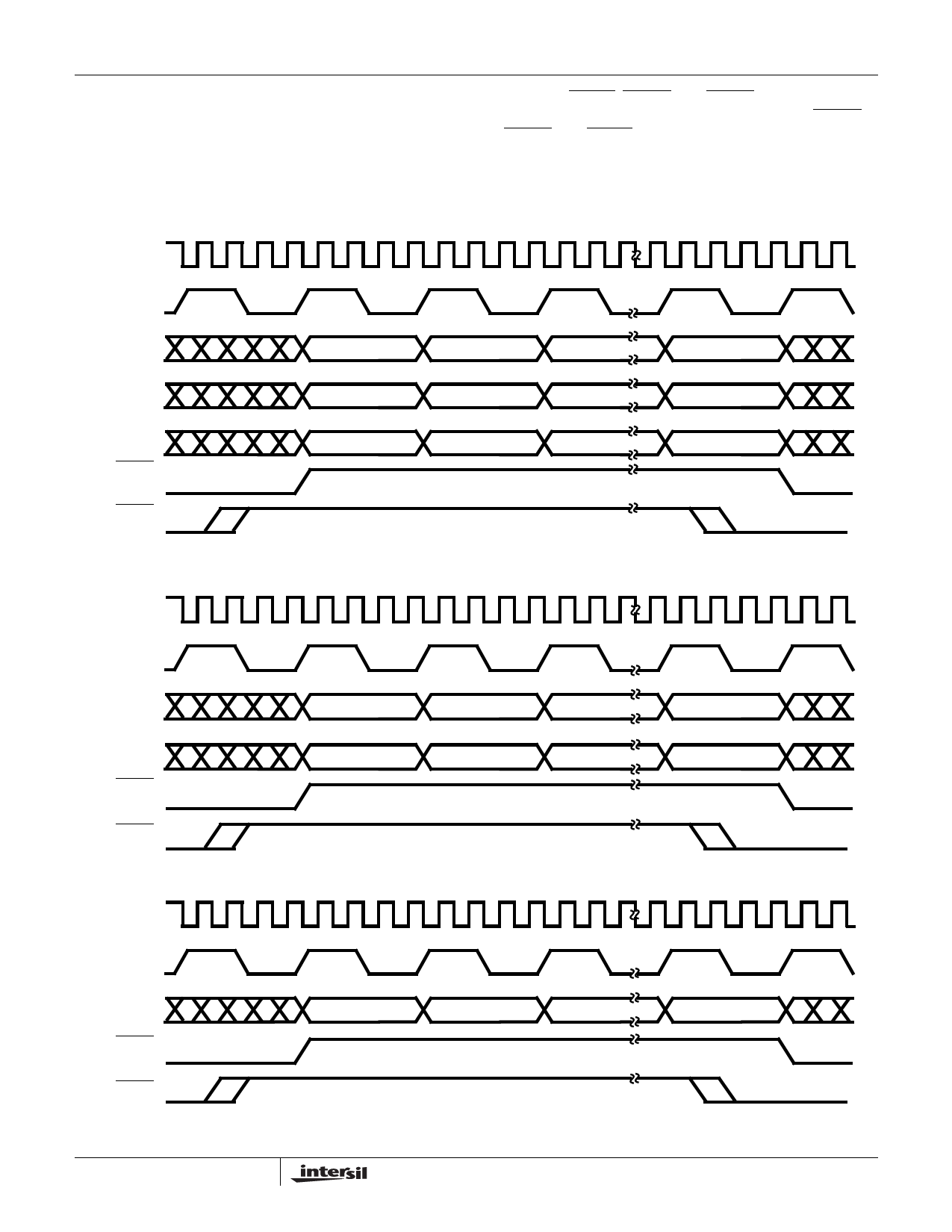

16-Bit YCbCr, 16-Bit RGB, 24-Bit RGB Formats

with 2X Upscaling

When 16-bit YCbCr, 16-bit RGB data, or 24-bit RGB format

is selected and 2X upscaling is enabled, data is latched on

the rising edge of CLK2 while CLK is low. Overlay data is

latched on the rising edge of CLK2 while CLK is low. The

pixel and overlay input timing is shown in Figures 6-8.

As inputs, BLANK, HSYNC, and VSYNC are latched on the

rising edge of CLK2 while CLK is low. As outputs, HSYNC,

VSYNC, and BLANK are output following the rising edge of

CLK2 while CLK is high. CLK is one-fourth the CLK2

frequency.

CLK2

CLK

P8-P15

P0-P7

OL0-OL2,

M1, M0

BLANK

(INPUT)

BLANK

(OUTPUT)

Y0

Cb 0

PIXEL 0

Y1

Cr 0

PIXEL 1

YN

Cr N-1

PIXEL N

FIGURE 6. PIXEL AND OVERLAY INPUT TIMING - 16-BIT YCBCR WITH 2X UPSAMPLING

CLK2

CLK

P0-P15

OL0-OL2,

M1, M0

BLANK

(INPUT)

BLANK

(OUTPUT)

CLK2

CLK

P0-P24

BLANK

(INPUT)

BLANK

(OUTPUT)

RGB 0

PIXEL 0

RGB 1

PIXEL 1

RGB N

PIXEL N

FIGURE 7. PIXEL AND OVERLAY INPUT TIMING - 16-BIT RGB WITH 2X UPSAMPLING

RGB 0

RGB 1

RGB N

FIGURE 8. PIXEL AND OVERLAY INPUT TIMING - 24-BIT RGB WITH 2X UPSAMPLING

9

4343.4

November 4, 2005