ADM1021AARQ View Datasheet(PDF) - Analog Devices

Part Name

Description

Manufacturer

ADM1021AARQ Datasheet PDF : 16 Pages

| |||

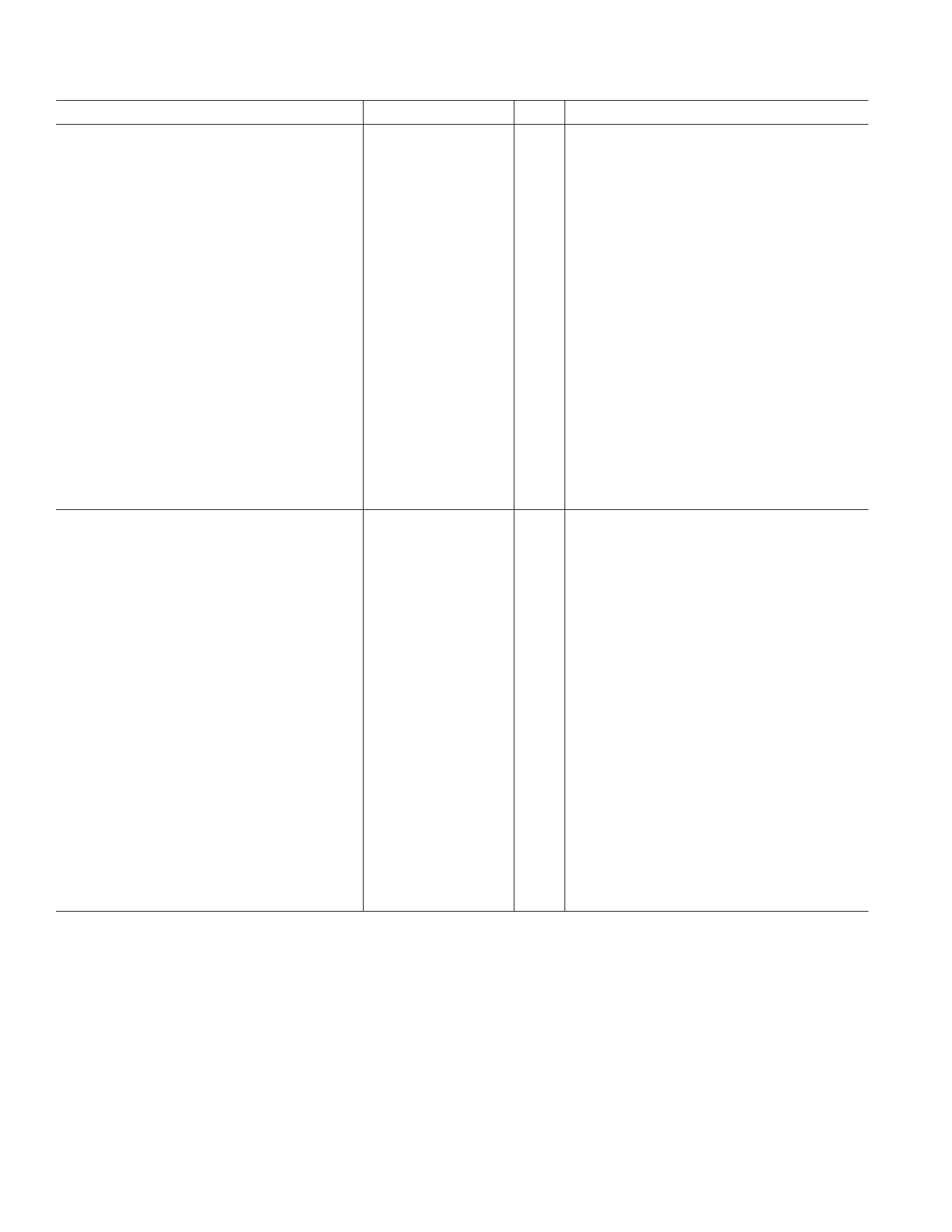

ADM1021A–SPECIFICATIONS (TA = TMIN to TMAX1, VDD = 3.0 V to 3.6 V, unless otherwise noted.)

Parameter

Min Typ Max Unit Test Conditions/Comments

POWER SUPPLY AND ADC

Temperature Resolution

Temperature Error, Local Sensor

Temperature Error, Remote Sensor

Supply Voltage Range

Undervoltage Lockout Threshold

Undervoltage Lockout Hysteresis

Power-On Reset Threshold

POR Threshold Hysteresis

Standby Supply Current

Average Operating Supply Current

Autoconvert Mode, Averaged Over 4 Seconds

Conversion Time

Remote Sensor Source Current

D-Source Voltage

Address Pin Bias Current (ADD0, ADD1)

1

°C

±1

°C

–3

+3 °C

–3

+3 °C

–5

+5 °C

3

3.6 V

2.5 2.7 2.95 V

25

mV

0.9 1.7 2.2 V

50

mV

15

µA

4

µA

130 200 µA

225 330 µA

65 115 170 ms

120 205 300 µA

7

12 16 µA

0.7

V

50

µA

Guaranteed No Missed Codes

TA = 60°C to 100°C

Note 2

VDD Input, Disables ADC, Rising Edge

VDD, Falling Edge3

VDD = 3.3 V, No SMBus Activity

SCLK at 10 kHz

0.25 Conversions/Sec Rate

2 Conversions/Sec Rate

From Stop Bit to Conversion Complete

(Both Channels)

D+ Forced to D– + 0.65 V

High Level3

Low Level3

Momentary at Power-On Reset

SMBUS INTERFACE

Logic Input High Voltage, VIH

STBY, SCLK, SDATA

Logic Input Low Voltage, VIL

STBY, SCLK, SDATA

SMBus Output Low Sink Current

ALERT Output Low Sink Current

Logic Input Current, IIH, IIL

SMBus Input Capacitance, SCLK, SDATA

SMBus Clock Frequency

SMBus Clock Low Time, tLOW

SMBus Clock High Time, tHIGH

SMBus Start Condition Setup Time, tSU:STA

SMBus Repeat Start Condition

Setup Time, tSU:STA

SMBus Start Condition Hold Time, tHD:STA

SMBus Stop Condition Setup Time, tSU:STO

SMBus Data Valid to SCLK

Rising Edge Time, tSU:DAT

SMBus Data Hold Time, tHD:DAT

SMBus Bus Free Time, tBUF

SCLK Falling Edge to SDATA

Valid Time, tVD, DAT

2.2

6

1

–1

5

4.7

4

4.7

250

4

4

250

0

4.7

NOTES

1TMAX = 100°C; TMIN = 0°C.

2Operation at VDD = 5 V guaranteed by design, not production tested.

3Guaranteed by design, not production tested.

Specifications subject to change without notice.

V

0.8 V

mA

mA

+1 µA

pF

100 kHz

µs

µs

µs

ns

µs

µs

ns

µs

µs

1

µs

VDD = 3 V to 5.5 V

VDD = 3 V to 5.5 V

SDATA Forced to 0.6 V

ALERT Forced to 0.4 V

tLOW between 10% Points

tHIGH between 90% Points

Between 90% and 90% Points

Time from 10% of SDATA to 90% of SCLK

Time from 90% of SCLK to 10% of SDATA

Time from 10% or 90% of SDATA to 10%

of SCLK

Between Start/Stop Conditions

Master Clocking in Data

–2–

REV. D