GL652USB View Datasheet(PDF) - Genesys Logic

Part Name

Description

Manufacturer

GL652USB Datasheet PDF : 17 Pages

| |||

GL652USB 7 PORT USB HUB CONTROLLER

After filling the data-to-transmit into FF0, the micro-controller should setup this register to

enable endpoint 0 data transmit. If EP0OE = 0, endpoint 0 will respond to a valid IN transaction

with a NAK. EP0OE will be automatically cleared after a successful transmission, or when

endpoint 0 has incidentally accepted another SETUP or OUT transaction.

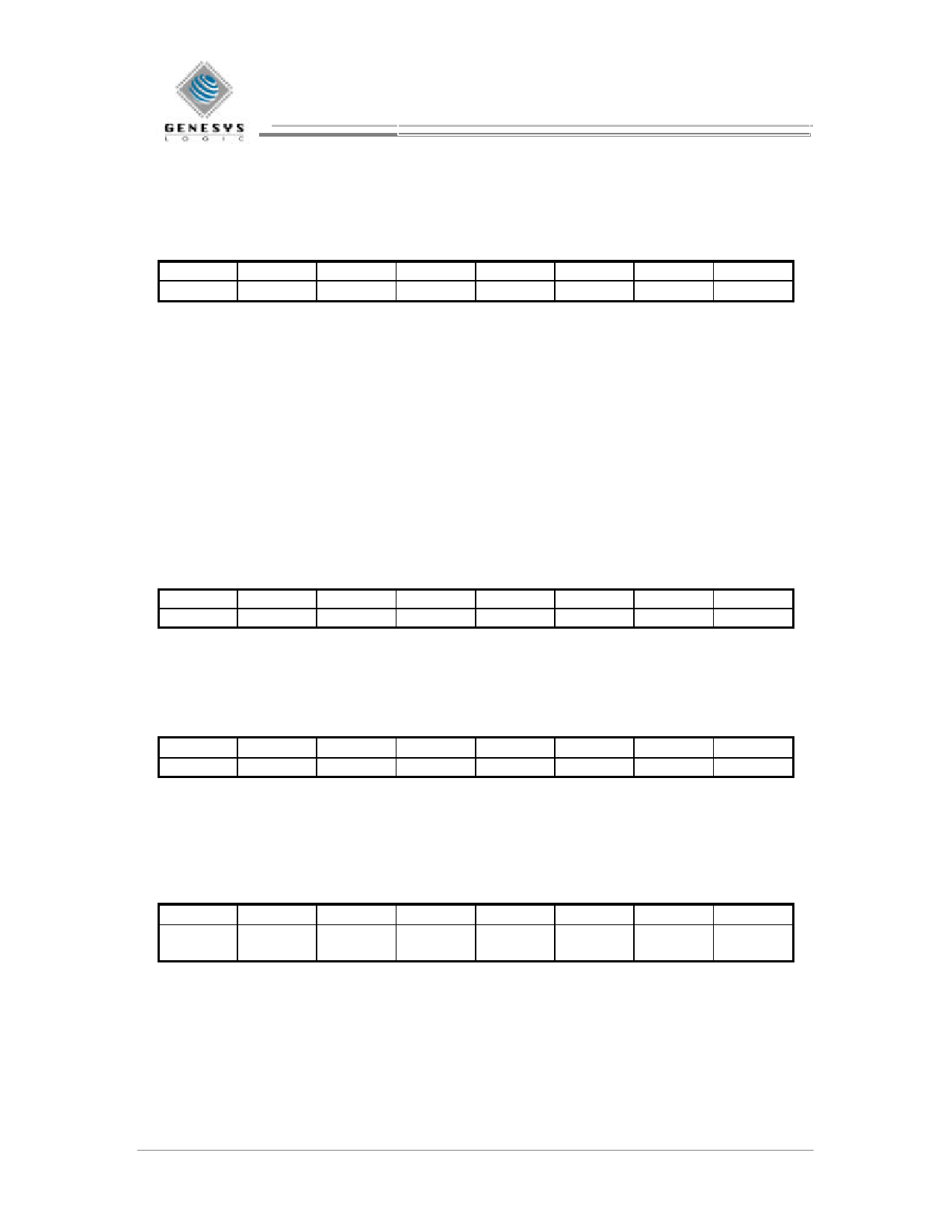

TXCTL1

( offset 04, default = 00h )

R/W

R/W

R/W

R/O

R/O

R/O

R/W

--

EP1STL EP1OE EP1SEQ EP1CNT3 EP1CNT2 EP1CNT1 EP1CNT0

Endpoint 1 transmit setting –

EP1CNT3~0

: number of data bytes to transmit. EP1CNT3~1 are always ‘0’.

EP1OE

: enable data transmit

EP1SEQ

1 – ready to transmit data packet

0 – not ready to transmit data packet (default)

: data packet type

EP1STL

0 –DATA0

1 –DATA1

: set endpoint 1 stall

1 – EP1 will respond to USB host controller with STALL packet

0 – default

After preparing the data to transmit, the micro-controller should setup this register to enable

endpoint 1 data transmit. If EP1OE = 0, endpoint 1 will respond to a valid IN transaction with a

NAK. After a successful transmission, the device will automatically clear EP1OE.

FFDAT

( offset 05, default = 00h )

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

FFD7

FFD6

FFD5

FFD4

FFD3

FFD2

FFD1

FFD0

If FFSEL1 (in BUFCTL) = 1’b0, this is FF0 access-window; if FFSEL1 = 1’b1, this is FF1

access-window. Each FFDAT read/write will automatically increase the FIFO pointer, which is

a 3-bit circular counter, by 1. Writing FPRST with ‘1’ (in BUFCTL) will reset the pointer. Note

that to fill FF0, RXDIS (in RXCTL0) must be first cleared.

BUFCTL

( offset 06 )

W/O

--

--

--

--

--

FPRST

Data buffer control –

FFSEL1

: FIFO 0/1 selector

1’b0 – select endpoint 0 data buffer

1’b1 – select endpoint 1 data buffer

FPRST

: reset FIFO 0/1 pointer (write only)

R/W

--

FFSEL1

PORTSEL

--

( offset 07, default = 00h )

R/W

R/W

R/W

R/W

R/W

PORTSEL PORTSEL PORTSEL PORTSEL PORTSEL

7

6

5

4

3

PORTSEL

: PORT 1~7 under request

PORTSEL1

PORTSEL2

PORTSEL3

PORTSEL4

1’b1 – port 1 selected

1’b1 – port 2 selected

1’b1 – port 3 selected

1’b1 – port 4 selected

PORTSEL5

PORTSEL6

PORTSEL7

1’b1 – port 4 selected

1’b1 – port 4 selected

1’b1 – port 4 selected

R/W

PORTSEL

2

R/W

PORTSEL

1

8

08/18/00

Revision 1.2