SSD1811 View Datasheet(PDF) - Solomon Systech

Part Name

Description

Manufacturer

SSD1811 Datasheet PDF : 40 Pages

| |||

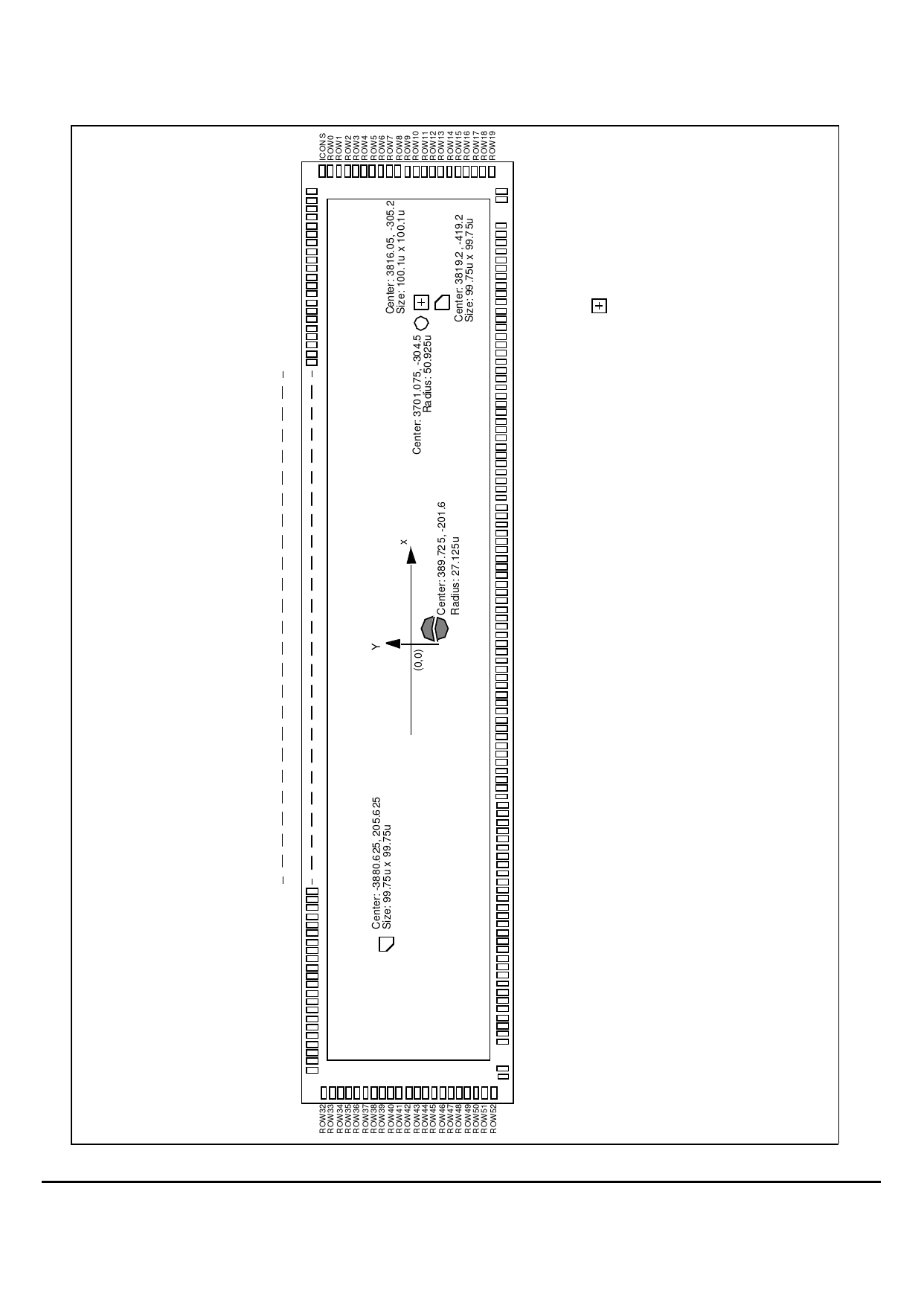

PIN ARRANGEMENT

SEG0

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG11

SEG12

SEG13

SEG14

SEG15

SEG16

SEG17

SEG18

SEG19

SEG20

137

SEG110

SEG111

SEG112

SEG113

SEG114

SEG115

SEG116

SEG117

SEG118

SEG119

SEG120

SEG121

SEG122

SEG123

SEG124

SEG125

SEG126

SEG127

SEG128

SEG129

SEG130

SEG131

268

115

:

:

:

:

1

ROW20

ROW21

:

:

ROW30

ROW31

VDD

IRS

VSS

/HPM

VDD

P/S

C68/80

VSS

CLS

M/S

VDD

NC

NC

VDD

VDD

VF

VF

VL6

VL6

VL6

VL5

VL5

VL4

VL4

VL4

VL3

VL3

VL3

VL2

VL2

VDD

VDD

VFS

VFS

VSS

VSS

C2P

C2P

C2P

C2N

C2N

C2N

C2N

C1N

C1N

C1N

C1P

C1P

C1P

C3N

C3N

C3N

C3N

VEE

VEE

VEE

VEE

VSS1

VSS1

VSS1

VSS1

VSS

VSS

VSS

VDD

VDD

VDD

VDD

D7 (SDA)

D6 (SCK)

D5

D4

D3

D2

D1

D0

VDD

E(/RD)

R/W(/WR)

VSS

D/C

/RES

VDD

CS2

/CS1

VSS

/DOF

CL

M

MSTAT

NC

ICONS

ROW63

ROW62

ROW61

:

:

ROW54

ROW53

Gold Bump Alignment Mark

This alignment mark contains gold bump for IC

bumping process alignment and IC identifica-

tions. No conductive tracks should be laid under-

neath this mark to avoid short circuit.

Note:

1. This diagram showing Die Face Up view.

2. Coordinates and Size of all alignment marks

are in unit um and w.r.t. center of the chip.

Die Size:

Die Thickness:

Bump Pitch:

Bump Height:

10.977mm X 1.912mm

533 +/-25um

76.2 um [Min]

Nominal 18um

Tolerance <4um within die

<8um within lot

PIN #1

SSD181X Series

5

Figure 2 SSD181X Series Gold Bump Die Pin Assignment

Rev 3.1

08/2001

SOLOMON